Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors (Code Name: Elkhart Lake)

**Get Started Guide**

September 2022

Maintenance Release 2 (MR2) – Kernel 5.4 Maintenance Release 3 (MR3) – Kernel 5.15 Maintenance Release 5 (MR5) – Kernel 5.15

You may not use or facilitate the use of this document any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visit www.intel.com/design/literature.htm.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No product or component can be absolutely secure. Check with your system manufacturer or retailer or learn more at intel.com.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

### Contents

| 1.0 |     | Introduction                                               | 6  |

|-----|-----|------------------------------------------------------------|----|

|     | 1.1 | Terminology                                                | 6  |

|     | 1.2 | Intended Audience                                          | 7  |

|     | 1.3 | Customer Support                                           | 7  |

|     | 1.4 | Reference Documents                                        | 8  |

| 2.0 |     | Prepare and Set Up the Host System                         | 10 |

|     | 2.1 | Setting up the Host System for the First Time              | 10 |

|     |     | 2.1.1 Prerequisite for the Host System                     |    |

|     |     | 2.1.2 Host System Preparation and Installation             | 10 |

|     | 2.2 | Install Additional Dependencies                            | 11 |

|     |     | 2.2.1 Install the Required Toolchain                       |    |

|     |     | 2.2.2 Install the Required GCC Version                     | 11 |

| 3.0 |     | Getting Started with the BSP                               |    |

|     | 3.1 | Getting Started with Kernel 5.4 BSP Release (MR2)          | 12 |

|     |     | 3.1.1 Obtain Repository Sources and Prepare to Build Image | 12 |

|     |     | 3.1.2 Adding Optional Components                           | 14 |

|     |     | 3.1.2.1 Integrate Software Tools or Packages               | 14 |

|     |     | 3.1.2.2 Integrate Proprietary Components                   | 15 |

|     |     | 3.1.2.3 Integrate Workarounds or Patches                   |    |

|     |     | 3.1.3 Build the Yocto Project*-based Image                 | 18 |

|     |     | 3.1.4 Subsequent Build of Image                            | 20 |

|     | 3.2 | Getting Started with Kernel 5.15 BSP Release (MR3)         | 21 |

|     |     | 3.2.1 Obtain Repository Sources and Prepare to Build Image | 21 |

|     |     | 3.2.2 Adding Optional Components                           | 24 |

|     |     | 3.2.2.1 Integrate Software Tools or Packages               | 24 |

|     |     | 3.2.2.2 Integrate Proprietary Components                   | 25 |

|     |     | 3.2.2.3 Integrate Workarounds or Patches                   |    |

|     |     | 3.2.3 Build the Yocto Project*-based Image                 |    |

|     |     | 3.2.4 Subsequent Build of Image                            |    |

|     | 3.3 | Getting Started with Kernel 5.15 BSP Release (MR5)         |    |

|     |     | 3.3.1 Obtain Repository Sources and Prepare to Build Image |    |

|     |     | 3.3.2 Adding Optional Components                           |    |

|     |     | 3.3.2.1 Integrate Software Tools or Packages               |    |

|     |     | 3.3.2.2 Integrate Proprietary Components                   |    |

|     |     | 3.3.2.3 Integrate Workarounds or Patches                   |    |

|     |     | 3.3.3 Build the Yocto Project*-based Image                 | 37 |

|     |     | 3.3.4 Subsequent Build of Image                            |    |

| 4.0 |     | Next Step to Boot Up CRB                                   | 41 |

|     | 4.1 | Prepare a Bootable Image with the USB Flash Drive          | 41 |

|     | 4.2 | Boot up Elkhart Lake CRB with USB Flash Drive              |    |

|     |     |                                                            |    |

|     | 4.3 | Boot with PREEMPT_RT Kernel                                                  | 43 |

|-----|-----|------------------------------------------------------------------------------|----|

|     | 4.4 | Install the Yocto Project*-Based Image into the Elkhart Lake CRB Local Drive |    |

|     |     | 4.4.1 First Time Image Installation into the CRB's Local Drive               |    |

|     |     | 4.4.2 Subsequent Image Installation into the CRB's Local Drive               | 45 |

|     | 4.5 | Next Steps for Intel® Time Coordinated Computing Tools (Intel® TCC Tools)    | 45 |

| 5.0 |     | Appendix                                                                     |    |

|     | 5.1 | Further References                                                           | 46 |

|     | 5.2 | i2s* Audio Settings and Configuration                                        | 47 |

|     |     | 5.2.1 BIOS Settings                                                          |    |

|     |     | 5.2.2 Integrate Firmware and Topology                                        | 47 |

|     | 5.3 | Kernel Configuration for Intel® Converged Security Engine (Intel® CSE)       |    |

|     | 5.4 | GPIO Control                                                                 |    |

|     |     | 5.4.1 BIOS Settings                                                          |    |

|     |     | 5.4.2 GPIO Control via sysfs Interface                                       |    |

|     |     | 5.4.3 GPIO Offset                                                            |    |

|     | 5.5 | Entering S0ix State via Opportunistic Idle                                   | 51 |

|     |     |                                                                              |    |

### **Figures**

| Figure 1. | Boot Menu43 |

|-----------|-------------|

|-----------|-------------|

### Tables

| Table 1. | Terminology         | 6 |

|----------|---------------------|---|

| Table 2. | Reference Documents | 8 |

### **Revision History**

| Date           | Revision | Description                                                                                                                                                             |

|----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| September 2022 | 6.0      | • Maintenance Release 5 (MR5) – Kernel 5.15                                                                                                                             |

| August 2022    | 5.1      | • Updated mandatory workaround for GNUlib error in Section 3.2.1                                                                                                        |

| July 2022      | 5.0      | • Maintenance Release 4 (MR4) – Kernel 5.15                                                                                                                             |

| April 2022     | 4.1      | <ul> <li>Updated mandatory workaround for Grub re-base URL issue in Section 3.2.1</li> <li>Updated mandatory patch to enable the Kernel Boot options in 5.15</li> </ul> |

|                |          | Bullpen RT SBL in Section 3.2.1                                                                                                                                         |

| March 2022     | 4.0      | • Maintenance Release 3 (MR3) – Kernel 5.15                                                                                                                             |

|                |          | • Updated Getting Started steps in Section 3.0 to contain both Kernel 5.4 (MR2) and Kernel 5.15 (MR3)                                                                   |

| March 2022     | 3.2      | Updated mandatory workaround in Section 3.1 for invalid source URL issue.                                                                                               |

| December 2021  | 3.1      | Hotfix - released a patch that resolved S4 issue. Updated Section 3.2.3 for the steps to integrate the patch.                                                           |

| November 2021  | 3.0      | MR2 Release.                                                                                                                                                            |

| August 2021    | 2.0      | MR1 Release.                                                                                                                                                            |

| June 2021      | 1.2      | • Updated Intel <sup>®</sup> TCC Tools link in Section 3.9.                                                                                                             |

|                |          | • Updated Intel Atom <sup>®</sup> x6000E Series Processors Real-Time Tuning Guide document Document# in Section 1.4.                                                    |

| March 2021     | 1.1      | Updated document title. Refer to Document #616424, Section 2.1 for supported silicon.                                                                                   |

| March 2021     | 1.0      | PV Release and added a Note on workaround for Intel® TCC Mode issue in Section 4.2.                                                                                     |

| February 2021  | 0.9      | Pre-production QS Release.                                                                                                                                              |

§

### 1.0 Introduction

This document provides instructions on how to build the Yocto Project\*-based board support package (BSP) for the Elkhart Lake customer reference board (CRB). This requires preparing and setting up a host system, steps in selecting the components and building a Yocto Project\*-based image, as well as preparing the bootable image with the USB flash drive to install to the CRB.

You are recommended to review the release information before proceeding with this *Get Started Guide*. For release information, notes, and reference, refer to the following documents:

- Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors (Kernel 5.4) - Release Notes (Document number: 616424) for MR2

- Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors (Kernel 5.15) - Release Notes (Document number: 723330) for MR3

- Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors (Kernel 5.15) - Release Notes (Document number: 732903) for MR5

- **Note:** The Yocto Project\*-based build system version and the corresponding open-source software components suggested for use with the BSP are only for reference purposes. If you decide to use Yocto Project\*, it is your responsibility to integrate the latest functional and/or security updates when they are available from the open-source community.

### 1.1 Terminology

#### Table 1. Terminology

| Term | Description                       |

|------|-----------------------------------|

| API  | Application Programming Interface |

| ATT  | Attribute Protocol                |

| BSP  | Board Support Package             |

| CAN  | Controller Area Network           |

| CRB  | Customer Reference Board          |

| DMA  | Direct Memory Access              |

| eMMC | Embedded Multi-Media Card         |

| Term                   | Description                               |

|------------------------|-------------------------------------------|

| GbE                    | Gigabit Ethernet                          |

| GCC                    | GNU Compiler Collection                   |

| HDCP                   | High-bandwidth Digital Content Protection |

| HECI                   | Host Embedded Controller Interface        |

| IBECC                  | In-Band Error Checking and Correction     |

| IFWI                   | Integrated Firmware Image                 |

| Intel <sup>®</sup> CSE | Intel® Converged Security Engine          |

| Intel <sup>®</sup> PSE | Intel® Programmable Services Engine       |

| Intel <sup>®</sup> TCC | Intel® Time Coordinated Computing         |

| LTS                    | Long-Term Support                         |

| PXE                    | Pre-Boot eXecution Environment            |

| RPMB                   | Replay Protected Memory Blob              |

| SCSI                   | Small Computer System Interface           |

| SOF                    | Sound Open Firmware                       |

| TSN                    | Time-Sensitive Networking                 |

| USB                    | Universal Serial Bus                      |

### **1.2** Intended Audience

This document is for users of the Yocto Project\*-based BSP for the Intel Atom® x6000E series, and Intel® Pentium® and Celeron® N and J Series processor CRBs.

#### 1.3 Customer Support

Contact your Intel representative for support or submit an issue to premiersupport.intel.com.

### **1.4 Reference Documents**

#### Table 2. Reference Documents

| Document                                                                                                                                                                                             | Document<br>Number/Location |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Intel® Media SDK for the Embedded Linux* OS on the Elkhart Lake<br>Platform                                                                                                                          | 616493                      |

| Ethernet Time-Sensitive Networking for Elkhart Lake/Tiger Lake UP3 -<br>Getting Started Guide                                                                                                        | 616446                      |

| Intel® PSE SDK Developer Guide                                                                                                                                                                       | 611877                      |

| Intel® PSE SDK API Guide                                                                                                                                                                             | 611876                      |

| Intel® Programmable Services Engine (Intel® PSE) SDK User Guide                                                                                                                                      | 611827                      |

| How to Video: Host System Build Environment Setup                                                                                                                                                    | 608732                      |

| Intel® PSE SDK Get Started Guide                                                                                                                                                                     | 608527                      |

| Host System Build Environment Setup Guide                                                                                                                                                            | 334828                      |

| Wireless Connectivity Product for Yocto Project User Guide                                                                                                                                           | 617199                      |

| ECMA-393 Network Proxy Technology Support Using Linux* User Space<br>Library (Elkhart Lake)                                                                                                          | 613398                      |

| Intel Atom <sup>®</sup> x6000E Series Processors Real-Time Tuning Guide                                                                                                                              | 640979                      |

| Cache Reservation Library (CRL) Integration for Intel® Platforms to<br>Enable Intel® Time Coordinated Computing (Intel® TCC)                                                                         | 660902                      |

| Programming Elkhart Lake MAC Addresses Using Capsule Update                                                                                                                                          | 620481                      |

| Intel® In-Band Manageability Framework x86 2.7.5.1                                                                                                                                                   | 630741                      |

| Yocto Project*-based Board Support Package for Intel Atom® x6000E<br>Series, and Intel® Pentium® and Celeron® N and J Series Processors<br>(Code Name: Elkhart Lake) (Kernel 5.4) MR2 Release Notes  | 616424                      |

| Generate Key for Secure Boot with the Yocto Project*-based Image and Bootloader/UEFI BIOS                                                                                                            | 633630                      |

| Pre-boot Execution Environment (PXE) Boot with Intel Atom® x6000E<br>Series, and Intel® Pentium® and Celeron® N and J Series Processors<br>(Code Name: Elkhart Lake) - Application Notes             | 635874                      |

| Yocto Project*-based Board Support Package for Intel Atom® x6000E<br>Series, and Intel® Pentium® and Celeron® N and J Series Processors<br>(Code Name: Elkhart Lake) (Kernel 5.15) MR3 Release Notes | 723330                      |

| Document                                                                                                                                                                                             | Document<br>Number/Location |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Intel® Media SDK for the Embedded Linux* OS on the Elkhart Lake<br>Platform                                                                                                                          | 616493                      |

| Ethernet Time-Sensitive Networking for Elkhart Lake/Tiger Lake UP3 -<br>Getting Started Guide                                                                                                        | 616446                      |

| Yocto Project*-based Board Support Package for Intel Atom® x6000E<br>Series, and Intel® Pentium® and Celeron® N and J Series Processors<br>(Code Name: Elkhart Lake) (Kernel 5.15) MR5 Release Notes | 732903                      |

*Note:* To download or search for a specific document, type the document number on the search bar in the Intel website.

§

### 2.0 Prepare and Set Up the Host System

This chapter describes the steps to prepare and set up the host system to build the Yocto Project\*-based image that will be used to boot up the Elkhart Lake board. The preparation and setup only need to be done for the first time.

### 2.1 Setting up the Host System for the First Time

#### 2.1.1 Prerequisite for the Host System

The following list provides the minimum host system configuration to build the BSP for the Yocto Project\*. For Elkhart Lake, this configuration supersedes the other prerequisite that may be listed in the *Host System Build Environment Setup Guide* (Document number: 334828).

- Intel<sup>®</sup> Core<sup>™</sup> i7 processor (4 cores)

- Linux\* OS of choice for the Yocto Project\* build is Ubuntu\* 18.04 LTS OS or higher (Refer to the Yocto Project\* Quick Start for more information.)

- A minimum of 32 GB RAM and 500 GB disk space are recommended

- High-speed network connectivity

- USB flash drive 64 GB minimum (to prepare the bootable Yocto Project\*-based image)

#### 2.1.2 Host System Preparation and Installation

Follow the Host System Build Environment Setup Guide (Document number: 334828) and How-to Video: Host System Build Environment Setup (Document number: 608732) to prepare the host system to build the Yocto Project\*-based image.

After that, proceed to the next section to install additional dependencies in the host system.

#### 2.2 Install Additional Dependencies

Install the following dependencies for this project.

#### 2.2.1 Install the Required Toolchain

1. Install the required toolchain if it is not available in your host machine:

```

$ sudo apt-get -y install socat gawk wget git-core diffstat

unzip texinfo build-essential chrpath libsdl1.2-dev xterm

libncurses5-dev patchutils curl libelf-dev elfutils

```

2. Download and install the git-lfs in the host machine:

```

$ curl -s

https://packagecloud.io/install/repositories/github/git-

lfs/script.deb.sh | sudo -E bash

```

```

$ sudo apt-get install git-lfs

```

#### 2.2.2 Install the Required GCC Version

1. Check the current GCC version in your host machine:

```

$ gcc --version

$ g++ --version

# If your gcc version is not 7.3 or 8.2 and above, proceed to

the next steps

```

#### 2. Install the required GCC version.

```

# Add ppa repository

$ sudo add-apt-repository ppa:ubuntu-toolchain-r/test

# If you are not able to add the ppa

```

```

$ sudo apt-get install --reinstall ca-certificates

$ sudo -E add-apt-repository ppa:ppaname/ppa

```

# Update and install gcc to take effect

\$ sudo apt-get update

\$ sudo apt-get install gcc-8 g++-8

```

# Alternatively update and configure gcc

$ sudo update-alternatives --install /usr/bin/gcc gcc

/usr/bin/gcc-8 60 --slave /usr/bin/g++ g++ /usr/bin/g++-8

```

```

# To select which GCC to use. Select with gcc8 or the latest

gcc you have installed as prompted

$ sudo update-alternatives --config gcc

```

#### §

### 3.0 Getting Started with the BSP

This section consists of 3 major sub-sections for different releases and kernels:

- Getting Started with Kernel 5.4 BSP Release (MR2)

- Getting Started with Kernel 5.15 BSP Release (MR3)

- Getting Started with Kernel 5.15 BSP Release (MR5), which is the latest release

Intel recommends migrating to the latest Board Support Package (BSP) for more fixes and features.

**Note:** Regularly check on available updates for the Ubuntu\* build system that you set up from Section 2.0. This is to make sure that all toolchains are up to date. Build steps in this section were performed based on **Python = 2.7.17** and **Python3 = 3.6.9** in the Ubuntu build machine. Intel recommends using this version or newer for this release. For information on how to switch or update Python version, refer to the appendix for more information.

#### 3.1 Getting Started with Kernel 5.4 BSP Release (MR2)

Refer to the Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors Release Notes (Document number: 616424) for further information on BSP Release.

#### 3.1.1 Obtain Repository Sources and Prepare to Build Image

This section describes the essential steps to obtain the BSP source and getting the system ready to build Yocto Project\*-based image. This section is compulsory, and any missing step might cause the build to fail.

1. Create a bin/ directory in your home directory and include your path:

```

$ mkdir ~/bin

$ PATH=~/bin:$PATH

```

2. Get the repo source and make it executable:

```

$ curl https://storage.googleapis.com/git-repo-downloads/repo

> ~/bin/repo

```

- \$ chmod a+x ~/bin/repo

- 3. Make a new directory:

```

$ mkdir <work_dir>

$ cd <work dir>

```

4. Git clone the repo manifest. This manifest will help you to clone all required repositories to create the base BSP:

```

$ repo init -u https://github.com/intel/iotg-yocto-ese-

manifest.git -b refs/tags/release-79 ehl-mr2 -g all

```

5. Pull the repository meta-layers (-j8 for simultaneous downloads, increase/decrease per your needs):

```

$ repo sync -c -j8 --force-sync

```

6. Make a branch:

\$ repo forall managed/\* -c git branch -f BUILD HEAD

7. The Yocto Project\*-based image supports both secure and non-secure booting options. In either case, security keys must be generated and integrated into the image; otherwise, the build may fail. Choose one of the following options to generate the keys:

#### Option 1 (Default):

Security keys will be generated randomly in this option and it is the default configuration. If randomly generated security keys are not affecting your application, no action is required in this step. You can proceed to the next step.

#### Option 2:

You need to generate your own security keys and place them in the 'cert' folder in the *<work\_dir>/build* folder of the build. For steps on how to use a common command-line tool (OpenSSL\*) to generate the keys required for the secure boot, including how to create the Keys and Certificates, place the created keys in the correct folder. Then install the keys into the UEFI BIOS. See *Generate Key for Secure Boot with the Yocto Project\*-based Image and Slim Bootloader/UEFI BIOS*, (Document number: 633630).

- *Note:* To use Slim Bootloader or secure boot with UEFI BIOS, you must choose *Option 2*. Make sure the same keys are used for the Yocto Project\*-based image and Slim Bootloader/UEFI BIOS.

- 8. Apply this workaround for invalid source URL issue by following the steps:

#### Step 1: Edit *linux-firmware\_git.bb* file

```

$ vi <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-iot-bsp/recipes-

kernel/linux-firmware/linux-firmware_git.bb

```

#### Step 2: Search and modify the following line

```

#Find the following line

```

#### Getting Started with the BSP

## intel.

```

SRC_URI =

"git://git.kernel.org/pub/scm/linux/kernel/git/firmware/linux-

firmware.git"

#Modify to the following line

SRC_URI =

"git://git.kernel.org/pub/scm/linux/kernel/git/firmware/linux-

firmware.git;protocol=https;branch=main"

#save and exit

```

#### 3.1.2 Adding Optional Components

This section describes the steps required to integrate Software Tools/Packages, Proprietary Components, and workarounds to the build. For more information about software tools or packages, refer to Section 5.1. For more information about proprietary components and workarounds, see Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors (Code Name: Elkhart Lake) Release Notes (Document number: 616424).

*Note:* Since the components are optional, the build will not fail if you choose to skip this section. You can still add the components in the future and re-build the image.

#### 3.1.2.1 Integrate Software Tools or Packages

1. This step integrates the bmaptool and/ or devmem2 into the Yocto Project\*-based image. The bmap-tools is needed if you need to install the image from one storage to another storage on the Elkhart Lake CRB (refer to Section 4.4 for steps to install from one storage to another). Devmem2 is needed if you need to test the IBECC feature. Otherwise, you may skip this step.

```

$ cd <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-distro/conf/include

$ vi ese-x86-common.inc

#add the following lines

IMAGE_INSTALL:append = " bmap-tools"

IMAGE_INSTALL:append = " devmem2"

```

2. **[Required for TSN]** This step integrates the TSN Reference Software into the image. TSN Reference Software is needed if you want to explore the TSN technology in your application. Otherwise, you may skip this step. For more information about TSN, refer to Section 3.6 of the *Yocto Project\*-based BSP Release Notes* (Document number: 616424).

```

$ vi <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-distro/conf/include/ese-

x86-common.inc

```

```

# Add the following lines

IMAGE INSTALL:append = " iotg-tsn-ref-sw"

```

#### 3.1.2.2 Integrate Proprietary Components

This section provides the steps to integrate proprietary components into the Yocto Project\*-based image. It is considered as an optional section as you may skip this section if none of the proprietary components is applicable to your interest. You may choose to integrate one or more components. For more information on the proprietary components, refer to the Yocto Project\*-based Board Support Package for Intel Atom<sup>®</sup> x6000E Series, and Intel<sup>®</sup> Pentium<sup>®</sup> and Celeron<sup>®</sup> N and J Series Processors (Code Name: Elkhart Lake) Release Notes (Document number: 616424).

Two files from Section 2.2 of the *Yocto Project-based BSP Release Notes* (Document number: 616424) are relevant in this section:

- a. yocto\_project\_mr2\_release.zip (ID# 621477)

The zip file consists of recipes and binaries for wireless (meta-intelwireless.zip) and Network Proxy Application (meta-libnetprox.tar.bz2).

- b. meta-ptcm.tar.gz (ID# 646606) The tarball contains the Real-Time Configuration Manager that required for Intel<sup>®</sup> Time Coordinated Computing Tools (Intel<sup>®</sup> TCC Tools).

Follow the instructions below if you choose to integrate the propriety components.

1. Create a new folder (for example: proprietary) in the working directory and unzip the yocto\_project\_mr2\_release.zip into the proprietary folder.

```

$ mkdir <work_dir>/proprietary

$ unzip yocto_project_mr2_release.zip

```

As a result of unzipping, multiple tarballs will be available in the proprietary folder. Untar the tarballs that you would like to integrate in the next steps. Replace <file\_name> with the tarball file name.

```

$ tar -xvf <file_name>.tar.gz

OR

$ tar -xvf <file name>.tar.bz2

```

2. Change the directory to the conf folder where local.conf and bblayers.conf are located.

```

$ cd <work dir>/build/conf

```

3. Integrate components of the Wi-Fi\* and Bluetooth® technology in the BSP

```

$ vi bblayers.conf

```

```

# Add the following lines

```

```

${TOPDIR}/../proprietary/meta-intel-wireless \

```

4. [Required for Intel<sup>®</sup> Time Coordinated Computing Tools (Intel<sup>®</sup> TCC Tools)] To integrate the real-time configuration manager (RTCM) by updating the following files:

```

$ vi bblayers.conf

# Add the following lines

{TOPDIR}/../proprietary/meta-ptcm \

```

\$ vi <work\_dir>/intel-embedded-system-enabling/meta-intelembedded-system-enabling/meta-intel-distro/conf/include/esex86-common.inc

```

# Add the following lines

IMAGE_INSTALL_append = " ptcm"

PTCM_INSTALL = "1"

```

- 5. To integrate the ECMA-393 network proxy technology in the BSP:

- a. Edit bblayers.conf and local.conf.

```

$ vi bblayers.conf

# Add the following lines

$ {TOPDIR}/../proprietary/meta-libnetprox \

```

\$ vi <work\_dir>/intel-embedded-system-enabling/meta-intelembedded-system-enabling/meta-inteldistro/conf/include/ese-x86-common.inc

# Add the following lines and change the path to where you have placed the binaries. IMAGE INSTALL:append = " libnetprox"

b. Update networkproxy.cfg ONLY if you need to change port. The config file is set for PSE GbE0 by default. If you need to use PSE GbE1, follow the path below:

\$ vi <work\_dir>/intel-embedded-system-enabling/meta-intelembedded-system-enabling/meta-intel-iot-bsp/recipeskernel/linux/linux-config/bsp/networkproxy.cfg

```

# change from "CONFIG_STMMAC_NETWORK_PROXY_PORT=0" to

"CONFIG_STMMAC_NETWORK_PROXY_PORT=1"

```

c. Edit the lts 5.4 kernel configuration file for updating the network proxy configurations:

#vi <work\_dir>/intel-embedded-system-enabling/meta-intelembedded-system-enabling/meta-intel-iot-bsp/recipeskernel/linux/linux-intel-ese-lts-5.4\_git.bb Append this line at the end of the file: SRC\_URI\_append = " file://bsp/networkproxy.scc"

d. Clean the kernel.

bitbake -c cleansstate mc:x86:linux-intel-ese-lts-5.4

#### 3.1.2.3 Integrate Workarounds or Patches

Integrate the patch for S4 issue - ID: 15010225801 (refer to Section 3.1.5 of the Yocto Project\*-based BSP Release Notes, Document number: 616424) by following the steps below:

Step 1: Download the patch from the below link and rename.

```

$ wget -0 0001-hid-intel-ish-hid-Use-different-pm-callbacks-

for-ish.patch https://github.com/intel/linux-intel-

lts/commit/93b630f89c8d94187fd181ae4cbca13b4b47201c.patch

```

#### Step 2: Put the patch file under the following directory:

\$ mv 0001-hid-intel-ish-hid-Use-different-pm-callbacks-forish.patch <work\_dir>/intel-embedded-system-enabling/metaintel-embedded-system-enabling/meta-intel-iot-bsp/recipeskernel/linux/files

#### Step 3: Edit both .bb files below:

\$ vi <work\_dir>/intel-embedded-system-enabling/meta-intelembedded-system-enabling/meta-intel-iot-bsp/recipeskernel/linux/linux-intel-ese-lts-5.4 git.bb

#### #add this line

```

SRC_URI:append = " file://0001-hid-intel-ish-hid-Use-

different-pm-callbacks-for-ish.patch"

```

```

$ vi <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-iot-bsp/recipes-

kernel/linux/linux-intel-ese-lts-rt-5.4 git.bb

```

#add this line

```

SRC_URI:append = " file://0001-hid-intel-ish-hid-Use-

different-pm-callbacks-for-ish.patch"

```

#save and exit

2. **[Workaround]** This step includes the workaround for the known issue in ASPM (Active State Power Management). Follow the steps if the feature is required in your application. Otherwise, you can skip.

Refer to workaround ID: 1508932757 from Section 3.1.6 Workarounds of the Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors (Kernel 5.15) Release Notes (Document number: 723330).

*Note:* This workaround is not applicable if Real-Time Performance is required.

\$ vi <work dir>/build/conf/multiconfig/x86-common.inc

# Add the following lines

APPEND append = " pcie aspm.policy=powersupersave"

#save and exit

#### 3.1.3 Build the Yocto Project\*-based Image

This section explains the steps required to start the build process. There are a few options to build different types of images:

*Note:* It is mandatory to choose Option B for Intel<sup>®</sup> Time Coordinated Computing Tools (Intel<sup>®</sup> TCC Tools)

**Option A:** Image boots with LTS kernel by default. This is a validated image with LTS Kernel as the default boot kernel, GUI, secureboot, partition layout (as required for manageability support) and other third-party software/ tools.

**Option B:** Image boots with real-time kernel by default. This is a validated image with RT kernel as the default boot kernel.

**Option C:** Minimal image with LTS kernel as default boot kernel. This is a non-validated image that contains the same kernel driver as the image in Option A but with minimal user space software (for example, without GUI) for boot up. Wi-Fi drivers are provided by the default kernel and not from iwlwifi-backports.

**Option D:** Netboot image with PXE boot. This is a non-validated image to demonstrate the PXE boot feature in this release. This image is not recommended to be used for other features testing.

Follow the steps below to build the image:

#### Option A: Full image with LTS Kernel as Default Boot Image

1. Start the build process:

```

$ cd <work_dir>/build

$ . ../intel-embedded-system-enabling/oe-init-build-env .

```

*Note:* The dot at the end of the above command is part of the command.

2. Run the bitbake compilation command

\$ bitbake mc:x86:core-image-sato-sdk

Location of Images: <work\_dir>/build/tmp-x86-glibc/deploy/images/intel-corei7-64/ Required Files: core-image-sato-sdk-intel-corei7-64--<date>.wic and core-imagesato-sdk-intel-corei7-64--<date>.wic.bmap

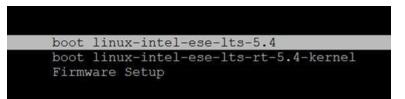

**Note:** The bitbake mc:x86:core-image-sato-sdk command will generate an image that boots up with the LTS Kernel by default and the real-time (RT) Kernel as the second option to be selected on the boot menu (refer to Section 4.3 for more details).

#### Option B: Full image with real-time (RT) kernel as the default boot image

1. Start the build process:

```

$ cd <work_dir>/build

$ . ../intel-embedded-system-enabling/oe-init-build-env .

```

Note: The dot at the end of the above command is part of the command

```

2. Run the bitbake compilation command.

$ bitbake mc:x86-rt:core-image-sato-sdk

```

**Location of Images**: <work\_dir>/build/tmp-x86-rt-glibc/deploy/images/intel-corei7-64/

**Required Files**: core-image-sato-sdk-intel-corei7-64--<date>.wic and core-image-sato-sdk-intel-corei7-64--<date>.wic.bmap

*Note:* The bitbake mc:x86-rt: core-image-sato-sdk command will generate an image that boots up with the real-time (RT) Kernel by default and the LTS Kernel as the second option.

#### Option C: Minimal image with LTS kernel as default boot image

```

1. Start the build process:

```

```

$ cd <work_dir>/build

$ . ../intel-embedded-system-enabling/oe-init-build-env .

```

Note: The dot at the end of the above command is part of the command

2. Run the bitbake compilation command

\$ bitbake mc:x86-minimal:core-image-full-cmdline

Location of Images: <work\_dir>/build/tmp-x86-minimal-glibc/deploy/images/intelcorei7-64/ Required Files: core-image-full-cmdline-intel-corei7-64--<date>.hddimg

#### **Option D: Netboot image with PXE boot**

- 1. Start the build process: \$ cd <work\_dir>/build \$ . ../intel-embedded-system-enabling/oe-init-build-env .

- Note: The dot at the end of the above command is part of the command

- 2. Run the bitbake compilation command

- \$ bitbake mc:x86-minimal-netboot:core-image-full-cmdline

Location of Images: <work\_dir>/build/tmp-x86-minimal-netbootglibc/deploy/images/intel-corei7-64/ Required File: core-image-full-cmdline-intel-corei7-64--<date>.rootfs.uefinetboot.tar.bz2

Refer to the PXE Boot Application Notes (Document number: 635874) for more details.

#### 3.1.4 Subsequent Build of Image

For subsequent rebuilding of the image, cleaning the kernel is recommended before executing bitbake compilation command.

#### For Option A:

bitbake -c cleansstate mc:x86:linux-intel-ese-lts-5.4 (To clean sstate of LTS kernel) bitbake -c cleansstate mc:x86:linux-intel-ese-lts-rt-5.4 (To clean sstate of RT kernel)

#### For Option B:

bitbake -c cleansstate mc:x86-rt:linux-intel-ese-lts-5.4 (To clean sstate of LTS Kernel) bitbake -c cleansstate mc:x86-rt:linux-intel-ese-lts-rt-5.4 (To clean sstate of RT kernel)

#### 3.2 Getting Started with Kernel 5.15 BSP Release (MR3)

Refer to the Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors (Kernel 5.15) Release Notes (Document number: 723330) for further information on BSP Release.

#### 3.2.1 Obtain Repository Sources and Prepare to Build Image

This section describes the essential steps to obtain the BSP source and getting the system ready to build Yocto Project\*-based image. This section is compulsory, and any missing step might cause the build to fail.

1. Create a bin/ directory in your home directory and include your path:

```

$ mkdir ~/bin

$ PATH=~/bin:$PATH

```

2. Get the repo source and make it executable:

```

$ curl https://storage.googleapis.com/git-repo-downloads/repo

> ~/bin/repo

$ chmod a+x ~/bin/repo

```

#### 3. Make a new directory:

```

$ mkdir <work_dir>

$ cd <work dir>

```

4. Git clone the repo manifest. This manifest will help you to clone all required repositories to create the base BSP:

```

$ repo init -u https://github.com/intel/iotg-yocto-ese-

manifest.git -b refs/tags/release-93 ehl-mr3 -g all

```

5. Pull the repository meta-layers (-j8 for simultaneous downloads, increase/decrease per your needs):

\$ repo sync -c -j8 --force-sync

- 6. Make a branch:

- \$ repo forall managed/\* -c git branch -f BUILD HEAD

7. The Yocto Project\*-based image supports both secure and non-secure booting options. In either case, security keys must be generated and integrated into the image; otherwise, the build may fail. Choose one of the following options to generate the keys:

#### Option 1 (Default):

Security keys will be generated randomly in this option and it is the default configuration. If randomly generated security keys are not affecting your application, no action is required in this step. You can proceed to the next step.

#### Option 2:

You need to generate your own security keys and place them in the 'cert' folder in the *<work\_dir>/build* folder of the build. For steps on how to use a common command-line tool (OpenSSL\*) to generate the keys required for the secure boot, including how to create the Keys and Certificates, place the created keys in the correct folder. Then install the keys into the UEFI BIOS. See *Generate Key for Secure Boot with the Yocto Project\*-based Image and Slim Bootloader/UEFI BIOS* (Document number: 633630).

- **Note:** To use Slim Bootloader or secure boot with UEFI BIOS, you must choose Option 2. Make sure the same keys are used for the Yocto Project\*-based image and Slim Bootloader/UEFI BIOS.

- 8. This is the workaround for the Grub rebase invalid source URL issue. Follow the steps below to modify specific values in the *grub\_2.06.inc* file:

#### Step 1: Go to the path below and edit grub\_2.06.inc

```

$ cd <work dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-iot-main/recipes-bsp/grub

```

\$ vi grub 2.06.inc

Step 2: Find the following lines and modify the original values to new values below:

```

SRCREV grub = "7c993f62b426daba88406c9347f31e6b681d9783"

```

```

SRC_URI:append = "

git://git.savannah.gnu.org/git/gnulib.git;protocol=https;name=

gnulib;destsuffix=git/gnulib;nobranch=1"

SRCREV_gnulib = "9f48fb992a3d7e96610c4ce8be969cff2d61a01b"

```

$PR = "r40 + \{SRCPV\}"$

9. This is the workaround for the GNUlib URL issue. Follow the steps below to modify specific values in the gnulib\_2018-03-07.03.bb file:

Step 1: Go to the path below and edit the gnulib\_2018-03-07.03.bb file

```

$ cd <work dir>/intel-embedded-system-enabling/meta-

openembedded/meta-oe/recipes-support/gnulib

```

\$ vi gnulib 2018-03-07.03.bb

#### Step 2: Find the following lines in its respective section of the file:

```

SRC_URI = "git://git.sv.gnu.org/gnulib.git;branch=master \

inherit utils

cd ${S}

check_git_config

git checkout master

git clone ${S} ${D}/${datadir}/gnulib

```

**Step 3:** Replace all the lines in Step 2 with the new following lines below in its same respective section. Take note for line "inherit utils" is only for removal and there is no replacement.

```

SRC_URI = "git://git.savannah.gnu.org/git/gnulib.git;branch=master \

```

```

install -d ${D}/${datadir}/gnulib

cp --no-preserve=ownership --recursive ${S}/* ${D}/${datadir}/gnulib/

cp --no-preserve=ownership --recursive ${S}/.git ${D}/${datadir}/gnulib/

```

10. This is the workaround for 18021221921 [Missed kernel boot param in RT Kernel] with a patch ID#: 728798 from RDC. Follow steps below to add kernel boot param:

**Step 1:** Download the SBL patch from RDC and copy patch into build machine. You can put the patch file in the /tmp folder of the build machine.

Step 2: Go to this location to run the patch

```

$cd <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-iot-bsp

```

**Step 3:** Run the command to apply the patch

\$ patch -Np1 -i /tmp/sbl.patch

#### Step 4: You will see output below after patching is done

```

$ patching file classes/kernel-sblimage.bbclass

```

#### 3.2.2 Adding Optional Components

intel

This section describes the steps required to integrate Software Tools/Packages, Proprietary Components, and workarounds to the build. For more information about software tools or packages, refer to Section 5.1. For more information about proprietary components and workarounds, see Yocto Project\*-based Board Support Package for Intel Atom<sup>®</sup> x6000E Series, and Intel<sup>®</sup> Pentium<sup>®</sup> and Celeron<sup>®</sup> N and J Series Processors (Kernel 5.15) Release Notes (Document number: 723330).

*Note:* Since the components are optional, the build will not fail if you choose to skip this section. You can still add the components in the future and re-build the image.

#### 3.2.2.1 Integrate Software Tools or Packages

1. This step integrates the bmaptool and/ or devmem2 into the Yocto Project\*-based image. The bmap-tools is needed if you need to install the image from one storage to another storage on the Elkhart Lake CRB (refer to Section 4.4 for steps to install from one storage to another). Devmem2 is needed if you need to test the IBECC feature. Otherwise, you may skip this step.

```

$ cd <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-distro/conf/include

$ vi ese-x86-common.inc

#add the following lines

IMAGE_INSTALL:append = " bmap-tools"

IMAGE_INSTALL:append = " devmem2"

```

2. **[Required for TSN]** This step integrates the TSN Reference Software into the image. TSN Reference Software is needed if you want to explore the TSN technology in your application. Otherwise, you may skip this step. For more information about TSN, refer to Section 3.6 of the *Yocto Project\*-based BSP Release Notes* (Document number: 723330).

```

$ vi <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-distro/conf/include/ese-

x86-common.inc

```

# Add the following lines IMAGE INSTALL:append = " iotg-tsn-ref-sw"

#### 3.2.2.2 Integrate Proprietary Components

This section provides the steps to integrate proprietary components into the Yocto Project\*-based image. It is considered as an optional section as you may skip this section if none of the proprietary components is applicable to your interest. You may choose to integrate one or more components. For more information on the proprietary components, refer to the Yocto Project\*-based Board Support Package for Intel Atom<sup>®</sup> x6000E Series, and Intel<sup>®</sup> Pentium<sup>®</sup> and Celeron<sup>®</sup> N and J Series Processors (Kernel 5.15) Release Notes (Document number: 723330).

Two files from Section 2.2 of the *Yocto Project-based BSP Release Notes* (Document number: 723330) are relevant in this section:

- a. yocto\_project\_mr3\_release.zip (ID# 724686) The zip file consists of recipes and binaries for wireless (meta-intelwireless.zip) and Network Proxy Application (meta-libnetprox.tar.bz2).

- meta-ptcm.tar.gz (ID# 724393) The tarball contains the Real-Time Configuration Manager that required for Intel<sup>®</sup> TCC Tools.

- c. intel-socwatch-yoctorecipe-ver1.zip (ID# 724016) The zip file consists of recipes to integrate the kernel module for Intel<sup>®</sup> Soc

Watch and the user guide to download binary via Intel<sup>®</sup> System Bring-up Toolkit.

Follow the instructions below if you choose to integrate the proprietary components.

1. Create a new folder (for example: proprietary) in the working directory and unzip the yocto\_project\_mr3\_release.zip into the proprietary folder.

```

$ mkdir <work_dir>/proprietary

$ unzip yocto project mr3 release.zip

```

As a result of unzipping, multiple tarballs will be available in the proprietary folder. Untar the tarballs that you would like to integrate in the next steps. Replace <file\_name> with the tarball file name.

```

$ tar -xvf <file_name>.tar.gz

OR

$ tar -xvf <file name>.tar.bz2

```

- 2. Change the directory to the conf folder where local.conf and bblayers.conf are located.

- \$ cd <work\_dir>/build/conf

- 3. Integrate components of the Wi-Fi\* and Bluetooth® technology in the BSP

```

$ vi bblayers.conf

```

# Add the following lines

```

${TOPDIR}/../proprietary/meta-intel-wireless \

```

4. **[Required for Intel<sup>®</sup> TCC Tools]** To integrate the real-time configuration manager (RTCM) by updating the following files:

```

$ vi bblayers.conf

# Add the following lines

{TOPDIR}/../proprietary/meta-ptcm \

$ vi <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-distro/conf/include/ese-

x86-common.inc

# Add the following lines

IMAGE INSTALL append = " ptcm"

```

PTCM INSTALL = "1"

- 5. To integrate the ECMA-393 network proxy technology in the BSP:

- a. Edit bblayers.conf and ese-x86-common.inc

```

$ vi bblayers.conf

# Add the following lines

$ {TOPDIR}/../proprietary/meta-libnetprox \

```

```

$ vi <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-

distro/conf/include/ese-x86-common.inc

```

# Add the following lines and change the path to where you have placed the binaries. IMAGE\_INSTALL:append = " libnetprox"

b. Update networkproxy.cfg ONLY if you need to change port. The config file is set for PSE GbE0 by default. If you need to use PSE GbE1, follow the path below:

\$ vi <work\_dir>/intel-embedded-system-enabling/meta-intelembedded-system-enabling/meta-intel-iot-bsp/recipeskernel/linux/linux-config/bsp/networkproxy.cfg

# change from "CONFIG\_STMMAC\_NETWORK\_PROXY\_PORT=0" to "CONFIG\_STMMAC\_NETWORK\_PROXY\_PORT=1"

c. Edit the lts 5.15 kernel configuration file for updating the network proxy configurations:

```

# vi <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-iot-bsp/recipes-

kernel/linux/linux-intel-iot-lts-5.15 git.bb

```

Append this line at the end of the file:

SRC URI append = " file://bsp/networkproxy.scc"

d. Clean the kernel.

```

bitbake -c cleansstate mc:x86-2021:linux-intel-iot-lts-

5.15

```

- 6. To integrate the kernel module for Intel<sup>®</sup> SoC Watch,

- a. Edit bblayers.conf and ese-x86-common.inc

```

$ vi bblayers.conf

# Add the following lines

$ {TOPDIR}/../proprietary/meta-intel-socwatch \

$ vi <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-

distro/conf/include/ese-x86-common.inc

# Add the following line

KERNEL_PROVIDERS_EXTRA_MODULES[5.15] += " intel-socwatch-

driver"

```

#### 3.2.2.3 Integrate Workarounds or Patches

1. **[Workaround]** This step includes the workaround for the known issue in ASPM (Active State Power Management). Follow the steps if the feature is required in your application. Otherwise, you can skip.

Refer to workaround ID: 1508932757 from Section 3.1.6 Workarounds of the Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors (Kernel 5.15) Release Notes (Document number: 723330).

*Note:* This workaround is not applicable if Real-Time Performance is required.

```

$ vi <work_dir>/build/conf/multiconfig/x86-common.inc

# Add the following lines

APPEND_append = " pcie_aspm.policy=powersupersave"

#save and exit

```

If you have your own kernel patches that are relevant to your application, apply them in this step.

#### 3.2.3 Build the Yocto Project\*-based Image

This section explains the steps required to start the build process. There are a few options to build different types of images:

Note: It is mandatory to choose Option B for Intel® TCC Tools

**Option A:** Image boots with LTS kernel by default. This is a validated image with LTS Kernel as the default boot kernel, GUI, secureboot, partition layout (as required for manageability support) and other third-party software/ tools.

**Option B:** Image boots with real-time kernel by default. This is a validated image with RT kernel as the default boot kernel.

**Option C:** Minimal image with LTS kernel as default boot kernel. This is a non-validated image that contains the same kernel driver as the image in Option A but with minimal user space software (for example, without GUI) for boot up. Wi-Fi drivers are provided by the default kernel and not from iwlwifi-backports.

**Option D:** Netboot image with PXE boot. This is a non-validated image to demonstrate the PXE boot feature in this release. This image is not recommended to be used for other features testing.

Follow the steps below to build the image:

#### Option A: Full image with LTS Kernel as Default Boot Image

1. Start the build process:

```

$ cd <work_dir>/build

$ . ../intel-embedded-system-enabling/oe-init-build-env .

```

#### *Note:* The dot at the end of the above command is part of the command.

2. Run the bitbake compilation command

\$ bitbake mc:x86-2021:core-image-sato-sdk

**Location of Images**: <work\_dir>/build/tmp-x86-2021-glibc/deploy/images/intelcorei7-64/

**Required Files**: core-image-sato-sdk-intel-corei7-64--<date>.wic and core-image-sato-sdk-intel-corei7-64--<date>.wic.bmap

**Note:** The bitbake mc:x86-2021:core-image-sato-sdk command will generate an image that boots up with the LTS Kernel by default and the real-time (RT) Kernel as the second option to be selected on the boot menu (refer to Section 4.3 for more details).

#### Option B: Full image with real-time (RT) kernel as the default boot image

1. Start the build process:

```

$ cd <work_dir>/build

$ . ../intel-embedded-system-enabling/oe-init-build-env .

```

#### Note: The dot at the end of the above command is part of the command

Run the bitbake compilation command.

\$ bitbake mc:x86-rt-2021:core-image-sato-sdk

**Location of Images**: <work\_dir>/build/tmp-x86-rt-2021-glibc/deploy/images/intelcorei7- 64/

**Required Files**: core-image-sato-sdk-intel-corei7-64--<date>.wic and core-image-sato-sdk-intel-corei7-64--<date>.wic.bmap

*Note:* The bitbake mc:x86-rt-2021:core-image-sato-sdk command will generate an image that boots up with the real-time (RT) Kernel by default and the LTS Kernel as the second option.

#### Option C: Minimal image with LTS kernel as default boot image

```

1. Start the build process:

$ cd <work_dir>/build

$ . ../intel-embedded-system-enabling/oe-init-build-env .

```

- Note: The dot at the end of the above command is part of the command

- 2. Run the bitbake compilation command

\$ bitbake mc:x86-2021-minimal:core-image-full-cmdline

Location of Images: <work\_dir>/build/tmp-x86-2021-minimal-glibc/deploy/images/ intel-corei7-64/ Required Files: core-image-full-cmdline-intel-corei7-64--<date>.hddimg

#### Option D: Netboot image with PXE boot

- 1. Start the build process: \$ cd <work\_dir>/build \$ . ../intel-embedded-system-enabling/oe-init-build-env .

- Note: The dot at the end of the above command is part of the command

2. Run the bitbake compilation command

\$ bitbake mc:x86-2021-minimal-netboot:core-image-full-cmdline

Location of Images: <work\_dir>/build/tmp-x86-2021-minimal-netboot-glibc/deploy /images/intel-corei7-64/ Required File: core-image-full-cmdline-intel-corei7-64--<date>.rootfs.uefinetboot.tar.bz2

Refer to the PXE Boot Application Notes (Document number: 635874) for more details.

#### 3.2.4 Subsequent Build of Image

For subsequent rebuilding of the image, cleaning the kernel is recommended before executing bitbake compilation command.

#### For Option A:

bitbake -c cleansstate mc:x86-2021:linux-intel-iot-lts-5.15 (To clean sstate of LTS kernel)

bitbake -c cleansstate mc:x86-2021:linux-intel-iot-lts-rt-5.15 (To clean sstate of RT kernel)

#### For Option B:

bitbake -c cleansstate mc:x86-rt-2021:linux-intel-iot-lts-5.15 (To clean sstate of LTS kernel)

bitbake -c cleansstate mc:x86-rt-2021:linux-intel-iot-lts-rt-5.15 (To clean sstate of RT kernel)

§

### 3.3 Getting Started with Kernel 5.15 BSP Release (MR5)

Refer to the Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors (Kernel 5.15) Release Notes (Document number: 732903) for further information on BSP Release.

*Note:* Intel® TCC Tools will not be supported in this MR5 release as it's not compatible with the Yocto Project version of Kirkstone. If Intel® TCC Tools are needed in the application, do not upgrade to this MR5 release. For more information, refer to the Cache Reservation Library (CRL) Integration for Intel® Platforms to Enable Intel® Time Coordinate Computing (Intel® TCC) public document.

#### 3.3.1 Obtain Repository Sources and Prepare to Build Image

This section describes the essential steps to obtain the BSP source and getting the system ready to build Yocto Project\*-based image. This section is compulsory, and any missing step might cause the build to fail.

1. Create a bin/ directory in your home directory and include your path:

```

$ mkdir ~/bin

$ PATH=~/bin:$PATH

```

2. Get the repo source and make it executable:

```

$ curl https://storage.googleapis.com/git-repo-downloads/repo

> ~/bin/repo

$ chmod a+x ~/bin/repo

```

3. Make a new directory:

```

$ mkdir <work_dir>

$ cd <work_dir>

```

4. Git clone the repo manifest. This manifest will help you to clone all required repositories to create the base BSP:

```

$ repo init -u https://github.com/intel/iotg-yocto-ese-

manifest.git -b refs/tags/release-115 ehl-mr5 -g all

```

5. Pull the repository meta-layers (-j8 for simultaneous downloads, increase/decrease per your needs):

\$ repo sync -c -j8 --force-sync

6. Make a branch:

$\$  repo forall managed/\* -c git branch -f BUILD HEAD

7. The Yocto Project\*-based image supports both secure and non-secure booting options. In either case, security keys must be generated and integrated into the image; otherwise, the build may fail. Choose one of the following options to generate the keys:

#### Option 1 (Default):

Security keys will be generated randomly in this option and it is the default configuration. If randomly generated security keys are not affecting your application, no action is required in this step. You can proceed to the next step.

#### Option 2:

You need to generate your own security keys and place them in the 'cert' folder in the *<work\_dir>/build* folder of the build. For steps on how to use a common command-line tool (OpenSSL\*) to generate the keys required for the secure boot, including how to create the Keys and Certificates, place the created keys in the correct folder. Then install the keys into the UEFI BIOS. See *Generate Key for Secure Boot with the Yocto Project\*-based Image and Slim Bootloader/UEFI BIOS* (Document number: 633630).

*Note:* To use Slim Bootloader or secure boot with UEFI BIOS, you must choose *Option 2*. Make sure the same keys are used for the Yocto Project\*-based image and Slim Bootloader/UEFI BIOS.

#### 3.3.2 Adding Optional Components

This section describes the steps required to integrate Software Tools/Packages, Proprietary Components, and workarounds to the build. For more information about software tools or packages, refer to Section 5.1. For more information about proprietary components and workarounds, see Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors (Kernel 5.15) Release Notes (Document number: 732903).

*Note:* Since the components are optional, the build will not fail if you choose to skip this section. You can still add the components in the future and re-build the image.

#### 3.3.2.1 Integrate Software Tools or Packages

1. This step integrates the bmaptool and/ or devmem2 into the Yocto Project\*-based image. The bmap-tools is needed if you need to install the image from one storage to another storage on the Elkhart Lake CRB (refer to Section 4.4 for steps to install from one storage to another). Devmem2 is needed if you need to test the IBECC feature. Otherwise, you may skip this step.

```

$ cd <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-distro/conf/include

$ vi ese-x86-common.inc

```

```

#add the following lines

IMAGE_INSTALL:append = " bmap-tools"

IMAGE_INSTALL:append = " devmem2"

```

2. **[Required for TSN]** This step integrates the TSN Reference Software into the image. TSN Reference Software is needed if you want to explore the TSN technology in your application. Otherwise, you may skip this step. For more information about TSN, refer to Section 3.6 of the *Yocto Project\*-based BSP Release Notes* (Document number: 732903).

```

$ vi <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-distro/conf/include/ese-

x86-common.inc

```

# Add the following lines IMAGE INSTALL:append = " iotg-tsn-ref-sw"

#### 3.3.2.2 Integrate Proprietary Components

This section provides the steps to integrate proprietary components into the Yocto Project\*-based image. It is considered as an optional section as you may skip this section if none of the proprietary components is applicable to your interest. You may choose to integrate one or more components. For more information on the proprietary components, refer to the Yocto Project\*-based Board Support Package for Intel Atom<sup>®</sup> x6000E Series, and Intel<sup>®</sup> Pentium<sup>®</sup> and Celeron<sup>®</sup> N and J Series Processors (Kernel 5.15) Release Notes (Document number: 732903).

Two files from Section 2.2 of the Yocto Project-based BSP Release Notes (Document number: 732903) are relevant in this section:

- a. yocto\_project\_mr5\_release.zip (ID# 743612)

The zip file consists of recipes and binaries for wireless (meta-intelwireless.zip) and Network Proxy Application (meta-libnetprox.tar.bz2).

- b. intel-socwatch-yoctorecipe-ver1.zip (ID# 724016)

The zip file consists of recipes to integrate the kernel module for Intel<sup>®</sup> Soc

Watch and the user guide to download binary via Intel<sup>®</sup> System Bring-up Toolkit.

Follow the instructions below if you choose to integrate the proprietary components.

1. Create a new folder (for example: proprietary) in the working directory and unzip the yocto\_project\_mr5\_release.zip into the proprietary folder.

```

$ mkdir <work_dir>/proprietary

$ unzip yocto project mr5 release.zip

```

As a result of unzipping, multiple tarballs will be available in the proprietary folder. Untar the tarballs that you would like to integrate in the next steps. Replace <file\_name> with the tarball file name.

```

$ tar -xvf <file_name>.tar.gz

OR

$ tar -xvf <file name>.tar.bz2

```

2. Change the directory to the conf folder where local.conf and bblayers.conf are located.

```

$ cd <work_dir>/build/conf

```

3. Integrate components of the Wi-Fi\* and Bluetooth® technology in the BSP

```

$ vi bblayers.conf

```

# Add the following lines

\${TOPDIR}/../proprietary/meta-intel-wireless \

- 4. To integrate the **ECMA-393 network proxy** technology in the BSP:

- a. Edit bblayers.conf and ese-x86-common.inc

```

$ vi bblayers.conf

# Add the following lines

$ {TOPDIR}/../proprietary/meta-libnetprox \

$ vi <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-

distro/conf/include/ese-x86-common.inc

# Add the following lines and change the path to where you

have placed the binaries.

IMAGE INSTALL:append = " libnetprox"

```

b. Update networkproxy.cfg ONLY if you need to change port. The config file is set for PSE GbE0 by default. If you need to use PSE GbE1, follow the path below:

\$ vi <work\_dir>/intel-embedded-system-enabling/meta-intelembedded-system-enabling/meta-intel-iot-bsp/recipeskernel/linux/linux-config/bsp/networkproxy.cfg

# change from "CONFIG\_STMMAC\_NETWORK\_PROXY\_PORT=0" to "CONFIG\_STMMAC\_NETWORK\_PROXY\_PORT=1"

c. Edit the lts 5.15 kernel configuration file for updating the network proxy configurations:

# vi <work\_dir>/intel-embedded-system-enabling/meta-intelembedded-system-enabling/meta-intel-iot-bsp/recipeskernel/linux/linux-intel-iot-lts-5.15 git.bb

Append this line at the end of the file:

SRC URI:append = " file://bsp/networkproxy.scc"

d. Clean the kernel.

```

bitbake -c cleansstate mc:x86-2021:linux-intel-iot-lts-

5.15

```

#### 5. To integrate the kernel module for Intel® SoC Watch,

a. Edit bblayers.conf and ese-x86-common.inc

```

$ vi bblayers.conf

# Add the following lines

$ {TOPDIR}/../proprietary/meta-intel-socwatch \

$ vi <work_dir>/intel-embedded-system-enabling/meta-intel-

embedded-system-enabling/meta-intel-

distro/conf/include/ese-x86-common.inc

# Add the following line

KERNEL_PROVIDERS_EXTRA_MODULES[5.15] += " intel-socwatch-

driver"

```

#### Getting Started with the BSP

#### 3.3.2.3 Integrate Workarounds or Patches

1. **[Workaround]** This step includes the workaround for the known issue in ASPM (Active State Power Management). Follow the steps if the feature is required in your application. Otherwise, you can skip.

Refer to workaround ID: 1508932757 from Section 3.1.6 Workarounds of the Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors (Kernel 5.15) Release Notes (Document number: 732903).

Note: This workaround is not applicable if Real-Time Performance is required.

```

$ vi <work_dir>/build/conf/multiconfig/x86-common.inc

# Add the following lines

APPEND:append = " pcie_aspm.policy=powersupersave"

#save and exit

```

If you have your own kernel patches that are relevant to your application, apply them in this step.

## 3.3.3 Build the Yocto Project\*-based Image

This section explains the steps required to start the build process. There are a few options to build different types of images:

Note: It is mandatory to choose Option B for Real Time use case

**Option A:** Image boots with LTS kernel by default. This is a validated image with LTS Kernel as the default boot kernel, GUI, secureboot, partition layout (as required for manageability support) and other third-party software/ tools.

**Option B:** Image boots with real-time kernel by default. This is a validated image with RT kernel as the default boot kernel.

**Option C:** Minimal image with LTS kernel as default boot kernel. This is a non-validated image that contains the same kernel driver as the image in Option A but with minimal user space software (for example, without GUI) for boot up. Wi-Fi drivers are provided by the default kernel and not from iwlwifi-backports.

**Option D:** Netboot image with PXE boot. This is a non-validated image to demonstrate the PXE boot feature in this release. This image is not recommended to be used for other features testing.

Follow the steps below to build the image:

#### Option A: Full image with LTS Kernel as Default Boot Image

1. Start the build process:

```

$ cd <work_dir>/build

$ . ../intel-embedded-system-enabling/oe-init-build-env .

```

#### *Note:* The dot at the end of the above command is part of the command.

2. Run the bitbake compilation command

\$ bitbake mc:x86-2021:core-image-sato-sdk

**Location of Images**: <work\_dir>/build/tmp-x86-2021-glibc/deploy/images/intelcorei7-64/

```

Required Files: core-image-sato-sdk-intel-corei7-64--<date>.wic and core-image-sato-sdk-intel-corei7-64--<date>.wic.bmap

```

**Note:** The bitbake mc:x86-2021:core-image-sato-sdk command will generate an image that boots up with the LTS Kernel by default and the real-time (RT) Kernel as the second option to be selected on the boot menu (refer to Section 4.3 for more details).

## Option B: Full image with real-time (RT) kernel as the default boot image

1. Start the build process:

```

$ cd <work_dir>/build

```

```

$ . ../intel-embedded-system-enabling/oe-init-build-env .

```

Note: The dot at the end of the above command is part of the command

2. Run the bitbake compilation command.

\$ bitbake mc:x86-rt-2021:core-image-sato-sdk

**Location of Images**: <work\_dir>/build/tmp-x86-rt-2021-glibc/deploy/images/intelcorei7- 64/

**Required Files**: core-image-sato-sdk-intel-corei7-64--<date>.wic and core-image-sato-sdk-intel-corei7-64--<date>.wic.bmap

*Note:* The bitbake mc:x86-rt-2021:core-image-sato-sdk command will generate an image that boots up with the real-time (RT) Kernel by default and the LTS Kernel as the second option.

Getting Started with the BSP

#### Option C: Minimal image with LTS kernel as default boot image

1. Start the build process:

```

$ cd <work_dir>/build

$ . ../intel-embedded-system-enabling/oe-init-build-env .

```

#### Note: The dot at the end of the above command is part of the command

2. Run the bitbake compilation command

\$ bitbake mc:x86-2021-minimal:core-image-full-cmdline

Location of Images: <work\_dir>/build/tmp-x86-2021-minimal-glibc/deploy/images/ intel-corei7-64/ Required Files: core-image-full-cmdline-intel-corei7-64--<date>.hddimg

#### **Option D: Netboot image with PXE boot**

1. Start the build process: \$ cd <work\_dir>/build \$ . ../intel-embedded-system-enabling/oe-init-build-env .

Note: The dot at the end of the above command is part of the command

2. Run the bitbake compilation command

\$ bitbake mc:x86-2021-minimal-netboot:core-image-full-cmdline

Location of Images: <work\_dir>/build/tmp-x86-2021-minimal-netboot-glibc/deploy /images/intel-corei7-64/ Required File: core-image-full-cmdline-intel-corei7-64--<date>.rootfs.uefinetboot.tar.bz2

Refer to the PXE Boot Application Notes (Document number: 635874) for more details.

## 3.3.4 Subsequent Build of Image

For subsequent rebuilding of the image, cleaning the kernel is recommended before executing bitbake compilation command.

#### For Option A:

bitbake -c cleansstate mc:x86-2021:linux-intel-iot-lts-5.15 (To clean sstate of LTS kernel)

bitbake -c cleansstate mc:x86-2021:linux-intel-iot-lts-rt-5.15 (To clean sstate of RT kernel)

#### For Option B:

bitbake -c cleansstate mc:x86-rt-2021:linux-intel-iot-lts-5.15 (To clean sstate of LTS kernel)

bitbake -c cleansstate mc:x86-rt-2021:linux-intel-iot-lts-rt-5.15 (To clean sstate of RT kernel)

§

## 4.0 Next Step to Boot Up CRB

This section describes the steps required to prepare a bootable Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors CRB. Last sub-section contains the link to Intel® TCC Tools for the next step.

## 4.1 Prepare a Bootable Image with the USB Flash Drive

Intel recommends using "bmaptool" to prepare a bootable image if the USB flash drive is being used (minimum size of 64 GB is recommended).

1. Download the latest bmaptool release from https://github.com/intel/bmaptools/releases into the Ubuntu\* host system, where you build the Yocto Projectbased image.

\$ curl -Lo bmaptool https://github.com/0lorg/bmaptools/releases/download/v3.4/bmaptool && chmod +x bmaptool

2. Ensure that Python\* module six is installed on the system.

pip3 install six

3. Insert the USB flash drive and ensure all partitions of the target device (the USB flash drive in this case) are unmounted. Refer to Section 5.1, Further References, on how to find the USB device.

**WARNING:** You could wipe off your hard drive if the wrong device is chosen.

4. Run the following command (assume the USB flash drive is using /dev/sdc) to generate a bootable USB flash drive:

\$ sudo ./bmaptool copy --bmap <path>/core-image-sato-xxx-<date>.wic.bmap <path>/core-image-sato-<date>.wic /dev/sdc

- 5. This step is required only if you want to have UEFI Secure Boot. Copy all of the files below, which you have generated earlier by following "Generate Key for Secure Boot with the Yocto Project\*-based Image and Bootloader/UEFI BIOS," (Document number: 633630) into the USB flash drive:

- DB.cer, KEK.cer and PK.cer.

## NOTES:

- 1. If you are copying to a different USB flash drive, make sure the USB flash drive is in an FAT32 format.

- 2. If you are copying into the USB flash drive that is the same as the bootable version, copy it to the same level of /BOOT/EFI/bootx64.efi dir.

## 4.2 Boot up Elkhart Lake CRB with USB Flash Drive

This section provides the steps to boot up the CRB with a bootable USB Flash Drive prepared in the previous section. For more information on CRB, refer to the *Elkhart Lake CRB User Guide* (Document number: 615859).

- 1. Insert a USB flash drive into the Elkhart Lake CRB and ensure the IFWI has been installed.

- 2. Boot up the Elkhart Lake CRB by pressing the power button. Press F2 if you need to enter the BIOS menu for configuration or to select the boot option.

- 3. **[Optional]** At the GRUB boot menu, press the key "e" on the keyboard. Append "i915.force\_probe=\*" to the end of the kernel boot parameters and press Ctrl + x to continue the booting process. This step will enable the multi-display function.

- 4. The Secure Boot feature is disabled by default in the UEFI BIOS. If you would like to use the UEFI Secure Boot feature, you will need to insert the security key that was generated in the previous section through the UEFI BIOS.

For steps on how to install the keys into the UEFI BIOS menu, see "Generate Key for Secure Boot with the Yocto Project\*-based Image and Bootloader/UEFI BIOS" (Document number: 633630).

5. Once the UEFI BIOS has passed, the log in screen will be shown. Type "root" to log in and no password is required by default.

## NOTES:

- 1. "Install" option is no longer applicable in this image. Make sure the bmaptool is integrated in the image as guided in Section 3.1.2.1. Refer to Section 4.4 to install the image into the Elkhart Lake CRB local drive.

- 2. eMMC storage on the Elkhart Lake CRB is limited. Only the minimal image (refer to Section 3.1.3 for Kernel 5.4 and Section 3.2.3 for Kernel 5.15) is small enough to install in the eMMC.

Yocto Project\*-based Board Support Package for Intel Atom® x6000E Series, and Intel® Pentium® and Celeron® N and J Series Processors Get Started Guide