# Intel® Manycore Platform Software Stack (Intel® MPSS)

**User's Guide**

September 2015

Copyright © 2013-2015 Intel Corporation All Rights Reserved US Revision: 3.6 World Wide Web: <u>http://www.intel.com</u>

# **Disclaimer and Legal Information**

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting: <a href="http://www.intel.com/design/literature.htm">http://www.intel.com/design/literature.htm</a>

Intel, the Intel logo, Intel Xeon Phi, and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2015, Intel Corporation. All rights reserved.

# **Revision History**

| Revision<br>Number | Description                                                          | Revision Date  |

|--------------------|----------------------------------------------------------------------|----------------|

| Version 3.6        | Release of the 3.6 Intel $\ensuremath{\mathbb{R}}$ MPSS User's Guide | September 2015 |

| Version 3.6        | Initial draft of the 3.6 Intel® MPSS User's Guide                    | August 2015    |

# **Table of Contents**

| 1 |                   | About Th                                                                                                                                                                                       | nis Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1               | Overvie                                                                                                                                                                                        | ew of this Document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 1.2               | Intel®                                                                                                                                                                                         | MPSS Release History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                   | 1.2.1                                                                                                                                                                                          | Technology Previews in this Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 1.3               | Notatio                                                                                                                                                                                        | nal Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                   | 1.3.1                                                                                                                                                                                          | Symbols within Normal Text                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                   | 1.3.2                                                                                                                                                                                          | Code conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 1.4               | Termine                                                                                                                                                                                        | ology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2 |                   | Intel® M                                                                                                                                                                                       | IPSS at a Glance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16                                                                                                                                                                                                                                                                                                                                                                                                                                     |

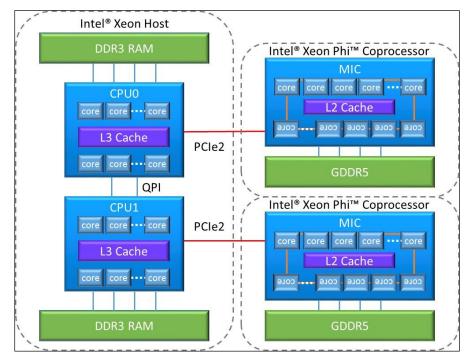

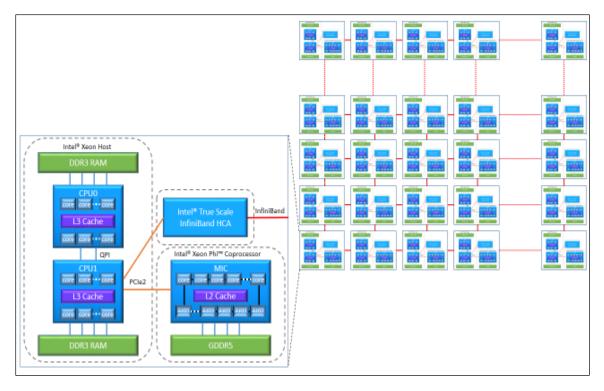

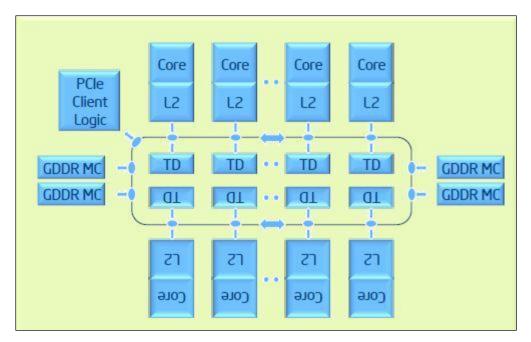

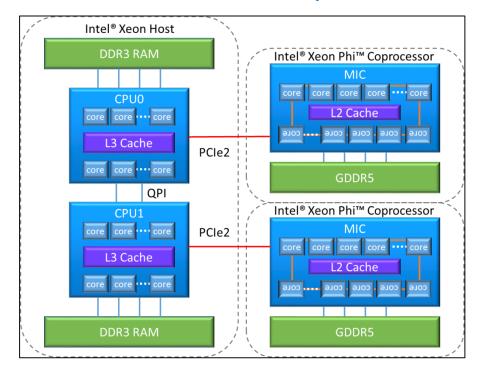

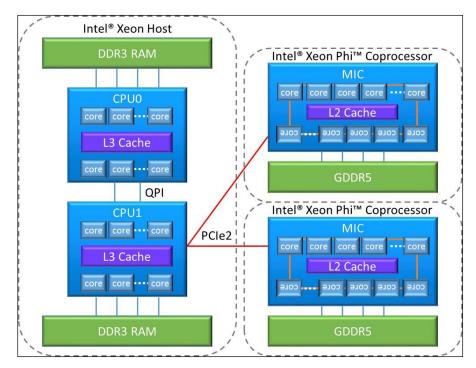

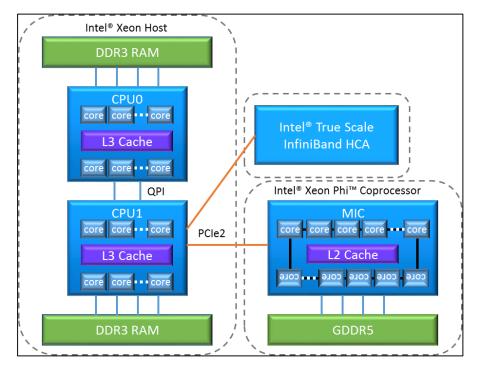

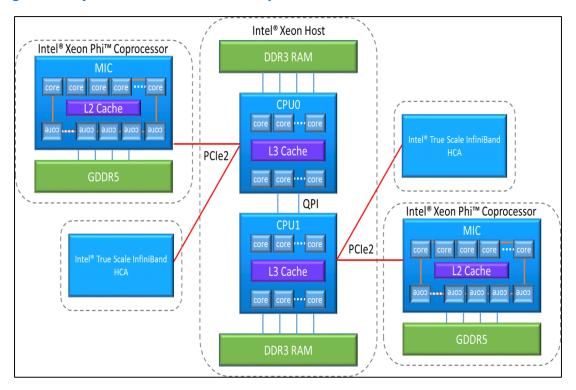

|   | 2.1               | Intel®                                                                                                                                                                                         | Xeon Phi <sup>™</sup> Hardware and System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 2.2               | Progran                                                                                                                                                                                        | nming Models and the Intel® MPSS Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18                                                                                                                                                                                                                                                                                                                                                                                                                                     |

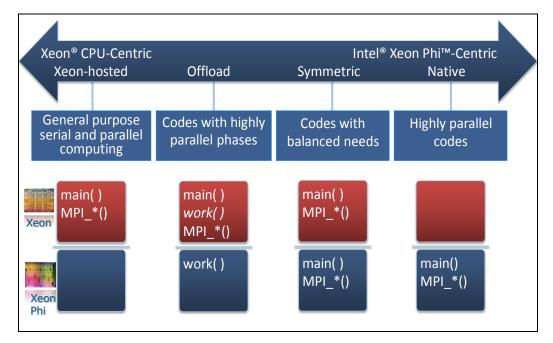

|   |                   | 2.2.1                                                                                                                                                                                          | Programming Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

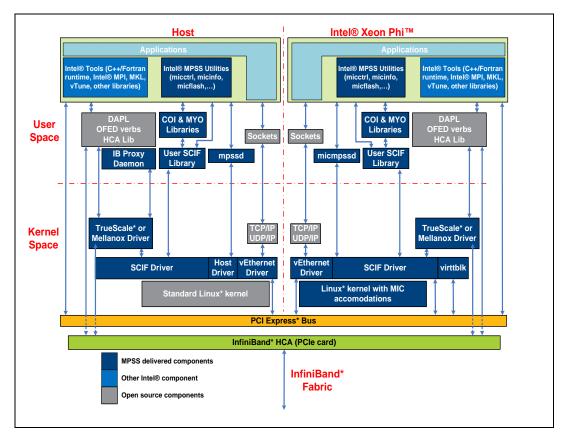

|   |                   | 2.2.2                                                                                                                                                                                          | Intel® MPSS Software Architecture and Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                     |

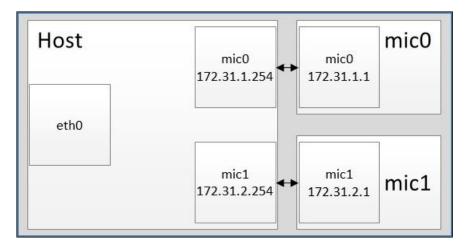

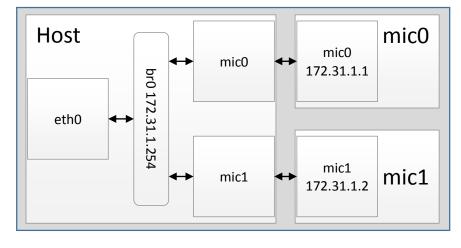

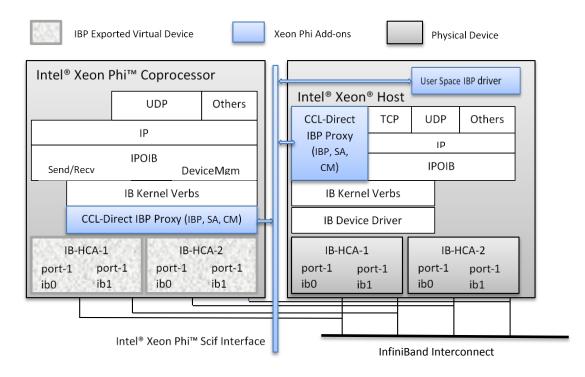

|   |                   | 2.2.3                                                                                                                                                                                          | Intel® Xeon Phi <sup>™</sup> Coprocessor Networking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 2.3               | Suppor                                                                                                                                                                                         | ted Intel® Productivity Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 2.4               | Related                                                                                                                                                                                        | Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                   | 2.4.1                                                                                                                                                                                          | SCIF documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                   | 2.4.2                                                                                                                                                                                          | COI Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                   | 2.4.3                                                                                                                                                                                          | MYO Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                   | 2.4.4                                                                                                                                                                                          | Micperf Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                   | 2.4.5                                                                                                                                                                                          | Intel® Xeon Phi <sup>™</sup> Coprocessor Collateral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3 |                   |                                                                                                                                                                                                | eon Phi™ Coprocessor Installation Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                   |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 3.1               | Hardwa                                                                                                                                                                                         | re and Software Prerequisites                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 3.1               | 3.1.1                                                                                                                                                                                          | Host System HW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 3.1               | 3.1.1<br>3.1.2                                                                                                                                                                                 | Host System HW<br>BIOS Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30<br>30                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 3.1               | 3.1.1<br>3.1.2<br>3.1.3                                                                                                                                                                        | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30<br>30<br>31                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 3.1               | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                                                                                                                                               | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30<br>30<br>31<br>31                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 3.1               | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5                                                                                                                                                      | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30<br>31<br>31<br>31<br>31                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 3.1               | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6                                                                                                                                             | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30<br>31<br>31<br>31<br>31<br>32                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 3.1               | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7                                                                                                                                    | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30<br>31<br>31<br>31<br>32<br>32                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                   | $3.1.1 \\ 3.1.2 \\ 3.1.3 \\ 3.1.4 \\ 3.1.5 \\ 3.1.6 \\ 3.1.7 \\ 3.1.8 $                                                                                                                        | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30<br>31<br>31<br>31<br>32<br>32<br>32<br>33                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 3.1<br>3.2        | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®                                                                                                                 | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi <sup>™</sup> Coprocessor Card Physical Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30<br>31<br>31<br>31<br>32<br>32<br>32<br>33<br>33                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                   | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®<br>3.2.1                                                                                                        | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi <sup>™</sup> Coprocessor Card Physical Installation<br>Workstation Considerations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30<br>31<br>31<br>32<br>32<br>32<br>33<br>34<br>35                                                                                                                                                                                                                                                                                                                                                                                     |

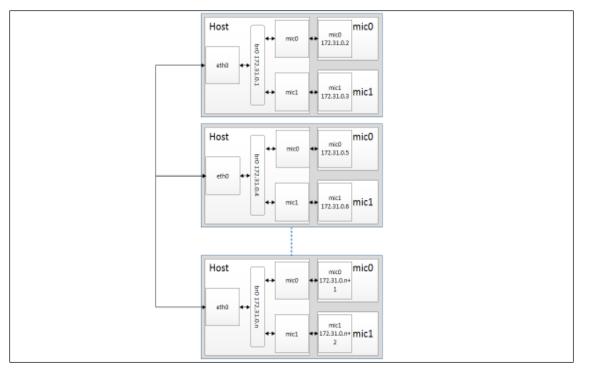

|   |                   | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®                                                                                                                 | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi <sup>™</sup> Coprocessor Card Physical Installation<br>Workstation Considerations<br>Cluster Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30<br>31<br>31<br>32<br>32<br>32<br>33<br>34<br>35<br>37                                                                                                                                                                                                                                                                                                                                                                               |

|   |                   | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®<br>3.2.1<br>3.2.2<br>3.2.3                                                                                      | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi <sup>™</sup> Coprocessor Card Physical Installation<br>Workstation Considerations<br>Cluster Considerations<br>Validate Intel® Xeon Phi <sup>™</sup> Coprocessor physical installation                                                                                                                                                                                                                                                                                                                                                                                 | 30<br>31<br>31<br>31<br>32<br>32<br>32<br>33<br>34<br>35<br>37<br>38                                                                                                                                                                                                                                                                                                                                                                   |

|   | 3.2               | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®<br>3.2.1<br>3.2.2<br>3.2.3<br>Base In                                                                           | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi <sup>™</sup> Coprocessor Card Physical Installation<br>Workstation Considerations<br>Cluster Considerations<br>Validate Intel® Xeon Phi <sup>™</sup> Coprocessor physical installation<br>tel® MPSS Installation                                                                                                                                                                                                                                                                                                                                                       | 30<br>31<br>31<br>31<br>32<br>32<br>32<br>33<br>34<br>35<br>37<br>38<br>39                                                                                                                                                                                                                                                                                                                                                             |

|   | 3.2               | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®<br>3.2.1<br>3.2.2<br>3.2.3<br>Base In<br>3.3.1                                                                  | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi <sup>™</sup> Coprocessor Card Physical Installation<br>Workstation Considerations<br>Cluster Considerations<br>Validate Intel® Xeon Phi <sup>™</sup> Coprocessor physical installation<br>tel® MPSS Installation<br>Get the Intel® MPSS Distribution                                                                                                                                                                                                                                                                                                                   | 30<br>31<br>31<br>31<br>32<br>32<br>32<br>33<br>34<br>35<br>37<br>38<br>39<br>39                                                                                                                                                                                                                                                                                                                                                       |

|   | 3.2               | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®<br>3.2.1<br>3.2.2<br>3.2.3<br>Base In<br>3.3.1                                                                  | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi <sup>™</sup> Coprocessor Card Physical Installation<br>Workstation Considerations<br>Cluster Considerations<br>Validate Intel® Xeon Phi <sup>™</sup> Coprocessor physical installation<br>tel® MPSS Installation                                                                                                                                                                                                                                                                                                                                                       | 30<br>31<br>31<br>31<br>32<br>32<br>32<br>33<br>34<br>35<br>37<br>38<br>39<br>39<br>39                                                                                                                                                                                                                                                                                                                                                 |

|   | 3.2               | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®<br>3.2.1<br>3.2.2<br>3.2.3<br>Base In<br>3.3.1<br>3.3.2                                                         | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi <sup>™</sup> Coprocessor Card Physical Installation<br>Workstation Considerations<br>Cluster Considerations<br>Validate Intel® Xeon Phi <sup>™</sup> Coprocessor physical installation<br>tel® MPSS Installation<br>Get the Intel® MPSS Distribution<br>Uninstall Previous Intel® MPSS Installation Prior to Upgrade                                                                                                                                                                                                                                                   | 30<br>31<br>31<br>31<br>32<br>32<br>32<br>33<br>34<br>35<br>37<br>38<br>39<br>39<br>39<br>39<br>39                                                                                                                                                                                                                                                                                                                                     |

|   | 3.2               | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®<br>3.2.1<br>3.2.2<br>3.2.3<br>Base In<br>3.3.1<br>3.3.2<br>3.3.3                                                | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi <sup>™</sup> Coprocessor Card Physical Installation<br>Workstation Considerations<br>Cluster Considerations<br>Validate Intel® Xeon Phi <sup>™</sup> Coprocessor physical installation<br>tel® MPSS Installation<br>Get the Intel® MPSS Distribution<br>Uninstall Previous Intel® MPSS Installation Prior to Upgrade<br>Rebuild Intel® MPSS Host Drivers                                                                                                                                                                                                               | 30<br>31<br>31<br>32<br>32<br>32<br>33<br>34<br>35<br>37<br>39<br>39<br>39<br>39<br>39<br>39<br>39<br>39                                                                                                                                                                                                                                                                                                                               |

|   | 3.2               | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®<br>3.2.1<br>3.2.2<br>3.2.3<br>Base In<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6                     | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi <sup>™</sup> Coprocessor Card Physical Installation<br>Workstation Considerations<br>Cluster Considerations<br>Cluster Considerations<br>Validate Intel® Xeon Phi <sup>™</sup> Coprocessor physical installation<br>tel® MPSS Installation<br>Get the Intel® MPSS Distribution<br>Uninstall Previous Intel® MPSS Installation Prior to Upgrade<br>Rebuild Intel® MPSS Host Drivers<br>Update Intel® Xeon Phi <sup>™</sup> Coprocessor Flash & SMC Firmware<br>Initialize Intel® MPSS default configuration settings.<br>Start Intel® MPSS                              | 30<br>31<br>31<br>32<br>32<br>32<br>33<br>34<br>35<br>37<br>39<br>39<br>39<br>39<br>39<br>39<br>39<br>39<br>39<br>39<br>34<br>35<br>37<br>31<br>31<br>31<br>31<br>31<br>32<br>32<br>33<br>34<br>35<br>37<br>39<br>39<br>39<br>34<br>39<br>39<br>34<br>35<br>39<br>34<br>34<br>39<br>39<br>34<br>34<br>34<br>35<br>34<br>34<br>35<br>34<br>39<br>34<br>34<br>35<br>34<br>34<br>35<br>34<br>34<br>35<br>34<br>34<br>35<br>34<br>34<br>35 |

|   | 3.2<br>3.3        | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®<br>3.2.1<br>3.2.2<br>3.2.3<br>Base In<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.7                     | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi <sup>™</sup> Coprocessor Card Physical Installation<br>Workstation Considerations.<br>Cluster Considerations<br>Validate Intel® Xeon Phi <sup>™</sup> Coprocessor physical installation<br>tel® MPSS Installation<br>Get the Intel® MPSS Distribution.<br>Uninstall Previous Intel® MPSS Installation Prior to Upgrade<br>Rebuild Intel® MPSS Host Drivers<br>Update Intel® Xeon Phi <sup>™</sup> Coprocessor Flash & SMC Firmware<br>Initialize Intel® MPSS default configuration settings.<br>Start Intel® MPSS<br>Validate Base Intel® MPSS Installation            | 30<br>31<br>31<br>32<br>32<br>32<br>32<br>33<br>34<br>35<br>37<br>38<br>39<br>39<br>39<br>39<br>39<br>39<br>39<br>39<br>40<br>41<br>45                                                                                                                                                                                                                                                                                                 |

|   | 3.2<br>3.3<br>3.4 | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®<br>3.2.1<br>3.2.2<br>3.2.3<br>Base In<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>Basic W | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi™ Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi™ Coprocessor Card Physical Installation<br>Workstation Considerations<br>Cluster Considerations<br>Validate Intel® Xeon Phi™ Coprocessor physical installation<br>tel® MPSS Installation<br>Get the Intel® MPSS Distribution<br>Uninstall Previous Intel® MPSS Installation Prior to Upgrade<br>Rebuild Intel® MPSS Host Drivers<br>Update Intel® MPSS default configuration settings.<br>Start Intel® MPSS Installation<br>Validate Base Intel® MPSS Installation                                                                                                                 | 30<br>31<br>31<br>31<br>32<br>32<br>32<br>33<br>34<br>35<br>37<br>38<br>39<br>39<br>39<br>39<br>39<br>40<br>41<br>45<br>49                                                                                                                                                                                                                                                                                                             |

|   | 3.2<br>3.3        | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®<br>3.2.1<br>3.2.2<br>3.2.3<br>Base In<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>Basic W | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi <sup>™</sup> Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi <sup>™</sup> Coprocessor Card Physical Installation<br>Workstation Considerations.<br>Cluster Considerations.<br>Cluster Considerations.<br>Validate Intel® Xeon Phi <sup>™</sup> Coprocessor physical installation<br>tel® MPSS Installation<br>Get the Intel® MPSS Distribution.<br>Uninstall Previous Intel® MPSS Installation Prior to Upgrade<br>Rebuild Intel® MPSS Host Drivers<br>Update Intel® MPSS default configuration settings.<br>Start Intel® MPSS<br>Validate Base Intel® MPSS Installation<br>/orkstation Installation is Complete<br>k Configuration | 30<br>31<br>31<br>31<br>32<br>32<br>32<br>33<br>34<br>35<br>37<br>38<br>39<br>39<br>39<br>39<br>39<br>40<br>41<br>45<br>45<br>49<br>50                                                                                                                                                                                                                                                                                                 |

|   | 3.2<br>3.3<br>3.4 | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>Intel®<br>3.2.1<br>3.2.2<br>3.2.3<br>Base In<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>Basic W | Host System HW<br>BIOS Configuration<br>Supported Host Operating Systems<br>Host Operating System Configuration<br>Root Access<br>SSH Access to the Intel® Xeon Phi™ Coprocessor<br>Init Scripts<br>Network Manager<br>Xeon Phi™ Coprocessor Card Physical Installation<br>Workstation Considerations<br>Cluster Considerations<br>Validate Intel® Xeon Phi™ Coprocessor physical installation<br>tel® MPSS Installation<br>Get the Intel® MPSS Distribution<br>Uninstall Previous Intel® MPSS Installation Prior to Upgrade<br>Rebuild Intel® MPSS Host Drivers<br>Update Intel® MPSS default configuration settings.<br>Start Intel® MPSS Installation<br>Validate Base Intel® MPSS Installation                                                                                                                 | 30<br>31<br>31<br>31<br>32<br>32<br>33<br>34<br>35<br>37<br>38<br>39<br>39<br>39<br>39<br>39<br>39<br>40<br>41<br>45<br>45<br>49<br>50<br>50                                                                                                                                                                                                                                                                                           |

| 3.6        | $\begin{array}{c} 3.6.1 \\ 3.6.2 \\ 3.6.3 \\ 3.6.4 \\ 3.6.5 \\ 3.6.6 \\ 3.6.7 \\ 3.6.8 \\ 3.6.9 \\ 3.6.10 \end{array}$ | Configuring a Basic External Bridge<br>Defining and Implementing Exported/Mounted File Systems<br>Configuring the Host Firewall<br>How to Install Lustre* on the Intel® Xeon Phi <sup>™</sup> Coprocessor Card<br>Ing OFED with Intel® MPSS Support (optional)<br>Supported OFED distros<br>Tips for OFED distributions<br>Install OFED +<br>Install OFED 1.5.4.1.<br>Install OFED 1.5.4.1.<br>Install OFED-3.5-2-MIC<br>Install OFED-3.12-1<br>Install OFED 3.18<br>Install OFED 3.18<br>Install Mellanox* OFED 2.x<br>Starting OFED<br>Stopping/restarting OFED<br>Validate OFED Installation | 52<br>53<br>54<br>56<br>57<br>58<br>59<br>60<br>61<br>61<br>61<br>62<br>62 |

|------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|            |                                                                                                                        | ring and Booting the Intel® Xeon Phi™ Coprocessor Operating S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |

| 4.1        |                                                                                                                        | ed Configuration and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

|            | 4.1.1                                                                                                                  | Configuration Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

|            | 4.1.2                                                                                                                  | Initializing, Updating and Resetting the Configuration Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

|            | 4.1.3                                                                                                                  | micctrl Directory Path Modifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

|            | $4.1.4 \\ 4.1.5$                                                                                                       | Boot Configuration<br>Assisted Boot Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

| 4.2        |                                                                                                                        | I Configuration and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

|            | 4.2.1                                                                                                                  | Directly Editing (and persisting) Card /etc Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

|            | 4.2.2                                                                                                                  | NFS Mounting the Root and Other File Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

|            | 4.2.3                                                                                                                  | Driver sysfs Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |