# Lenovo

# DC Persistent Memory Module Population Manual

# **Contents**

| Chapter 1. DC Persistent Memory           | SR570 Mixed Memory Mode               |

|-------------------------------------------|---------------------------------------|

| Module (DCPMM) setup                      | SR590 DCPMM and DIMM configuration 34 |

| Configure DC Persistent Memory Module     | SR590 Memory Mode                     |

| (DCPMM)                                   | SR590 App Direct Mode                 |

| Update the firmware 6                     | SR590 Mixed Memory Mode               |

| Chapter 2. DCPMM installation order       | SR630 DCPMM and DIMM configuration 40 |

| for ThinkSystem compute nodes 9           | SR630 Memory Mode 41                  |

| -                                         | SR630 App Direct Mode 43              |

| SN550 DCPMM and DIMM configuration 9      | SR630 Mixed Memory Mode 46            |

| SNS50 Memory Mode                         | SR650 DCPMM and DIMM configuration 48 |

| SN850 DCPMM and DIMM configuration 12     | SR650 Memory Mode 49                  |

| SN850 Memory Mode with two processors 14  | SR650 App Direct Mode 51              |

| SN850 Memory Mode with four processors 16 | SR650 Mixed Memory Mode 54            |

| Chapter 3. DCPMM installation order       | SR850 DCPMM and DIMM configuration 56 |

| for ThinkSystem high-density              | SR850 Memory Mode 59                  |

| servers                                   | SR850 App Direct Mode 61              |

| SD530 DCPMM and DIMM configuration 19     | SR850 Mixed Memory Mode 65            |

| SD530 Memory Mode 20                      | SR860 DCPMM and DIMM configuration 66 |

| SD530 App Direct Mode 20                  | SR860 Memory Mode 70                  |

| SD530 Mixed Memory Mode                   | SR860 App Direct Mode 72              |

| SD650 DCPMM and DIMM configuration 23     | SR860 Mixed Memory Mode 76            |

| SD650 DCPMM installation order            | SR950 DCPMM and DIMM configuration 77 |

|                                           | SR950 Memory Mode 81                  |

| Chapter 4. DCPMM installation order       | SR950 App Direct Mode 91              |

| for ThinkSystem rack servers 29           | SR950 Mixed Memory Mode 104           |

| SR570 DCPMM and DIMM configuration 29     |                                       |

| SR570 Memory Mode 30                      | Index                                 |

| SB570 Ann Direct Mode 31                  |                                       |

© Copyright Lenovo 2019

## Chapter 1. DC Persistent Memory Module (DCPMM) setup

Follow the instructions in this section to complete required setup before installing DCPMMs for the first time, determine the most suitable configuration, and install memory modules accordingly.

Complete the following steps to finish system setup to support DCPMMs, and install the memory modules according to the designated combination.

- 1. Update the system firmware to the latest version that supports DCPMMs (see "Update the firmware" on page 6).

- 2. Make sure to meet all the following requirements before installing DCPMMs.

- All the DCPMMs that are installed must be of the same part number.

- All the DRAM DIMMs that are installed must be of the same type, rank, and capacity with minimum capacity of 16 GB. It is recommended to use Lenovo DRAM DIMMs of the same part number.

- 3. Refer to *DCPMM and DIMM installation order* sections in each system to determine the most suitable combination and the following:

- Number and capacity of the DCPMMs and DRAM DIMMs to install.

- Check if the presently installed processors support the combination. If not, replace the processors with ones that support the combination.

- 4. Based on the determined DCPMM combination, acquire the DCPMMs, DRAM DIMMs and processors if necessary.

- 5. Replace the processors if necessary.

- 6. Remove all the memory modules that are installed.

- 7. Follow the slot combination in *DCPMM and DIMM installation order* sections in each system to install all the DCPMMs and DRAM DIMMs.

- 8. Disable security on all the installed DCPMMs (see "Configure DC Persistent Memory Module (DCPMM)" on page 1).

- 9. Make sure the DCPMM firmware is the latest version. If not, update it to the latest version (see <a href="https://sysmgt.lenovofiles.com/help/topic/com.lenovo.lxca.doc/update\_fw.html">https://sysmgt.lenovofiles.com/help/topic/com.lenovo.lxca.doc/update\_fw.html</a>).

- 10. Configure DCPMMs so that the capacity is available for use (see "Configure DC Persistent Memory Module (DCPMM)" on page 1).

## **Configure DC Persistent Memory Module (DCPMM)**

Follow the instructions in this section to configure DCPMMs and DRAM DIMMs.

DCPMM capacity could act as accessible persistent memory for applications or volatile system memory. Based on the approximate percentage of DCPMM capacity invested in volatile system memory, the following three operating modes are available for choice:

• **App Direct Mode** (0% of DCPMM capacity acts as system memory):

In this mode, DCPMMs act as independent and persistent memory resources directly accessible by specific applications, and DRAM DIMMs act as system memory.

The total displayed volatile system memory in this mode is the sum of DRAM DIMM capacity.

## Notes:

© Copyright Lenovo 2019

- In App Direct Mode, the DRAM DIMMs that are installed can be configured to mirror mode.

- When only one DCPMM is installed for each processor, only not-interleaved App Direct Mode is supported.

- Mixed Memory Mode (1-99% of DCPMM capacity acts as system memory):

In this mode, some percentage of DCPMM capacity is directly accessible to specific applications (App Direct), while the rest serves as system memory. The App Direct part of DCPMM is displayed as persistent memory, while the rest of DCPMM capacity is displayed as system memory. DRAM DIMMs act as cache in this mode.

The total displayed volatile system memory in this mode is the DCPMM capacity that is invested in volatile system memory.

• Memory Mode (100% of DCPMM capacity acts as system memory):

In this mode, DCPMMs act as volatile system memory, while DRAM DIMMs act as cache.

The total displayed volatile system memory in this mode is the sum of DCPMM capacity.

## **DCPMM Management options**

DCPMMs can be managed with the following tools:

## Lenovo XClarity Provisioning Manager (LEPT)

To open LEPT, power on the system and press F1 as soon as the logo screen appears. If a password has been set, enter the password to unlock LEPT.

Go to **UEFI Setup** → **System Settings** → **Intel Optane DCPMMs** to configure and manage DCPMMs.

For more details, see https://sysmgt.lenovofiles.com/help/topic/LXPM/using LXPM.html.

Note: If the text-based interface of Setup Utility opens instead of Lenovo XClarity Provisioning Manager, go to System Settings → <F1> Start Control and select Tool Suite. Then, reboot the system and press **F1** as soon as the logo screen appears to open Lenovo XClarity Provisioning Manager.

### Setup Utility

To enter Setup Utility:

- 1. Power on the system and press **F1** to open LEPT.

- 2. Go to **UEFI Settings** → **System Settings**, click on the pull-down menu on the upper right corner of the screen, and select **Text Setup**.

- 3. Reboot the system, and press **F1** as soon as the logo screen appears.

Go to System Configuration and Boot Management → System Settings → Intel Optane DCPMMs to configure and manage DCPMMs.

## Lenovo XClarity Essentials OneCLI

Some management options are available in commands that are executed in the path of Lenovo XClarity Essentials OneCLI in the operating system. See https://sysmgt.lenovofiles.com/help/topic/toolsctr\_cli lenovo/onecli t download use tcscli.html to learn how to download and use Lenovo XClarity Essentials OneCLI.

Following are the available management options:

## Intel Optane DCPMM details

Select this option to view the following details concerning each of the the installed DCPMMs:

- Firmware version

- Configuration status

- Raw capacity

- Memory capacity

- App Direct capacity

- Unconfigured capacity

- Inaccessible capacity

- Reserved capacity

- Percentage remaining

- Security state

Alternatively, view DCPMM details with the following command in OneCLI:

onecli.exe config show IntelOptaneDCPMM

--imm USERID:PASSWORD@10.104.195.86

#### Notes:

- USERID stands for XCC user ID.

- PASSWORD stands for XCC user password.

- 10.104.195.86 stands for IP address.

#### Goals

## - Memory Mode [%]

Select this option to define the percentage of DCPMM capacity that is invested in system memory, and hence decide the DCPMM mode:

- **0%:** App Direct Mode

- 1-99%: Mixed Memory Mode

- **100%:** Memory Mode

Go to Goals → Memory Mode [%], input the memory percentage, and reboot the system.

#### Notes:

- Before changing from one mode to another:

- Make sure the capacity of installed DCPMMs and DRAM DIMMs meets system requirements for the new mode.

- Back up all the data and delete all the created namespaces. Go to Namespaces → View/ Modify/Delete Namespaces to delete the created namespaces.

- 3. Perform secure erase on all the installed DCPMMs. Go to **Security → Press to Secure Erase** to perform secure erase.

- After the system is rebooted and the input goal value is applied, the displayed value in System

Configuration and Boot Management → Intel Optane DCPMMs → Goals will go back to the

following default selectable options:

- Scope: [Platform]

- Memory Mode [%]: 0

- Persistent Memory Type: [App Direct]

These values are selectable options for DCPMM settings, and do not represent the current DCPMM status.

In addition, you can take advantage of a memory configurator, which is available at the following site: <a href="http://lconfig.lenovo.com/#/memory\_configuration">http://lconfig.lenovo.com/#/memory\_configuration</a>

Alternatively, set DCPMM Goals with the following commands in OneCLI:

1. Set create goal status.

```

onecli.exe config set IntelOptaneDCPMM.CreateGoal Yes --imm USERID:PASSWORD@10.104.195.86

```

2. Define the DCPMM capacity that is invested in system volatile memory.

```

onecli.exe config set IntelOptaneDCPMM.MemoryModePercentage 20 --imm USERID:PASSWORD@10.104.195.86

```

Where 20 stands for the percentage of capacity that is invested in system volatile memory.

3. Set the DCPMM mode.

```

onecli.exe config set IntelOptaneDCPMM.PersistentMemoryType "App Direct" --imm USERID:PASSWORD@10.104.195.86

```

Where App Direct stands for the DCPMM mode.

## - Persistent Memory Type

In App Direct Mode and Mixed Memory Mode, the DCPMMs that are connected to the same processor are by default interleaved (displayed as **App Direct**), while memory banks are used in turns. To set them as not interleaved in the Setup Utility, go to **Intel Optane DCPMMs** → **Goals** → **Persistent Memory Type [(DCPMM mode)]**, select **App Direct Not Interleaved** and reboot the system.

**Note:** Setting DCPMM App Direct capacity to not interleaved will turn the displayed App Direct regions from one region per processor to one region per DCPMM.

### Regions

After the memory percentage is set and the system is rebooted, regions for the App Direct capacity will be generated automatically. Select this option to view the App Direct regions.

## Namespaces

App Direct capacity of DCPMMs requires the following steps before it is truly available for applications.

- 1. Namespaces must be created for region capacity allocation.

- 2. Filesystem must be created and formatted for the namespaces in the operating system.

Each App Direct region can be allocated into one namespace. Create namespaces in the following operating systems:

- Windows: Use Pmem command.

- Linux: Use ndctl command.

- VMware: Reboot the system, and VMware will create namespaces automatically.

After creating namespaces for App Direct capacity allocation, make sure to create and format filesystem in the operating system so that the App Direct capacity is accessible for applications.

#### Security

Enable Security

**Attention:** By default, DCPMM security is disabled. Before enabling security, make sure all the country or local legal requirements regarding data encryption and trade compliance are met. Violation could cause legal issues.

DCPMMs can be secured with passphrases. Two types of passphrase protection scope are available for DCPMM:

Platform: Choose this option to run security operation on all the installed DCPMM units at once. A

platform passphrase is stored and automatically applied to unlock DCPMMs before operating

system starts running, but the passphrase still has to be disabled manually for secure erase.

Alternatively, enable/disable platform level security with the following commands in OneCLI:

- Enable security:

- 1. Enable security.

```

onecli.exe config set IntelOptaneDCPMM.SecurityOperation "Enable Security" --imm USERID:PASSWORD@10.104.195.86

```

2. Set the security passphrase.

```

onecli.exe config set IntelOptaneDCPMM.SecurityPassphrase "123456" --imm USERID:PASSWORD@10.104.195.86

```

Where 123456 stands for the passphrase.

- 3. Reboot the system.

- · Disable security:

- 1. Disable security.

```

onecli.exe config set IntelOptaneDCPMM.SecurityOperation "Disable Security"

--imm USERID:PASSWORD@10.104.195.86

```

2. Enter passphrase.

```

onecli.exe config set IntelOptaneDCPMM.SecurityPassphrase "123456"

--imm USERID:PASSWORD@10.104.195.86

```

- 3. Reboot the system.

- Single DCPMM: Choose this option to run security operation on one or more selected DCPMM units.

### Notes:

- Single DCPMM passphrases are not stored in the system, and security of the locked units needs to be disabled before the units are available for access or secure erase.

- Always make sure to keep records of the slot number of locked DCPMMs and corresponding passphrases. In the case the passphrases are lost or forgotten, the stored data cannot be backed up or restored, but you can contact Lenovo service for administrative secure erase.

- · After three failed unlocking attempts, the corresponding DCPMMs enter "exceeded" state with a system warning message, and the DCPMM unit can only be unlocked after the system is rebooted.

To enable passphrase, go to **Security** → **Press to Enable Security**.

Secure Frase

Note: If the DCPMMs to be secure erased are protected with a passphrase, make sure to disable security and reboot the system before performing secure erase.

Secure erase cleanses all the data that is stored in the DCPMM unit, including encrypted data. This data deletion method is recommended before returning or disposing a malfunctioning unit, or changing DCPMM mode. To perform secure erase, go to Security → Press to Secure Erase.

Alternatively, perform platform level secure erase with the following command in OneCLI:

onecli.exe config set IntelOptaneDCPMM.SecurityOperation "Secure Erase Without Passphrase" --imm USERID:PASSWORD@10.104.195.86

## DCPMM Configuration

DCPMM contains spared internal cells to stand in for the failed ones. When the spared cells are exhausted to 0%, there will be an error message, and it is advised to back up data, collect service log, and contact Lenovo support.

There will also be a warning message when the percentage reaches 1% and a selectable percentage (10% by default). When this message appears, it is advised to back up data and run DCPMM diagnostics (see https://sysmgt.lenovofiles.com/help/topic/LXPM/running\_diagnostics.html). To adjust the selectable percentage that the warning message requires, go to Intel Optane DCPMMs → DCPMM Configuration. and input the percentage.

Alternatively, change the selectable percentage with the following command in OneCLI:

```

onecli.exe config set IntelOptaneDCPMM.PercentageRemainingThresholds 20

--imm USERID:PASSWORD@10.104.195.86

```

Where 20 is the selectable percentage.

## **Update the firmware**

Several options are available to update the firmware for the server.

You can use the tools listed here to update the most current firmware for your server and the devices that are installed in the server.

**Note:** Lenovo typically releases firmware in bundles called UpdateXpress System Packs (UXSPs). To ensure that all of the firmware updates are compatible, you should update all firmware at the same time. If you are updating firmware for both the Lenovo XClarity Controller and UEFI, update the firmware for Lenovo XClarity Controller first.

Best practices related to updating firmware is available at the following location:

### http://lenovopress.com/LP0656

## Important terminology

- **In-band update**. The installation or update is performed using a tool or application within an operating system that is executing on the server's core CPU.

- Out-of-band update. The installation or update is performed by the Lenovo XClarity Controller collecting the update and then directing the update to the target subsystem or device. Out-of-band updates have no dependency on an operating system executing on the core CPU. However, most out-of-band operations do require the server to be in the S0 (Working) power state.

- On-Target update. The installation or update is initiated from an Operating System executing on the server's operating system.

- Off-Target update. The installation or update is initiated from a computing device interacting directly with the server's Lenovo XClarity Controller.

- **UpdateXpress System Packs (UXSPs)**. UXSPs are bundled updates designed and tested to provide the interdependent level of functionality, performance, and compatibility. UXSPs are server machine-type specific and are built (with firmware and device driver updates) to support specific Windows Server, Red Hat Enterprise Linux (RHEL) and SUSE Linux Enterprise Server (SLES) operating system distributions. Machine-type-specific firmware-only UXSPs are also available.

See the following table to determine the best Lenovo tool to use for installing and setting up the firmware:

**Note:** The server UEFI settings for option ROM must be set to **Auto** or **UEFI** to update firmware using Lenovo XClarity Administrator or Lenovo XClarity Essentials. For more information, see the following Tech Tip:

https://datacentersupport.lenovo.com/us/en/solutions/ht506118

| Tool                                                                                                                                                                                                                       | In-band<br>update | Out-of-<br>band<br>update | On-<br>target<br>update | Off-<br>target<br>update | Graphical user interface | Command-<br>line interface | Supports<br>UXSPs |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------|-------------------------|--------------------------|--------------------------|----------------------------|-------------------|

| Lenovo XClarity Provisioning Manager Limited to core system firmware only.                                                                                                                                                 | <b>√</b>          |                           |                         | √                        | √                        |                            | <b>√</b>          |

| Lenovo XClarity Controller Supports core system firmware and most advanced I/O option firmware updates                                                                                                                     |                   | <b>√</b>                  |                         | √                        | √                        | √                          |                   |

| Lenovo XClarity Essentials OneCLI Supports all core system firmware, I/O firmware, and installed operating system driver updates                                                                                           | <b>√</b>          | <b>√</b>                  |                         |                          |                          | √                          | <b>√</b>          |

| Lenovo XClarity Essentials UpdateXpress Supports all core system firmware, I/O firmware, and installed operating system driver updates                                                                                     | <b>√</b>          | √                         |                         |                          | √                        |                            | √                 |

| Lenovo XClarity Essentials Bootable Media Creator Supports core system firmware and I/O firmware updates. You can update the Microsoft Windows operating system, but device drivers are not included on the bootable image | <b>√</b>          |                           |                         |                          | √                        | <b>√</b>                   | <b>√</b>          |

| Lenovo XClarity Administrator Supports core system firmware and I/O firmware updates                                                                                                                                       | √                 | √                         |                         | √                        | √                        |                            |                   |

## • Lenovo XClarity Provisioning Manager

From Lenovo XClarity Provisioning Manager, you can update the Lenovo XClarity Controller firmware, the UEFI firmware, and the Lenovo XClarity Provisioning Manager software.

Note: By default, the Lenovo XClarity Provisioning Manager Graphical User Interface is displayed when you press F1. If you have changed that default to be the text-based system setup, you can bring up the Graphical User Interface from the text-based system setup interface.

Additional information about using Lenovo XClarity Provisioning Manager to update firmware is available at:

http://sysmgt.lenovofiles.com/help/topic/LXPM/platform\_update.html

## Lenovo XClarity Controller

If you need to install a specific update, you can use the Lenovo XClarity Controller interface for a specific server.

#### Notes:

To perform an in-band update through Windows or Linux, the operating system driver must be installed and the Ethernet-over-USB (sometimes called LAN over USB) interface must be enabled.

Additional information about configuring Ethernet over USB is available at:

$\underline{\text{http://sysmgt.lenovofiles.com/help/topic/com.lenovo.systems.management.xcc.doc/NN1ia\_c\_configuringUSB.html}$

If you update firmware through the Lenovo XClarity Controller, make sure that you have downloaded and installed the latest device drivers for the operating system that is running on the server.

Specific details about updating firmware using Lenovo XClarity Controller are available at:

http://sysmgt.lenovofiles.com/help/topic/com.lenovo.systems.management.xcc.doc/NN1ia\_c\_manageserverfirmware.html

## Lenovo XClarity Essentials OneCLI

Lenovo XClarity Essentials OneCLI is a collection of command line applications that can be used to manage Lenovo servers. Its update application can be used to update firmware and device drivers for your servers. The update can be performed within the host operating system of the server (in-band) or remotely through the BMC of the server (out-of-band).

Specific details about updating firmware using Lenovo XClarity Essentials OneCLI is available at:

http://sysmgt.lenovofiles.com/help/topic/toolsctr\_cli\_lenovo/onecli\_c\_update.html

## • Lenovo XClarity Essentials UpdateXpress

Lenovo XClarity Essentials UpdateXpress provides most of OneCLI update functions through a graphical user interface (GUI). It can be used to acquire and deploy UpdateXpress System Pack (UXSP) update packages and individual updates. UpdateXpress System Packs contain firmware and device driver updates for Microsoft Windows and for Linux.

You can obtain Lenovo XClarity Essentials UpdateXpress from the following location:

https://datacentersupport.lenovo.com/solutions/Invo-xpress

## Lenovo XClarity Essentials Bootable Media Creator

You can use Lenovo XClarity Essentials Bootable Media Creator to create bootable media that is suitable for applying firmware updates, running preboot diagnostics, and deploying Microsoft Windows operating systems.

You can obtain Lenovo XClarity Essentials BoMC from the following location:

https://datacentersupport.lenovo.com/solutions/Invo-bomc

## Lenovo XClarity Administrator

If you are managing multiple servers using the Lenovo XClarity Administrator, you can update firmware for all managed servers through that interface. Firmware management is simplified by assigning firmware-compliance policies to managed endpoints. When you create and assign a compliance policy to managed endpoints, Lenovo XClarity Administrator monitors changes to the inventory for those endpoints and flags any endpoints that are out of compliance.

Specific details about updating firmware using Lenovo XClarity Administrator are available at:

http://sysmgt.lenovofiles.com/help/topic/com.lenovo.lxca.doc/update\_fw.html

# Chapter 2. DCPMM installation order for ThinkSystem compute nodes

Follow the population table in this section to install the DCPMMs and DIMMs.

## **SN550 DCPMM and DIMM configuration**

Memory performance depends on several variables, such as memory mode, memory speed, memory ranks, memory population and processor.

Information about optimizing memory performance and configuring memory is available at the Lenovo Press website:

https://lenovopress.com/servers/options/memory

In addition, you can take advantage of a memory configurator, which is available at the following site:

http://1config.lenovo.com/#/memory\_configuration

Specific information about the required installation order of memory modules in your compute node based on the system configuration and memory mode that you are implementing is shown below.

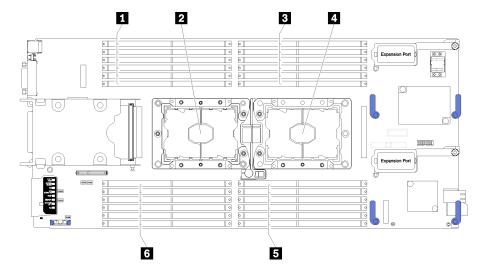

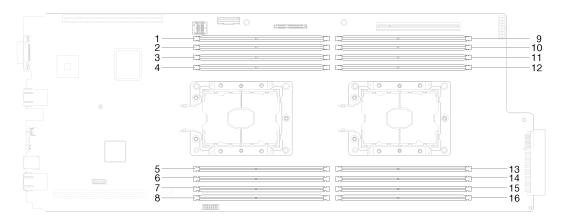

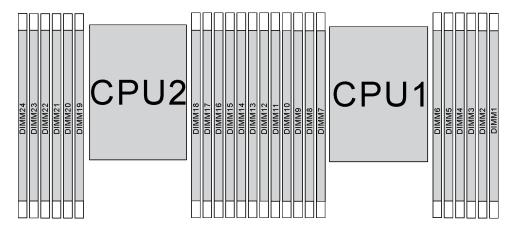

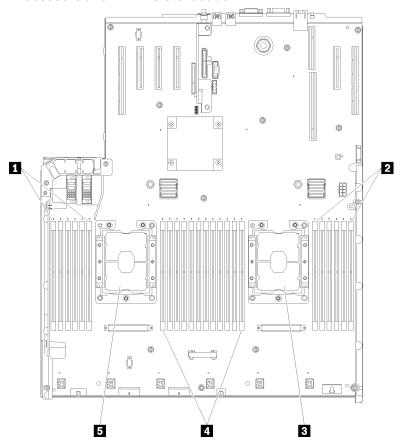

Figure 1. DIMM and processor location

Table 1. DIMM and processor location

| ☐ DIMM connectors 13–18 | Processor socket 1      |

|-------------------------|-------------------------|

| 2 Processor socket 2    | 5 DIMM connectors 7–12  |

| DIMM connectors 1–6     | ₫ DIMM connectors 19–24 |

Table 2. Channel and slot information of DIMMs around processor 1 and 2

The memory-channel configuration table is a three-column table that shows the relationship between the processors, memory controllers, memory channels, slot number and the DIMM connectors.

© Copyright Lenovo 2019

Table 2. Channel and slot information of DIMMs around processor 1 and 2 (continued)

| Integrated Memory Controller (iMC) | Controller 0 |           |    |           |    |           |    | Controller 1 |    |           |    |       |  |  |  |

|------------------------------------|--------------|-----------|----|-----------|----|-----------|----|--------------|----|-----------|----|-------|--|--|--|

| Channel                            | Char         | Channel 2 |    | Channel 1 |    | Channel 0 |    | Channel 0    |    | Channel 1 |    | nel 2 |  |  |  |

| Slot                               | 0            | 0 1       |    | 1         | 0  | 1         | 1  | 0            | 1  | 0         | 1  | 0     |  |  |  |

| DIMM connector (processor 1)       | 1            | 2         | 3  | 4         | 5  | 6         | 7  | 8            | 9  | 10        | 11 | 12    |  |  |  |

| DIMM connector (processor 2)       | 24           | 23        | 22 | 21        | 20 | 19        | 18 | 17           | 16 | 15        | 14 | 13    |  |  |  |

## **SN550 Memory Mode**

Memory modules must be installed in a specific order based on the memory configuration that you implement on your node. Below is the information of Memory Mode.

Note: Before installing DCPMM, refer to "SN550 DCPMM and DIMM configuration" on page 9 for the requirements.

Table 3. Three categories of DIMM

| DIMM Category | DDR4 Type | Capacity                            |

|---------------|-----------|-------------------------------------|

| D1            | RDIMM     | All density of DDR4 more than 32 GB |

| D2            | RDIMM     | 16 GB or 32 GB RDIMM                |

Following are all the combinations that are supported in this solution.

## **Memory Mode with one processor**

Table 4. Memory Mode with one processor

D1-D2: Refer to Table 3 "Three categories of DIMM" on page 10. P: Only DC Persistent Memory Module (DCPMM) can be installed on the corresponding DIMM slots. Configuration Processor 1 1 2 4 5 6 7 8 9 3 10 11 12 D2 D2 Ρ Р D2 2 DCPMMs and 6 DIMMs D2 D2 D2 4 DCPMMs and 6 DIMMs D1 D1 Ρ D1 Р Ρ D1 Ρ D1 D1 Р Р Р 6 DCPMMs and 6 DIMMs D1 Ρ D1 D1 D1 Ρ D1 Ρ D1 Р Ρ 2 DCPMMs and 4 DIMMs D1 D1 D1 D1

Note: 2 DCPMMs and 4 DIMMs: one DIMM per processor channel configuration.

Table 5. Supported DCPMM capacity in Memory Mode with one processor

| Total<br>DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |

|-----------------|----------------|------------------|--------------|--------------|--------------|

|                 |                | L                |              | √            | √            |

| 2               | 6              | М                |              | √            | √            |

|                 |                | Other            |              | √            |              |

| 4               | 6              | L                |              | √            | √            |

Table 5. Supported DCPMM capacity in Memory Mode with one processor (continued)

|   |   | М     |   | √ |   |

|---|---|-------|---|---|---|

|   |   | Other |   |   |   |

|   |   | L     | √ | √ | √ |

| 6 | 6 | М     | √ | √ |   |

|   |   | Other | √ |   |   |

|   |   | L     |   | √ | √ |

| 2 | 4 | М     |   | √ | √ |

|   |   | Other |   | √ |   |

## **Memory Mode with two processors**

Table 6. Memory Mode with two processors

D1-D2: Refer to Table 3 "Three categories of DIMM" on page 10.

**P**: Only DC Persistent Memory Module (DCPMM) can be installed on the corresponding DIMM slots.

| Configuration             |    | Processor 1 |    |   |    |   |   |    |   |    |    |    |    | Processor 2 |    |    |    |    |    |    |    |    |    |    |

|---------------------------|----|-------------|----|---|----|---|---|----|---|----|----|----|----|-------------|----|----|----|----|----|----|----|----|----|----|

|                           | 1  | 2           | 3  | 4 | 5  | 6 | 7 | 8  | 9 | 10 | 11 | 12 | 13 | 14          | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 4 DCPMMs and<br>12 DIMMs  | D2 |             | D2 |   | D2 | Р | Р | D2 |   | D2 |    | D2 | D2 |             | D2 |    | D2 | Р  | Р  | D2 |    | D2 |    | D2 |

| 8 DCPMMs and<br>12 DIMMs  | D1 |             | D1 | Р | D1 | Р | Р | D1 | Р | D1 |    | D1 | D1 |             | D1 | Р  | D1 | Р  | Р  | D1 | P  | D1 |    | D1 |

| 12 DCPMMs<br>and 12 DIMMs | D1 | Р           | D1 | Р | D1 | Р | Р | D1 | Р | D1 | Р  | D1 | D1 | Р           | D1 | Р  | D1 | Р  | Р  | D1 | Р  | D1 | Р  | D1 |

| 4 DCPMMs and<br>8 DIMMs   | Р  |             | D1 |   | D1 |   |   | D1 |   | D1 |    | Р  | Р  |             | D1 |    | D1 |    |    | D1 |    | D1 |    | Р  |

Note: 4 DCPMMs and 8 DIMMs: one DIMM per processor channel configuration.

Table 7. Supported DCPMM capacity in Memory Mode with two processors

| Total<br>DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |

|-----------------|----------------|------------------|--------------|--------------|--------------|

|                 |                | L                |              | √            | √            |

| 4               | 12             | М                |              | √            | √            |

|                 |                | Other            |              | √            |              |

|                 |                | L                |              | √            | √            |

| 8               | 12             | М                |              | √            |              |

|                 |                | Other            |              |              |              |

|                 |                | L                | √            | $\checkmark$ | √            |

| 12              | 12             | М                | √            | √            |              |

|                 |                | Other            | √            |              |              |

| 4               | 8              | L                |              | √            | √            |

Table 7. Supported DCPMM capacity in Memory Mode with two processors (continued)

| М     | √ | $\checkmark$ |

|-------|---|--------------|

| Other | √ |              |

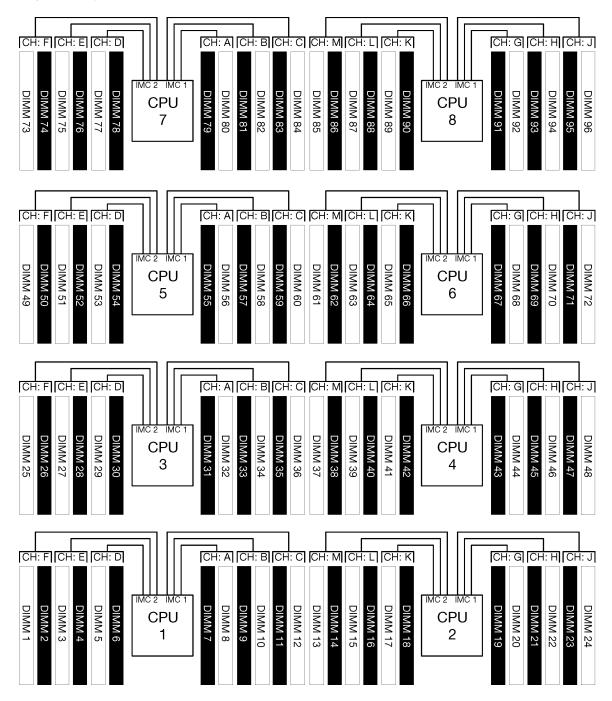

## **SN850 DCPMM and DIMM configuration**

In Memory Mode, DCPMMs act as volatile system memory, while DRAM DIMMs act as cache. Only DCPMM capacity is displayed as system memory in this mode.

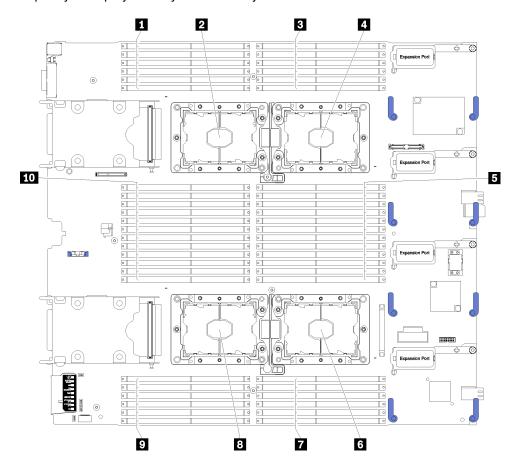

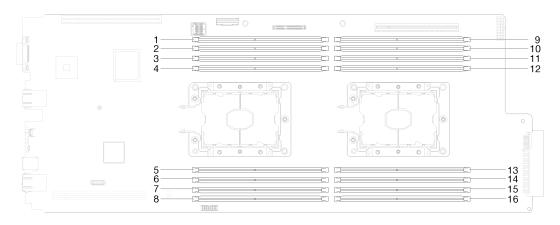

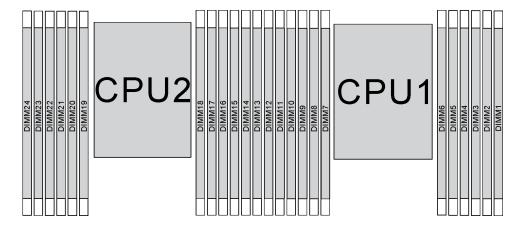

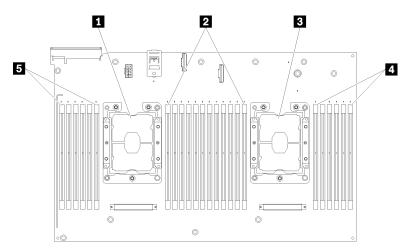

Figure 2. Processor and memory module layout

Table 8. Processor and memory module layout

| ☐ DIMM 25 – 30       | 6 Processor socket 2 |

|----------------------|----------------------|

| 2 Processor socket 3 | 7 DIMM 19 – 24       |

| <b>■</b> DIMM 1 – 6  | 8 Processor socket 4 |

| ☐ Processor socket 1 | 7 DIMM 43 – 48       |

| ☐ DIMM 7 – 18        | 10 DIMM 31 – 42      |

Table 9. Channel and slot information of DIMMs around processor 1 and 2

| Memory controllers         |      |           | Contr | oller 0             |    | Controller 1 |    |           |    |           |    |    |

|----------------------------|------|-----------|-------|---------------------|----|--------------|----|-----------|----|-----------|----|----|

| Channels                   | Char | Channel 2 |       | Channel 1 Channel 0 |    | Channel 0    |    | Channel 1 |    | Channel 2 |    |    |

| Slots                      | 0    | 0 1       |       | 1                   | 0  | 1            | 1  | 0         | 1  | 0         | 1  | 0  |

| DIMM numbers (processor 1) | 1    | 1 2       |       | 4                   | 5  | 6            | 7  | 8         | 9  | 10        | 11 | 12 |

| DIMM numbers (processor 2) | 13   | 14        | 15    | 16                  | 17 | 18           | 19 | 20        | 21 | 22        | 23 | 24 |

Table 10. Channel and slot information of DIMMs around processor 3 and 4

| Memory controllers         |           |    | Contr     | oller 1 |           |    |           |    | Conti     | roller 0 |           |    |

|----------------------------|-----------|----|-----------|---------|-----------|----|-----------|----|-----------|----------|-----------|----|

| Channels                   | Channel 2 |    | Channel 1 |         | Channel 0 |    | Channel 0 |    | Channel 1 |          | Channel 2 |    |

| Slots                      | 0         | 1  | 0         | 1       | 0         | 1  | 1         | 0  | 1         | 0        | 1         | 0  |

| DIMM numbers (processor 3) | 25        | 26 | 27        | 28      | 29        | 30 | 31        | 32 | 33        | 34       | 35        | 36 |

| DIMM numbers (processor 4) | 37        | 38 | 39        | 40      | 41        | 42 | 43        | 44 | 45        | 46       | 47        | 48 |

The memory mode DIMM population sequences for each supported processor configuration are:

- "SN850 Memory Mode with two processors" on page 14

- "SN850 Memory Mode with four processors" on page 16

## **SN850 Memory Mode with two processors**

Memory module installation order for Memory Mode with two processors installed in the compute node.

Table 11. Three categories of DIMM

| DIMM Category | DDR4 Type | Capacity                            |

|---------------|-----------|-------------------------------------|

| D1            | RDIMM     | All density of DDR4 more than 32 GB |

| D2            | RDIMM     | 16 GB or 32 GB RDIMM                |

The following table shows the DIMM population sequence for Memory Mode when two processors are installed.

**Note:** When adding one or more DIMMs during a memory upgrade, you might need to move other DIMMs that are already installed to new locations.

Table 12. Memory Mode with two processors

D1-D2: Refer to Table 11 "Three categories of DIMM" on page 14. P: Only DC Persistent Memory Module (DCPMM) can be installed on the corresponding DIMM slots. Configuration Processor 1 Processor 2 7 11 13 1 2 3 4 6 8 9 10 12 14 15 16 17 18 19 20 21 22 23 24 5 Р 4 DCPMMs and D2 D2 D2 Ρ D2 D2 D2 D2 D2 D2 Ρ Ρ D2 D2 D2 12 DIMMs 8 DCPMMs and D1 D1 Ρ D1 Ρ Ρ D1 Ρ D1 D1 D1 D1 Ρ D1 Ρ Ρ D1 Ρ D1 D1 12 DIMMs Ρ Р Р Ρ D1 Ρ Ρ Р Ρ Ρ D1 D1 Ρ D1 D1 D1 Ρ D1 Ρ D1 D1 D1 12 DCPMMs D1 D1 and 12 DIMMs Ρ Ρ 4 DCPMMs and D1 D1 D1 D1 Ρ Ρ D1 D1 D1 D1 8 DIMMs

Note: 4 DCPMMs and 8 DIMMs: one DIMM per processor channel configuration.

Table 13. Supported DCPMM capacity in Memory Mode with two processors

| Total<br>DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |

|-----------------|----------------|------------------|--------------|--------------|--------------|

|                 |                | L                | √            | √            | √            |

| 4               | 12             | М                | √            | √            | √            |

|                 |                | Other            | √            | √            |              |

|                 |                | L                | √            | √            | √            |

| 8               | 12             | М                | √            | √            |              |

|                 |                | Other            | √            |              |              |

|                 |                | L                | √            | √            | √            |

| 12              | 12             | М                | √            | √            |              |

|                 |                | Other            | √            |              |              |

Table 13. Supported DCPMM capacity in Memory Mode with two processors (continued)

|   |   | L     | √ | √ | √        |

|---|---|-------|---|---|----------|

| 4 | 8 | М     | √ | √ | <b>√</b> |

|   |   | Other | √ | √ |          |

## **SN850 Memory Mode with four processors**

Memory module installation order for Memory Mode with four processors installed in the compute node.

Table 14. Three categories of DIMM

| DIMM Category | DDR4 Type | Capacity                           |

|---------------|-----------|------------------------------------|

| D1            | RDIMM     | All density of DDR4 more than 32GB |

| D2            | RDIMM     | 16GB or 32GB RDIMM                 |

The following tables show the DIMM population sequence for independent Memory Mode when four processors are installed.

Note: When adding one or more DIMMs during a memory upgrade, you might need to move other DIMMs that are already installed to new locations.

Table 15. Memory Mode with four processors (Processors 1 and 2)

| D1-D2: Refer to           | 11-D2: Refer to Table 14 "Three categories of DIMM" on page 16.                               |   |    |   |    |   |   |    |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---------------------------|-----------------------------------------------------------------------------------------------|---|----|---|----|---|---|----|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| P: Only DC Persis         | e: Only DC Persistent Memory Module (DCPMM) can be installed on the corresponding DIMM slots. |   |    |   |    |   |   |    |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| Configuration             | Configuration Processor 1 Processor 2                                                         |   |    |   |    |   |   |    |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                           | 1                                                                                             | 2 | 3  | 4 | 5  | 6 | 7 | 8  | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 8 DCPMMs and<br>24 DIMMs  | D2                                                                                            |   | D2 |   | D2 | Р | Р | D2 |   | D2 |    | D2 | D2 |    | D2 |    | D2 | Р  | Р  | D2 |    | D2 |    | D2 |

| 16 DCPMMs<br>and 24 DIMMs | D1                                                                                            |   | D1 | Р | D1 | Р | Р | D1 | Р | D1 |    | D1 | D1 |    | D1 | Р  | D1 | Р  | Р  | D1 | P  | D1 |    | D1 |

| 24 DCPMMs<br>and 24 DIMMs | D1                                                                                            | Р | D1 | Р | D1 | Р | Р | D1 | Р | D1 | P  | D1 | D1 | Р  | D1 | Р  | D1 | Р  | Р  | D1 | P  | D1 | Р  | D1 |

| 8 DCPMMs and<br>16 DIMMs  | Р                                                                                             |   | D1 |   | D1 |   |   | D1 |   | D1 |    | Р  | Р  |    | D1 |    | D1 |    |    | D1 |    | D1 |    | Р  |

Note: 8 DCPMMs and 16 DIMMs: one DIMM per processor channel configuration.

Related DIMM population sequences for four processor systems:

To continue populating processor 3 and 4 DIMMs for system, see Table 16 "Memory Mode with four processors (Processors 3 and 4)" on page 17.

Table 16. Memory Mode with four processors (Processors 3 and 4)

D1-D2: Refer to Table 14 "Three categories of DIMM" on page 16. P: Only DC Persistent Memory Module (DCPMM) can be installed on the corresponding DIMM slots. Configuration Processor 3 Processor 4 25 26 27 28 29 30 31 32 | 33 | 34 35 36 37 38 39 40 41 42 45 46 47 48 43 44 8 DCPMMs and D2 D2 D2 Р Р D2 D2 D2 D2 D2 D2 Р Ρ D2 D2 D2 24 DIMMs 16 DCPMMs D1 D1 Ρ D1 Ρ Ρ D1 Ρ D1 D1 D1 D1 Ρ D1 Ρ Ρ D1 Ρ D1 D1 and 24 DIMMs Ρ Ρ D1 Ρ D1 Ρ D1 Р D1 D1 D1 Ρ Р Ρ D1 Р D1 24 DCPMMs D1 Ρ D1 Ρ D1 D1 Ρ and 24 DIMMs 8 DCPMMs and Ρ D1 D1 D1 D1 Ρ Ρ D1 D1 D1 D1 Ρ 16 DIMMs

Note: 8 DCPMMs and 16 DIMMs: one DIMM per processor channel configuration.

Related DIMM population sequences for four processor systems:

To continue populating processor 1 and 2 DIMMs for system, see Table 15 "Memory Mode with four processors (Processors 1 and 2)" on page 16.

Table 17. Supported DCPMM capacity in Memory Mode with four processors

| Total DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |

|--------------|----------------|------------------|--------------|--------------|--------------|

|              |                | L                | √            | √            | √            |

| 8            | 24             | M                | $\checkmark$ | √            | √            |

|              |                | Other            | √            | √            |              |

|              |                | L                | $\checkmark$ | √            | √            |

| 16           | 24             | М                | √            | √            |              |

|              |                | Other            | √            |              |              |

|              |                | L                | √            | √            | √            |

| 24           | 24             | М                | √            | √            |              |

|              |                | Other            | √            |              |              |

|              |                | L                | √            | √            | √            |

| 8            | 16             | М                | √            | √            | √ ·          |

|              |                | Other            | √            | √            |              |

# Chapter 3. DCPMM installation order for ThinkSystem highdensity servers

Follow the population table in this section to install the DCPMMs and DIMMs.

## SD530 DCPMM and DIMM configuration

This section contains information of how to install DCPMMs and DRAM DIMMs properly.

#### Notes:

- To verify if the presently installed processors support DCPMMs, examine the four digits in the processor description. Only the processor with description meeting both of the following requirements support DCPMMs.

- The first digit is **5** or a larger number.

Note: The only exception to this rule is *Intel Xeon Silver 4215*, which also supports DCPMM.

- The second digit is 2.

Example: Intel Xeon 5215L and Intel Xeon Platinum 8280M

If the presently installed processors do not support DCPMMs, replace them with the processors that support DCPMMs.

- Supported memory capacity range varies with the following types of processors.

- Large memory tier (L): The processors with L after the four digits (for example: Intel Xeon 5215L)

- Medium memory tier (M): The processors with M after the four digits (for example: Intel Xeon Platinum 8280M)

- Other: Other processors that support DCPMMs (for example: Intel Xeon Gold 5222)

In addition, you can take advantage of a memory configurator, which is available at the following site:

http://1config.lenovo.com/#/memory\_configuration

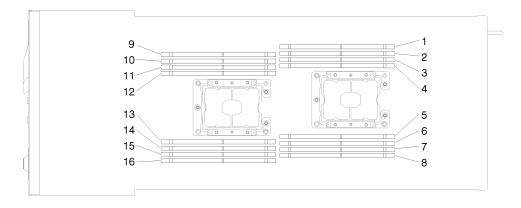

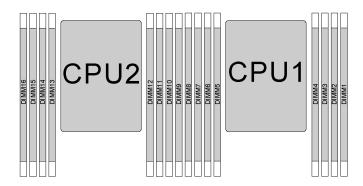

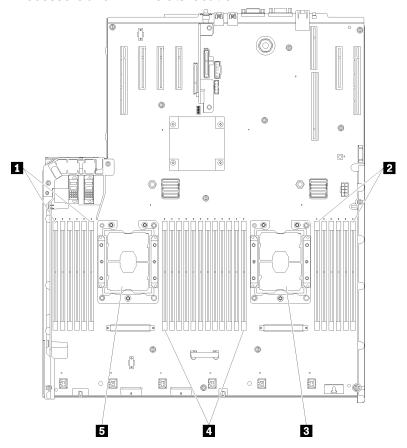

The following illustration shows the location of the DIMM connectors on the system board.

Figure 3. The location of the DIMM connectors on the system board

© Copyright Lenovo 2019

## **SD530 Memory Mode**

In this mode, DCPMMs act as volatile system memory, while DRAM DIMMs act as cache.

## Memory Mode - one processor

Table 18. Memory Mode with one processor

| <ul> <li>D: DRAM DIMMs</li> </ul> |

|-----------------------------------|

|-----------------------------------|

• P: DC Persistent Memory Module (DCPMM)

| Configuration        |   |   |   | Proce | essor 1 |   |   |   |

|----------------------|---|---|---|-------|---------|---|---|---|

|                      | 1 | 2 | 3 | 4     | 5       | 6 | 7 | 8 |

| 2 DCPMMs and 6 DIMMs | D | D | D | Р     | Р       | D | D | D |

Table 19. Supported DCPMM capacity in Memory Mode with one processor

| Total DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |

|--------------|----------------|------------------|--------------|--------------|--------------|

|              |                | L                |              | √            | √            |

| 2            | 6              | М                |              | √            | √            |

|              |                | Other            |              | √            |              |

## **Memory Mode - two processors**

Table 20. Memory Mode with two processors

| <ul><li>D: DRAM DIMMs</li><li>P: DC Persistent Men</li></ul> |                                         |  |  |  |  |  |  |  |  |    |  |  |  |

|--------------------------------------------------------------|-----------------------------------------|--|--|--|--|--|--|--|--|----|--|--|--|

| Configuration Processor 1 Processor 2                        |                                         |  |  |  |  |  |  |  |  |    |  |  |  |

|                                                              | 1 2 3 4 5 6 7 18 9 10 11 12 13 14 15 16 |  |  |  |  |  |  |  |  | 16 |  |  |  |

| 4 DCPMMs and 12 D D D P P D D D D D P P D D D D D D D        |                                         |  |  |  |  |  |  |  |  |    |  |  |  |

Table 21. Supported DCPMM capacity in Memory Mode with two processors

| Total<br>DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |

|-----------------|----------------|------------------|--------------|--------------|--------------|

|                 |                | L                |              | √            | √            |

| 4               | 12             | М                |              | √            |              |

|                 |                | Other            |              |              |              |

# **SD530 App Direct Mode**

In this mode, DCPMMs act as independent and persistent memory resources directly accessible by specific applications, and DRAM DIMMs act as system memory.

## **App Direct Mode - one processor**

Table 22. App Direct Mode with one processor

- D: DRAM DIMMs

- P: DC Persistent Memory Module (DCPMM)

| Configuration        |   | Processor 1 |   |   |   |   |   |   |  |

|----------------------|---|-------------|---|---|---|---|---|---|--|

|                      | 1 | 2           | 3 | 4 | 5 | 6 | 7 | 8 |  |

| 1 DCPMM and 6 DIMMs  | D | D           | D |   | Р | D | D | D |  |

| 2 DCPMMs and 6 DIMMs | D | D           | D | Р | Р | D | D | D |  |

Table 23. Supported DCPMM capacity in App Direct Mode with one processor

| Total<br>DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |

|-----------------|----------------|------------------|--------------|--------------|--------------|

|                 |                | L                | <b>√</b>     | √            | √            |

| 1               | 6              | М                | √            | √            | √            |

|                 |                | Other            | √            | √            | √            |

|                 |                | L                | <b>√</b>     | √            |              |

| 2 6             | 6              | М                | √            | √            |              |

|                 |                | Other            | √            | √            |              |

## **App Direct Mode - two processors**

Table 24. App Direct Mode with two processors

D: DRAM DIMMs • P: DC Persistent Memory Module (DCPMM) Configuration Processor 2 Processor 1 8 2 10 11 12 13 14 15 16 1 DCPMM and 12 D D D D D D D D D D D D DIMMs 2 DCPMMs and 12 D D Ρ D D D D Ρ D D D D D D DIMMs 4 DCPMMs and 12 D D D Ρ Ρ D D D D D D Ρ Ρ D D D **DIMMs**

Table 25. Supported DCPMM capacity in App Direct Mode with two processors

| Total<br>DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |

|-----------------|----------------|------------------|--------------|--------------|--------------|

|                 |                | L                | √            | √            | √            |

| 1               | 1 12           | М                | √            | √            | √            |

|                 |                | Other            | √            | √            | √            |

| 2               | 10             | L                | √            | √            | √            |

| 2               | 2   12         | М                | √            | √            | √            |

Table 25. Supported DCPMM capacity in App Direct Mode with two processors (continued)

|   |    | Other | √ | √ |   |

|---|----|-------|---|---|---|

|   |    | L     | √ | √ | √ |

| 4 | 12 | М     | √ | √ |   |

|   |    | Other | √ |   |   |

## **SD530 Mixed Memory Mode**

In this mode, some percentage of DCPMM capacity is directly accessible to specific applications (App Direct), while the rest serves as system memory. The App Direct part of DCPMM is displayed as persistent memory, while the rest of DCPMM capacity is displayed as system memory. DRAM DIMMs act as cache in this mode.

## **Mixed Memory Mode - one processor**

Table 26. Mixed Memory Mode with one processor

| D: DRAM DIMMs     P: DC Persistent Memory Module (DCPMM) |             |   |   |   |   |   |   |   |

|----------------------------------------------------------|-------------|---|---|---|---|---|---|---|

| Configuration                                            | Processor 1 |   |   |   |   |   |   |   |

|                                                          | 1           | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 2 DCPMMs and 6 DIMMs                                     | D           | D | D | Р | Р | D | D | D |

Table 27. Supported DCPMM capacity in Mixed Memory Mode with one processor

| Total<br>DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |

|-----------------|----------------|------------------|--------------|--------------|--------------|

|                 |                | L                |              |              | √            |

| 2               | 6              | M                |              |              | √            |

|                 |                | Other            |              |              |              |

### Mixed Memory Mode - two processors

Table 28. Mixed Memory Mode with two processors

| <ul> <li>D: DRAM DIMMs</li> <li>P: DC Persistent Memory Module (DCPMM)</li> </ul> |                                       |   |   |   |   |   |   |    |   |    |    |    |    |    |    |    |

|-----------------------------------------------------------------------------------|---------------------------------------|---|---|---|---|---|---|----|---|----|----|----|----|----|----|----|

| Configuration                                                                     | Configuration Processor 1 Processor 2 |   |   |   |   |   |   |    |   |    |    |    |    |    |    |    |

|                                                                                   | 1                                     | 2 | 3 | 4 | 5 | 6 | 7 | 18 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| DCPMMs and 12 D D D P P D D D D P P D D D D D D D D                               |                                       |   |   |   |   |   |   |    |   |    |    |    |    |    |    |    |

Table 29. Supported DCPMM capacity in Mixed Memory Mode with two processors

| Total DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |

|--------------|----------------|------------------|--------------|--------------|--------------|

| 4            | 12             | L                |              |              | √            |

| 7            | 12             | М                |              |              |              |

Table 29. Supported DCPMM capacity in Mixed Memory Mode with two processors (continued)

|  | Other |  |  |

|--|-------|--|--|

|  |       |  |  |

## SD650 DCPMM and DIMM configuration

This section contains information of how to install DC Persistent Memory Module (DCPMM) and DRAM DIMMs.

For more information about the processors compatibility, see <a href="http://www.lenovo.com/us/en/serverproven/">http://www.lenovo.com/us/en/serverproven/</a>.

- To verify if the presently installed processors support DCPMMs, examine the four digits in the processor description. Only the processors with description meeting both of the following requirements support DCPMMs.

- The first digit is **6** or a larger number.

- The second digit is 2.

Example: Intel Xeon 6262V and Intel Xeon Platinum 8260M

If the presently installed processors do not support DCPMMs, replace them with the processors that support DCPMMs.

- Supported memory capacity range varies with the following types of DCPMMs.

- Medium memory tier (M): The processors with M after the four digits (for example: Intel Xeon Platinum 8260M) support up to 2 TB of memory capacity per processor

- No suffix: Other processors that support DCPMMs (for example: Intel Xeon Gold 6230) support up to 1 TB of memory capacity per processor

The following illustration shows the location of the DIMM connectors on the system board.

Figure 4. The location of the DIMM connectors on the system board

## SD650 DCPMM installation order

This section contains information of how to install DC Persistent Memory Module (DCPMM) and DRAM DIMMs.

For more information about the processors compatibility, see <a href="http://www.lenovo.com/us/en/serverproven/">http://www.lenovo.com/us/en/serverproven/</a>.

To verify if the presently installed processors support DCPMMs, examine the four digits in the processor description. Only the processors with description meeting both of the following requirements support DCPMMs.

- The first digit is 6 or a larger number.

- The second digit is 2.

Example: Intel Xeon 6262V and Intel Xeon Platinum 8260M

If the presently installed processors do not support DCPMMs, replace them with the processors that support DCPMMs.

- Supported memory capacity range varies with the following types of DCPMMs.

- Medium memory tier (M): The processors with M after the four digits (for example: Intel Xeon Platinum 8260M) support up to 2 TB of memory capacity per processor

- No suffix: Other processors that support DCPMMs (for example: Intel Xeon Gold 6230) support up to 1

TB of memory capacity per processor

The following illustration shows the location of the DIMM connectors on the system board.

Figure 5. The location of the DIMM connectors on the system board

Table 30. Supported DCPMM capacity in DCPMM population configuration

|                 |                |                     | App direct mode |              |              |

|-----------------|----------------|---------------------|-----------------|--------------|--------------|

| Total<br>DCPMMs | Total<br>DIMMs | Processor<br>Family | 128 GB DCPMM    | 256 GB DCPMM | 512 GB DCPMM |

| 1               | 12             | М                   | √               | √            | √            |

|                 |                | No suffix           | √               | √            | √            |

| 2               | 12             | М                   | √               | √            | √            |

|                 |                | No suffix           | √               | √            | √<br>Note 1  |

| 4               | 12             | М                   | √               | √            | √            |

|                 |                | No suffix           | √               | √<br>Note 2  |              |

#### Notes:

- 1. 12x128 GB 3DS RDIMM + 2x512 GB DCPMM is not supported.

- 2. 12x128 GB 3DS RDIMM + 4x256 GB DCPMM is not supported.

|                 | Memory mode    |                     |              |              |              |  |  |  |  |  |

|-----------------|----------------|---------------------|--------------|--------------|--------------|--|--|--|--|--|

| Total<br>DCPMMs | Total<br>DIMMs | Processor<br>Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |  |  |  |  |  |

Table 30. Supported DCPMM capacity in DCPMM population configuration (continued)

| 4                 | 12             | М                   | √            | √            | √            |  |  |  |  |  |

|-------------------|----------------|---------------------|--------------|--------------|--------------|--|--|--|--|--|

|                   |                | No suffix           | √            | √            |              |  |  |  |  |  |

| Mixed memory mode |                |                     |              |              |              |  |  |  |  |  |

| Total<br>DCPMMs   | Total<br>DIMMs | Processor<br>Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |  |  |  |  |  |

| 4                 | 12             | М                   | √            | √            | √            |  |  |  |  |  |

|                   |                | No suffix           | √            | √            |              |  |  |  |  |  |

To install DC Persistent Memory Module (DCPMM), refer to the following combinations:

- DCPMM population sequence Memory mode

- DCPMM population sequence App direct mode

- DCPMM population sequence Mix memory mode

## **DCPMM** installation order

DCPMMs shall only be installed on DIMM3, DIMM6, DIMM11 and DIMM14.

Table 31. DCPMM population sequence - Memory mode

|                | DCPMM population sequence - Memory mode                                                                                                                                                                     |    |    |   |      |         |   |   |   |    |    |    |      |         |    |    |   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|---|------|---------|---|---|---|----|----|----|------|---------|----|----|---|

|                | Note: D2: It represents RDIMMs (DIMM density =16GB or 32GB) can be installed on the corresponding DIMM slots. P: Only DC Persistent Memory Module (DCPMM) can be installed on the corresponding DIMM slots. |    |    |   |      |         |   |   |   |    |    |    |      |         |    |    |   |

|                | Processor 1 Processor 2                                                                                                                                                                                     |    |    |   |      |         |   |   |   |    |    |    |      |         |    |    |   |

| Operation      | Con-<br>figura-                                                                                                                                                                                             |    |    |   | DIMI | VI slot |   |   |   |    |    |    | DIMI | /I slot |    |    |   |

| mode           | tion                                                                                                                                                                                                        | 8  | 7  | 6 | 5    | 4       | 3 | 2 | 1 | 16 | 15 | 14 | 13   | 12      | 11 | 10 | 9 |

| Memory<br>mode | 4 AEPs<br>and 12<br>DIMMs                                                                                                                                                                                   | D2 | D2 |   |      |         |   |   |   |    |    |    |      |         |    |    |   |

Table 32. DCPMM population sequence - App direct mode

## DCPMM population sequence - App direct mode

#### Note:

D1: It represents RDIMMs (DIMM density ≥16GB) can be installed on the corresponding DIMM slots.

P: Only DC Persistent Memory Module (DCPMM) can be installed on the corresponding DIMM slots.

|                                                                                     |                           |    | Processor 1 |   |      |         |   |    |    |    | Processor 2 |    |      |         |    |    |    |  |

|-------------------------------------------------------------------------------------|---------------------------|----|-------------|---|------|---------|---|----|----|----|-------------|----|------|---------|----|----|----|--|

| Operation                                                                           | Con-<br>figura-           |    |             |   | DIMI | VI slot |   |    |    |    |             |    | DIMI | /I slot |    |    |    |  |

| mode                                                                                | tion                      | 8  | 7           | 6 | 5    | 4       | 3 | 2  | 1  | 16 | 15          | 14 | 13   | 12      | 11 | 10 | 9  |  |

| App direct<br>mode (not<br>interleaved)                                             | 1 AEP<br>and 12<br>DIMMs  | D1 | D1          | Р | D1   | D1      |   | D1 | D1 | D1 | D1          |    | D1   | D1      |    | D1 | D1 |  |

| App direct<br>mode +<br>Mirroring<br>mode (not<br>interleaved)                      | 1 AEP<br>and 12<br>DIMMs  | D1 | D1          | Р | D1   | D1      |   | D1 | D1 | D1 | D1          |    | D1   | D1      |    | D1 | D1 |  |

| App direct<br>mode (not<br>interleaved)                                             | 2 AEPs<br>and 12<br>DIMMs | D1 | D1          | Р | D1   | D1      |   | D1 | D1 | D1 | D1          | Р  | D1   | D1      |    | D1 | D1 |  |

| App direct<br>mode +<br>Mirroring<br>mode (not<br>interleaved)                      | 2 AEPs<br>and 12<br>DIMMs | D1 | D1          | Р | D1   | D1      |   | D1 | D1 | D1 | D1          | Р  | D1   | D1      |    | D1 | D1 |  |

| App direct<br>mode<br>(interleaved<br>or not<br>interleaved)                        |                           | D1 | D1          | Р | D1   | D1      | Р | D1 | D1 | D1 | D1          | Р  | D1   | D1      | Р  | D1 | D1 |  |

| App direct<br>mode +<br>Mirroring<br>mode<br>(interleaved<br>or not<br>interleaved) |                           | D1 | D1          | Р | D1   | D1      | Р | D1 | D1 | D1 | D1          | Р  | D1   | D1      | Р  | D1 | D1 |  |

Table 33. DCPMM population sequence - Mix memory mode

## DCPMM population sequence - Mix memory mode

#### Note:

D3: It represents RDIMMs (DIMM density ≥16GB, no 3DS LRDIMM) can be installed on the corresponding DIMM

P: Only DC Persistent Memory Module (DCPMM) can be installed on the corresponding DIMM slots.

|                                                                 |                 |   |    |   | Proce | ocessor 1 |   |    |    | Processor 2 |    |    |      |         |    |    |    |

|-----------------------------------------------------------------|-----------------|---|----|---|-------|-----------|---|----|----|-------------|----|----|------|---------|----|----|----|

| Operation                                                       | Con-<br>figura- |   |    |   | DIMI  | VI slot   |   |    |    |             |    |    | DIMN | /I slot |    |    |    |

| mode                                                            | tion            | 8 | 7  | 6 | 5     | 4         | 3 | 2  | 1  | 16          | 15 | 14 | 13   | 12      | 11 | 10 | 9  |

| Mix<br>memory<br>mode<br>(interleaved<br>or not<br>interleaved) |                 |   | D3 | Р | D3    | D3        | Р | D3 | D3 | D3          | D3 | Р  | D3   | D3      | Р  | D3 | D3 |

# Chapter 4. DCPMM installation order for ThinkSystem rack servers

Follow the population table in this section to install the DCPMMs and DIMMs.

## SR570 DCPMM and DIMM configuration

Memory modules must be installed in a specific order based on the memory configuration that you implement on your server.

Your server has 16 memory slots, and supports the following types of memory modules depending on the processors installed:

- For Intel Xeon Skylake processors:

- TruDDR4 2666, single-rank or dual-rank, 8 GB/16 GB/32 GB RDIMMs

- TruDDR4 2666, quad-rank, 64 GB LRDIMMs

- For Intel Xeon Cascade Lake processors:

- TruDDR4 2666, single-rank or dual-rank, 16 GB/32 GB RDIMMs

- DDR4 2933, single-rank or dual-rank, 8 GB/16 GB/32 GB/64 GB RDIMMs (available by June 2019)

- 128 GB, 256 GB, or 512 GB DCPMMs

For a list of supported memory options, see: http://www.lenovo.com/us/en/serverproven/

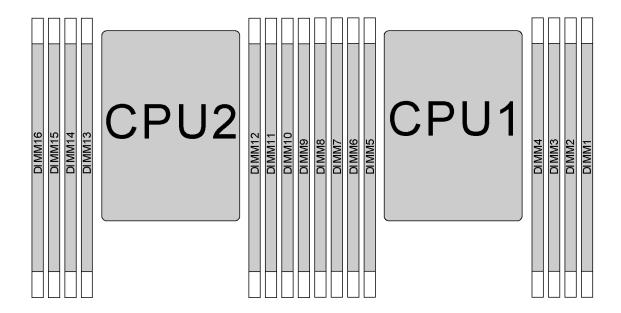

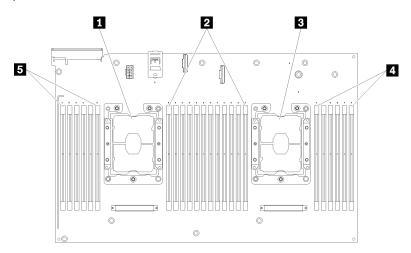

The following illustration helps you to locate the memory slots on the system board.

Figure 6. DIMM locations

The following table shows the relationship between the processors, memory controllers, memory channels, slots, and DIMM numbers. For each memory controller, channel 0 has two DIMM slots (slot 0, furthest from the processor, and slot 1, closest to the processor), and channel 1 and channel 2 have only one DIMM slot (slot 0).

| Processor                                   | CP   | U2   | CPU1 |      |  |  |  |

|---------------------------------------------|------|------|------|------|--|--|--|

| Integrated<br>Memory<br>Controller<br>(iMC) | iMC1 | iMC0 | iMC1 | iMC0 |  |  |  |

© Copyright Lenovo 2019

| Channel<br>(CH) | C-<br>H2 | C-<br>H1 | Cl | <del>1</del> 0 | CI | H0 | C-<br>H1 | C-<br>H2 | C-<br>H2 | C-<br>H1 | Cŀ | 10 | Cł | <del>1</del> 0 | C-<br>H1 | C-<br>H2 |

|-----------------|----------|----------|----|----------------|----|----|----------|----------|----------|----------|----|----|----|----------------|----------|----------|

| Slot            | 0        | 0        | 0  | 1              | 1  | 0  | 0        | 0        | 0        | 0        | 0  | 1  | 1  | 0              | 0        | 0        |

| DIMM<br>number  | 16       | 15       | 14 | 13             | 12 | 11 | 10       | 9        | 8        | 7        | 6  | 5  | 4  | 3              | 2        | 1        |

#### Notes:

- To verify if the presently installed processors support DCPMMs, examine the four digits in the processor description. Only processors with description meeting both of the following requirements support DCPMMs.

- The first digit is 5 or a larger number.

**Note:** The only exception to this rule is *Intel Xeon Silver 4215*, which also supports DCPMM.

- The second digit is 2.

Example: Intel Xeon 5215L and Intel Xeon Platinum 8280M

If the presently installed processors do not support DCPMMs, replace them with the processors that support DCPMMs.

- Supported memory capacity range varies with the following types of processors:

- Large memory tier (L): The processors with L after the four digits (for example: Intel Xeon 5215L)

- Medium memory tier (M): The processors with M after the four digits (for example: Intel Xeon Platinum 8280**M**)

- Other: Other processors that support DCPMMs (for example: Intel Xeon Gold 5222)

In addition, you can take advantage of a memory configurator, which is available at the following site:

http://1config.lenovo.com/#/memory\_configuration

## SR570 Memory Mode

In this mode, DCPMMs act as volatile system memory, while DRAM DIMMs act as cache. Only DCPMM capacity is displayed as system memory in this mode.

## Memory Mode with one processor

Table 34. Memory population order in Memory Mode with one processor

D: DRAM DIMM; 16 GB or 32 GB RDIMM supported P: DC Persistent Memory Module (DCPMM) **Processor 1** Configuration 8 7 5 4 3 2 6 1 Р Р 2 DCPMMs and 6 RDIMMs D D D D D D

Table 35. Supported DCPMM capacity in Memory Mode with one processor

| Total<br>DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM <sup>1</sup> | 512 GB DCPMM <sup>2</sup> |

|-----------------|----------------|------------------|--------------|---------------------------|---------------------------|

| 0               | 6              | L                |              | √                         | √                         |

| 2               | 0              | М                |              | √                         | √                         |

Table 35. Supported DCPMM capacity in Memory Mode with one processor (continued)

| Other |  | $\checkmark$ |  |

|-------|--|--------------|--|

|-------|--|--------------|--|

#### Notes:

- 1. For 256 GB DCPMM, use 16 GB RDIMM.

- 2. For 512 GB DCPMM, use 16 GB or 32 GB RDIMM.

## **Memory Mode with two processors**

Table 36. Memory population order in Memory Mode with two processors

| D: DRAM DIMM; 16 GB or 32 GB I                               | D: DRAM DIMM; 16 GB or 32 GB RDIMM supported |    |    |       |      |    |    |   |   |   |   |       |      |   |   |   |

|--------------------------------------------------------------|----------------------------------------------|----|----|-------|------|----|----|---|---|---|---|-------|------|---|---|---|

| P: DC Persistent Memory Module (DCPMM)                       |                                              |    |    |       |      |    |    |   |   |   |   |       |      |   |   |   |

| Configuration                                                |                                              |    | F  | Proce | ssor | 2  |    |   |   |   | F | Proce | ssor | 1 |   |   |

| Comiguration                                                 | 16                                           | 15 | 14 | 13    | 12   | 11 | 10 | 9 | 8 | 7 | 6 | 5     | 4    | 3 | 2 | 1 |

| 4 DCPMMs and 12 RDIMMs D D D P P D D D D D D P P D D D D D D |                                              |    |    |       |      |    |    |   |   |   |   |       |      |   |   |   |

Table 37. Supported DCPMM capacity in Memory Mode with two processors

| Total<br>DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM <sup>1</sup> | 512 GB DCPMM <sup>2</sup> |

|-----------------|----------------|------------------|--------------|---------------------------|---------------------------|

|                 |                | L                |              | √                         | √                         |

| 4               | 12             | М                |              | √                         | √                         |

|                 |                | Other            |              | √                         |                           |

## Notes:

- 1. For 256 GB DCPMM, use 16 GB RDIMM.

- 2. For 512 GB DCPMM, use 16 GB or 32 GB RDIMM. To install four 512 GB DCPMMs, ensure that the processor TDP is lower than or equal to 125 watts.

# **SR570 App Direct Mode**

In this mode, DCPMMs act as independent and persistent memory resources directly accessible by specific applications, and DRAM DIMMs act as system memory. The total displayed system memory in this mode is the total capacity of DRAM DIMMs.

## App Direct mode with one processor

Table 38. Memory population order in App Direct mode with one processor

D: DRAM DIMM; 16 GB, 32 GB, or 64 GB RDIMM supported

P: DC Persistent Memory Module (DCPMM)

| Configuration         |   | Processor 1 |   |   |   |   |   |   |  |  |  |  |  |  |

|-----------------------|---|-------------|---|---|---|---|---|---|--|--|--|--|--|--|

| Configuration         | 8 | 7           | 6 | 5 | 4 | 3 | 2 | 1 |  |  |  |  |  |  |

| 1 DCPMM and 6 RDIMMs  | D | D           | D |   | Р | D | D | D |  |  |  |  |  |  |

| 2 DCPMMs and 6 RDIMMs | D | D           | D | Р | Р | D | D | D |  |  |  |  |  |  |

Table 39. Supported DCPMM capacity in App Direct mode with one processor

| Total<br>DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |

|-----------------|----------------|------------------|--------------|--------------|--------------|

|                 |                | L                | √            | √            | √            |

| 1               | 6              | M                | √            | √            | √            |

|                 |                | Other            | <b>√</b>     | √            | √            |

|                 |                | L                | √            | √            | √            |

| 2               | 6              | M                | <b>√</b>     | √            | <b>√</b>     |

|                 |                | Other            | √            | √            |              |

#### **App Direct mode with two processors**

Table 40. Memory population order in App Direct mode with two processors

D: DRAM DIMM; 16 GB, 32 GB, or 64 GB RDIMM supported

P: DC Persistent Memory Module (DCPMM)

|                        |                          |   | ı | Proce | ssor 2 | 2 |   |   | Processor 1 |   |   |   |   |   |   |   |

|------------------------|--------------------------|---|---|-------|--------|---|---|---|-------------|---|---|---|---|---|---|---|

| Configuration          | 16 15 14 13 12 11 10 9 8 |   |   |       |        |   | 8 | 7 | 6           | 5 | 4 | 3 | 2 | 1 |   |   |

| 1 DCPMM and 12 RDIMMs  | D                        | D | D |       |        | D | D | D | D           | D | D |   | Р | D | D | D |

| 2 DCPMMs and 12 RDIMMs | D                        | D | D |       | Р      | D | D | D | D           | D | D |   | Р | D | D | D |

| 4 DCPMMs and 12 RDIMMs | D                        | D | D | Р     | Р      | D | D | D | D           | D | D | Р | Р | D | D | D |

Table 41. Supported DCPMM capacity in App Direct mode with two processors

| Total<br>DCPMMs | Total<br>DIMMs | Processor Family | 128 GB DCPMM | 256 GB DCPMM | 512 GB DCPMM |

|-----------------|----------------|------------------|--------------|--------------|--------------|

|                 |                | L                | √            | √            | √            |

| 1               | 12             | М                | √            | √            | √            |

|                 |                | Other            | √            | √            | √            |