## int<sub>el</sub>.

## Intel<sup>®</sup> Pentium<sup>®</sup> 4 Processor in 478-Pin Package and Intel<sup>®</sup> 845 Chipset Platform for DDR

**Design Guide**

February 2002

Document Number: 298605-002

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> Pentium 4 processor and the Intel<sup>®</sup> 845 chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Alert on LAN is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

www.intel.com

or call 1-800-548-4725

Intel, Pentium, Intel Netburst and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2002, Intel Corporation

# int<sub>e</sub>l.

## **Contents**

| Introdu | iction                |                         |                                                | 15     |

|---------|-----------------------|-------------------------|------------------------------------------------|--------|

| 1.1     | Related               | Documenta               | tion                                           | 16     |

| 1.2     | Convent               | ions and Te             | rminology                                      | 18     |

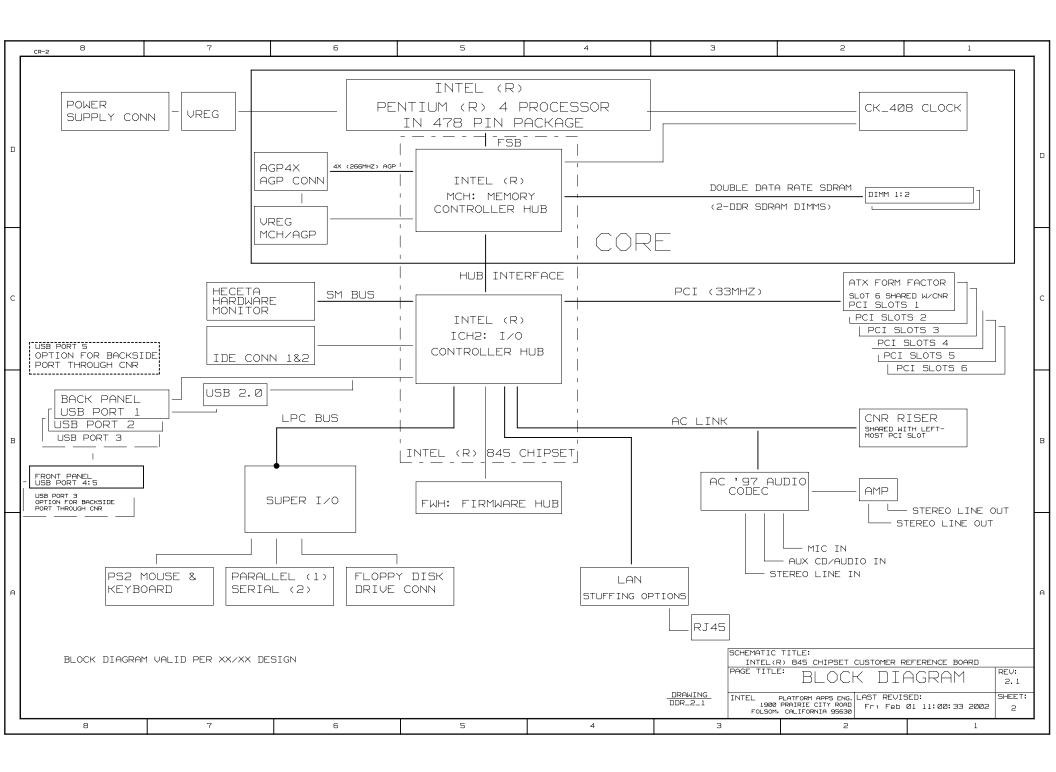

| 1.3     | System                | Overview                |                                                | 21     |

|         | 1.3.1                 | Intel <sup>®</sup> Pent | ium <sup>®</sup> 4 Processor                   | 21     |

|         | 1.3.2                 |                         | Chipset                                        | 21     |

|         |                       | 1.3.2.1                 | Intel <sup>®</sup> Memory Controller Hub (MCH) |        |

|         |                       | 1.3.2.2                 | Accelerated Graphics Port (AGP) Interface      |        |

|         |                       | 1.3.2.3                 |                                                | 22     |

|         | 1.3.3                 | 1.3.2.4                 | Intel <sup>®</sup> I/O Controller Hub 2 (ICH2) |        |

|         | 1.3.3                 |                         | Summary<br>onfigurations                       |        |

| 1.4     |                       | •                       |                                                |        |

| 1.4     | 1.4.1                 |                         | Chipset                                        |        |

|         | 1.4.1                 | 1.4.1.1                 | Processor/Host Interface (System Bus)          |        |

|         |                       | 1.4.1.2                 | System Memory Interface                        |        |

|         |                       |                         | Accelerated Graphics Port (AGP)                | 25     |

|         | 1.4.2                 | Intel <sup>®</sup> ICH2 | 2                                              | 25     |

|         |                       | 1.4.2.1                 | Integrated LAN Controller                      | 25     |

|         |                       | 1.4.2.2                 | Ultra ATA/100 Support                          |        |

|         |                       | 1.4.2.3                 | Expanded USB 1.1 Support                       |        |

|         |                       | 1.4.2.4                 | AC '97 6-Channel Support                       |        |

|         | 1.4.3                 | -                       | ility and Other Enhancements                   |        |

|         |                       | 1.4.3.1<br>1.4.3.2      | SMBus                                          |        |

|         | 1.4.4                 | -                       | Interrupt Controller<br>Platform Compliance    |        |

|         |                       |                         | •                                              |        |

| Compo   |                       | •                       | t                                              |        |

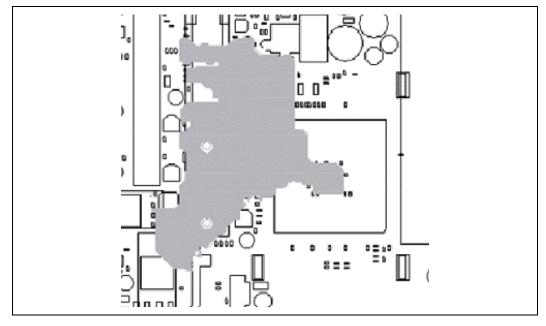

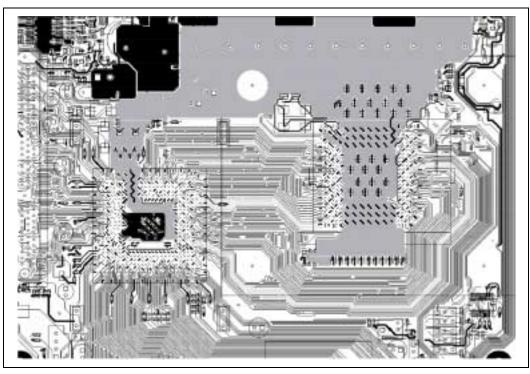

| 2.1     | Intel <sup>®</sup> Pe | ntium <sup>®</sup> 4 Pr | ocessor Component Quadrant Layout              | 29     |

| 2.2     | Intel <sup>®</sup> 84 | 5 Chipset C             | omponent Quadrant Layout                       | 30     |

| 2.3     |                       |                         | ent Quadrant Layout                            |        |

|         |                       | -                       | -                                              |        |

|         |                       |                         | ck-Up Overview                                 |        |

| 3.1     |                       |                         | t Placement (DDR-SDRAM)                        |        |

| 3.2     | Nominal               | 4-Layer Boa             | ard Stack-Up                                   | 32     |

| 3.3     | PCB Tec               | chnologies              |                                                | 34     |

|         | 3.3.1                 | Design Co               | nsiderations                                   | 34     |

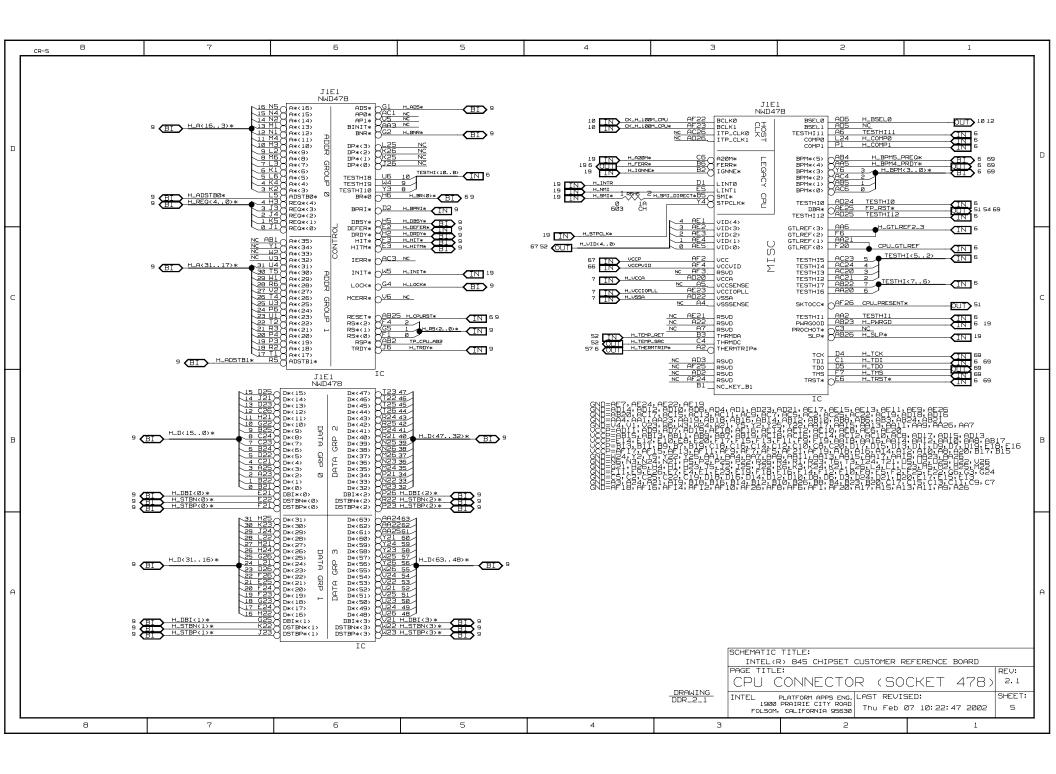

| Proces  | sor Syste             | m Bus Guid              | elines                                         | 35     |

| 4.1     | Process               | or System B             | us Design Guidelines                           | 35     |

|         | 4.1.1                 |                         | ayout and Routing Recommendations              |        |

|         | 4.1.2                 | HVREF, H                | SWNG, HRCOMP Layout and Routing Recommendatio  | ons at |

|         |                       | the Intel®              | ИСН                                            | 38     |

| 4.2     | Process               | or Configura            | ition                                          | 39     |

|         |                       |                         |                                                |        |

|     | 4.2.1                | Intel <sup>®</sup> Per  | ntium <sup>®</sup> 4 Processor Configuration                                                                                 | 39         |

|-----|----------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------|------------|

|     | 4.2.2                |                         | and Routing                                                                                                                  |            |

|     |                      | 4.2.2.1                 | Design Recommendations                                                                                                       |            |

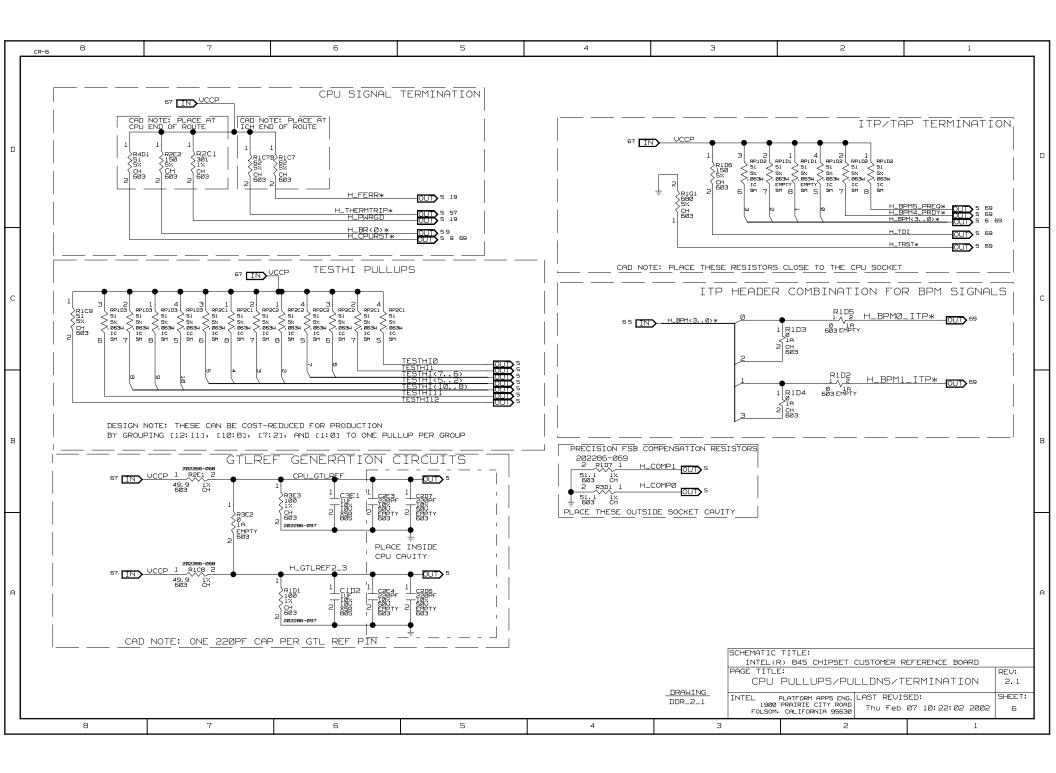

| 4.3 |                      |                         | for Asynchronous GTL+ and Other Signals                                                                                      |            |

|     | 4.3.1                |                         | es                                                                                                                           |            |

|     |                      | 4.3.1.1                 | Topology 1A: Asynchronous GTL+ Signal Driven by the<br>Processor—FERR#                                                       |            |

|     |                      | 4.3.1.2                 | Topology 1B: Asynchronous GTL+ Signal Driven by the<br>Processor—PROCHOT#                                                    | 44         |

|     |                      | 4.3.1.3                 | Topology 1C: Asynchronous GTL+ Signal Driven by the<br>Processor—THERMTRIP#                                                  | 45         |

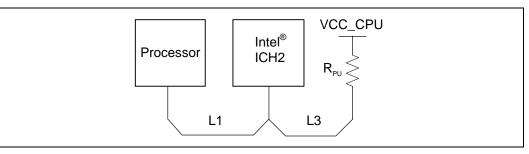

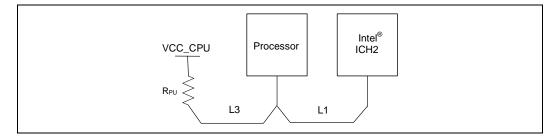

|     |                      | 4.3.1.4                 | Topology 2A: Asynchronous GTL+ Signals Driven by the Intel <sup>®</sup> ICH2—A20M#, IGNNE#, LINT[1:0], SLP#, SMI#, a STPCLK# | and        |

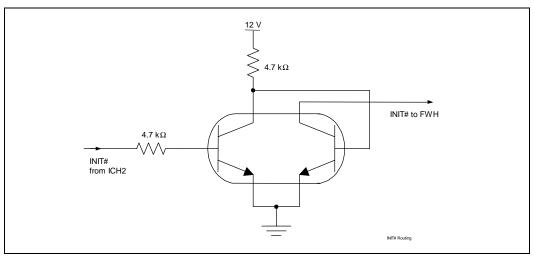

|     |                      | 4.3.1.5                 | Topology 2B: Asynchronous GTL+ Signal Driven by the Intel <sup>®</sup> ICH2—INIT#                                            | 47         |

|     |                      | 4.3.1.6                 | Topology 2C: Asynchronous GTL+ Signal Driven by the Intel <sup>®</sup> ICH2 Open Drain—PWRGOOD                               |            |

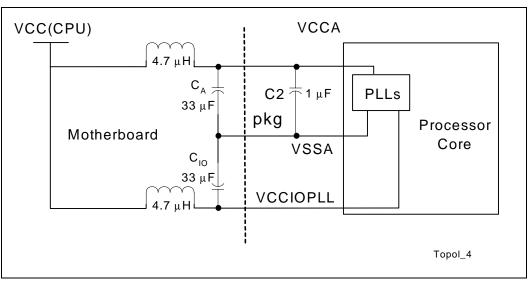

|     |                      | 4.3.1.7                 | Topology 3—V <sub>CCIOPLL</sub> , V <sub>CCA</sub> and V <sub>SSA</sub>                                                      | 48         |

|     |                      | 4.3.1.8                 | Topology 4—BR0# and RESET#                                                                                                   |            |

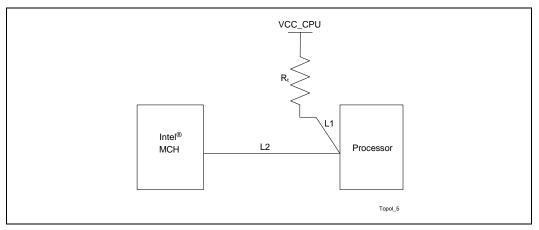

|     |                      | 4.3.1.9                 | Topology 5: COMP[1:0] Signals                                                                                                |            |

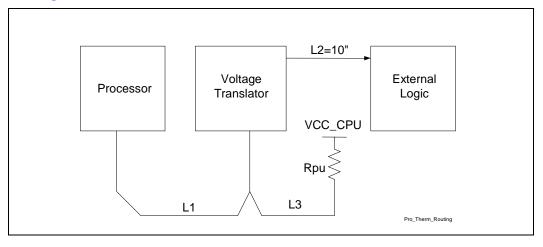

|     |                      | 4.3.1.10                | Topology 6: THERMDA/THERMDC Routing Guidelines                                                                               |            |

|     |                      | 4.3.1.11                | Topology 7: TESTHI and RESERVED Pins                                                                                         | 50         |

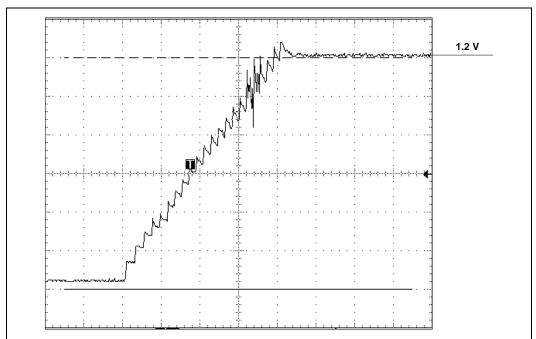

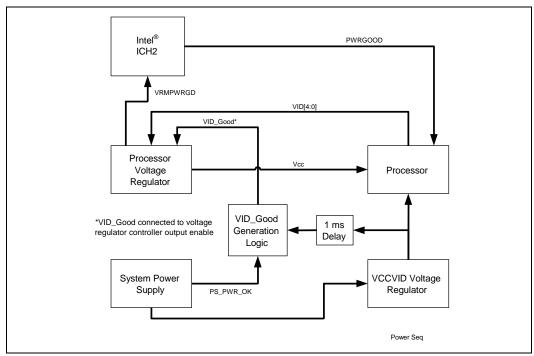

|     |                      | 4.3.1.12                | Topology 8: Processor Voltage Regulator Sequencing                                                                           | <b>F</b> 4 |

| 4 4 | A ddition            |                         | Requirements                                                                                                                 |            |

| 4.4 |                      |                         | or Design Considerations                                                                                                     |            |

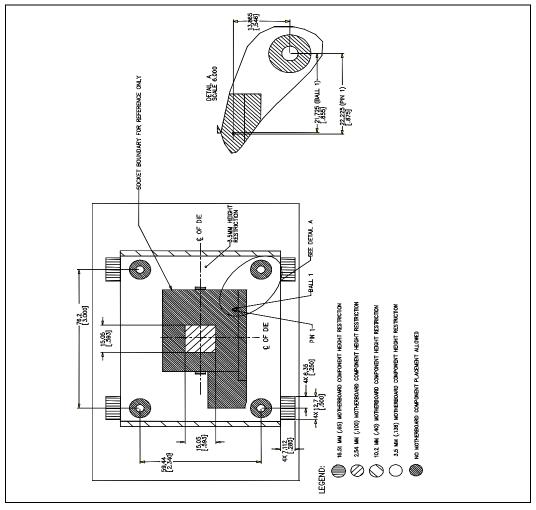

|     | 4.4.1<br>4.4.2       |                         | Mechanism Placement and Keep-Outs                                                                                            |            |

| 4.5 |                      |                         | g Guidelines                                                                                                                 |            |

| 4.5 | 4.5.1                |                         | pols Specifications                                                                                                          |            |

|     | 4.5.1                | 4.5.1.1                 | Logic Analyzer Interface (LAI)                                                                                               |            |

|     |                      | 4.5.1.1                 | Mechanical Considerations                                                                                                    |            |

|     |                      | 4.5.1.3                 | Electrical Considerations                                                                                                    |            |

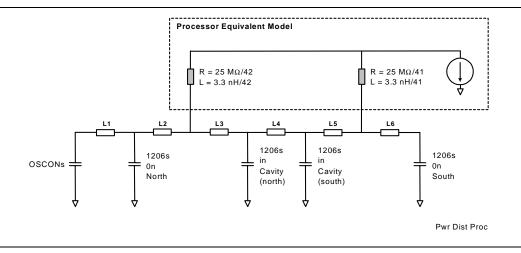

| 4.6 | Intel <sup>®</sup> P |                         | Processor Power Distribution Guidelines                                                                                      |            |

| 4.0 | 4.6.1                |                         | equirements                                                                                                                  |            |

|     | 4.6.2                |                         | Processor Thermal Design Power (TDP) Limit                                                                                   |            |

|     | 4.6.3                |                         | ng Requirements                                                                                                              |            |

|     | 4.6.4                |                         |                                                                                                                              |            |

|     | 4.6.5                |                         | Considerations                                                                                                               |            |

|     | 4.6.6                | Simulatio               |                                                                                                                              | -          |

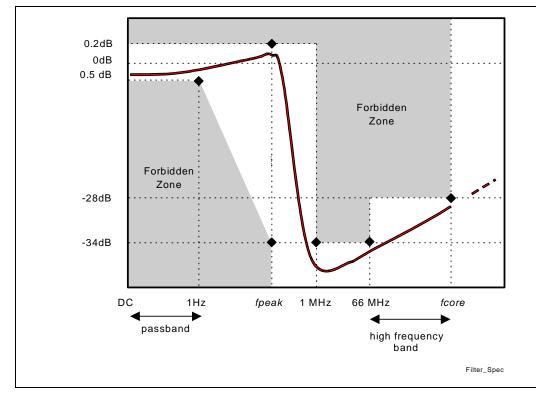

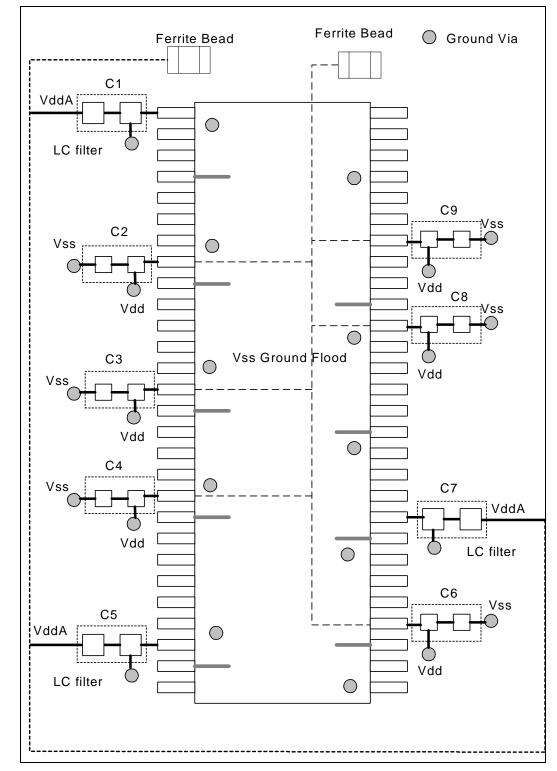

|     |                      | 4.6.6.1                 | Filter Specifications for V <sub>CCA</sub> , V <sub>CCIOPLL</sub> , and V <sub>SSA</sub>                                     | 68         |

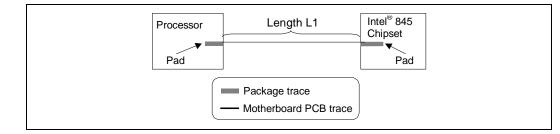

| 4.7 | Intel <sup>®</sup> P | entium <sup>®</sup> 4 F | Processor and Intel <sup>®</sup> 845 Chipset Package Lengths                                                                 | 71         |

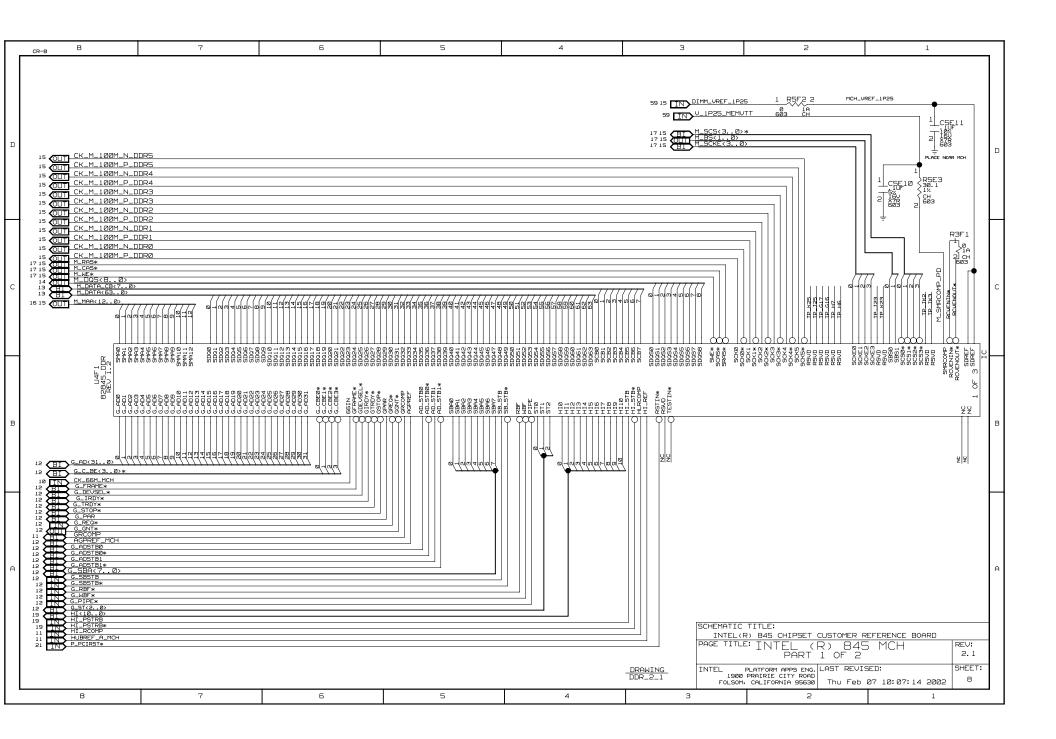

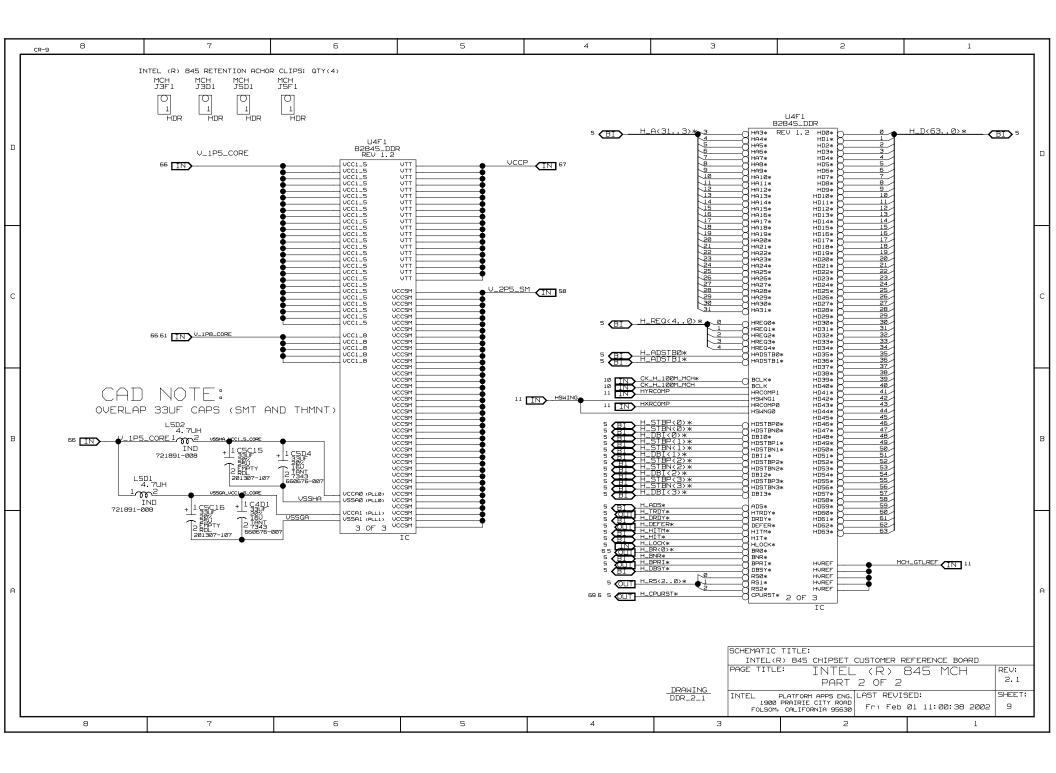

|     |                      |                         | nous DRAM (DDR-SDRAM) System Memory Design                                                                                   | 75         |

| 5.1 |                      |                         | Signals                                                                                                                      |            |

| 5.2 |                      | · ,                     | k-Up and Referencing Guidelines                                                                                              |            |

|     |                      |                         |                                                                                                                              |            |

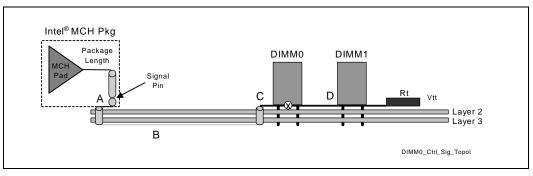

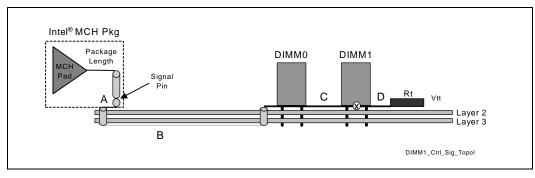

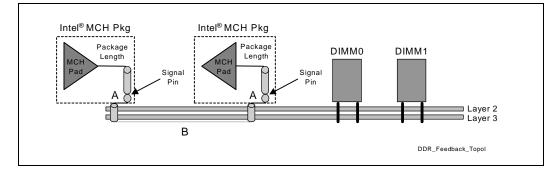

| 5.3 |                      |                         | ory Topology and Layout Design Guidelines                                                                                    |            |

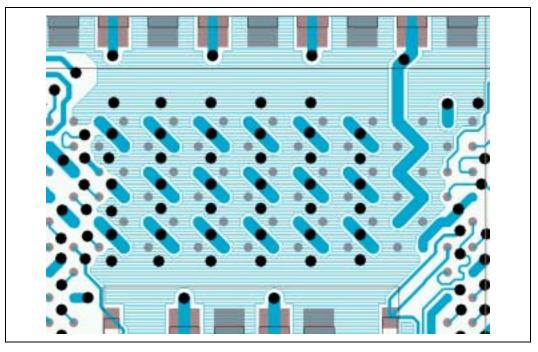

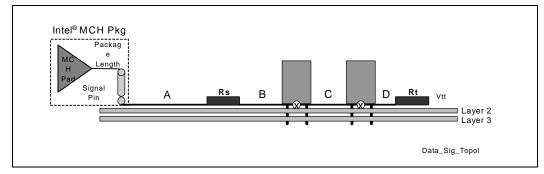

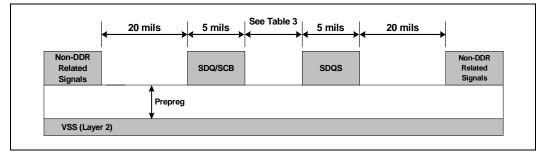

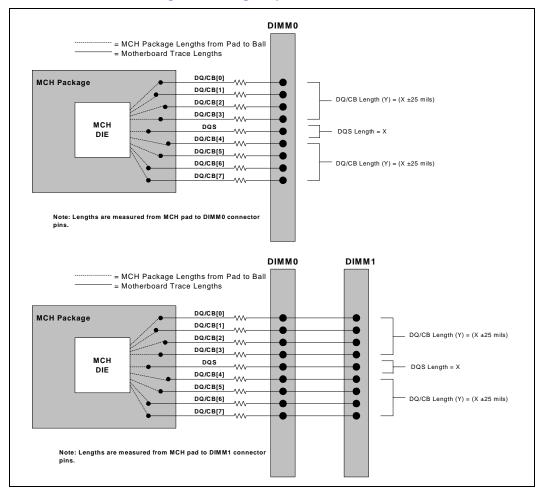

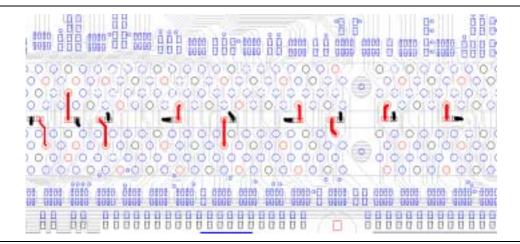

|     | 5.3.1                |                         | nals—SDQ[63:0], SDQS[8:0], SCB[7:0]                                                                                          | 81         |

|     |                      | 5.3.1.1<br>5.3.1.2      | Routing Example—SDQ[63:0], SCB[7:0], SDQS[8:0]<br>Data Group Signal Length Matching Requirements                             |            |

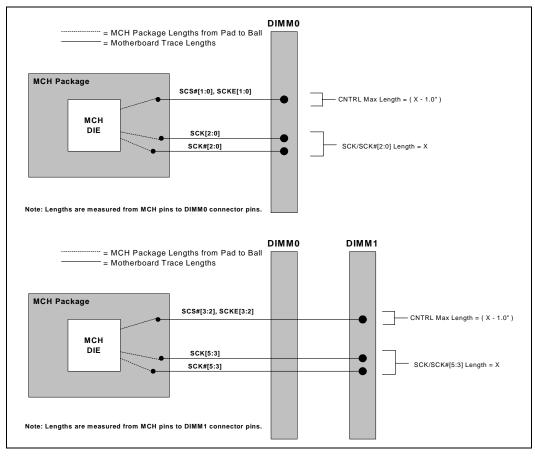

|     | 5.3.2                |                         | ignals—SCKE[3:0], SCS#[3:0]                                                                                                  |            |

|     |                      |                         | C L 1/ L - 1                                                                                                                 |            |

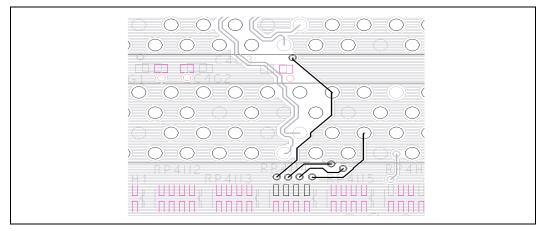

|        |                | 5.3.2.1<br>5.3.2.2     | Routing Examples—SCS#[3:0], SCKE[3:0]<br>Control Signal to System Memory Clock Routing<br>Requirements                          |                |

|--------|----------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------|

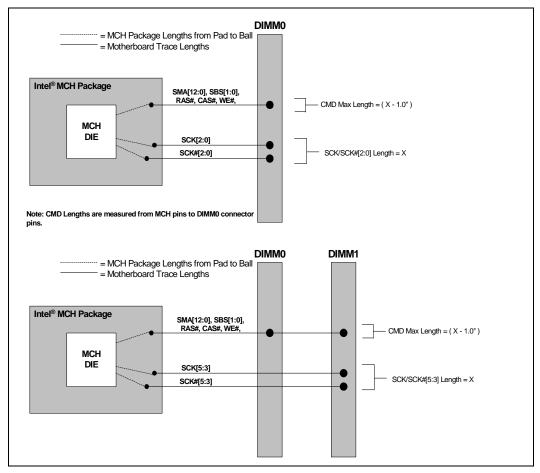

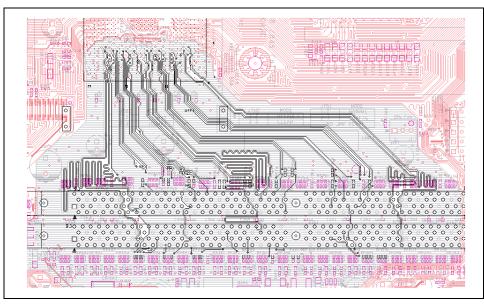

|        | 5.3.3          | Command 5.3.3.1        | Signals—SMA[12:0], SBS[1:0], SRAS#, SCAS#, SWE#<br>Routing Examples—SMA[12:0], SBS[1:0], SCAS#, SRAS#<br>SWE#                   | 88<br>#,<br>90 |

|        |                | 5.3.3.2                | Command Group Signal to System Memory Clock Routing<br>Requirements                                                             |                |

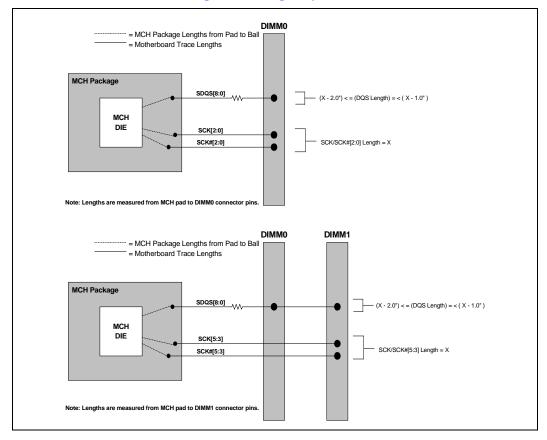

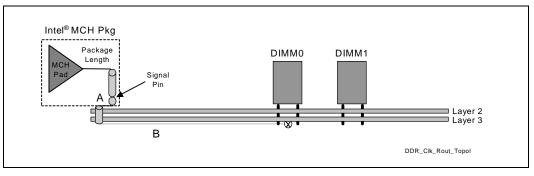

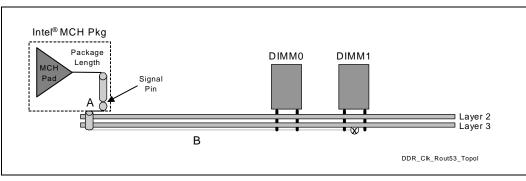

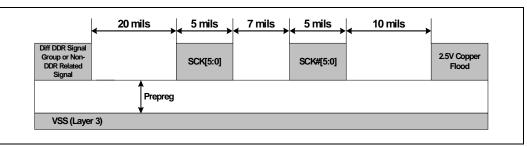

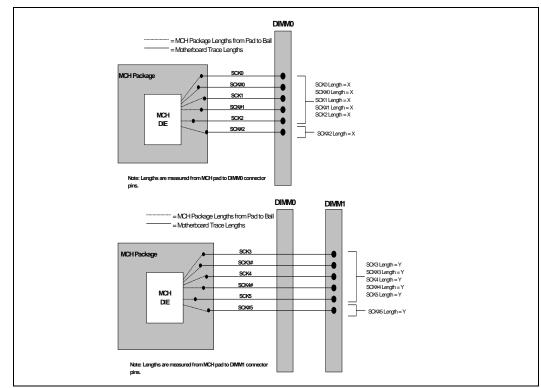

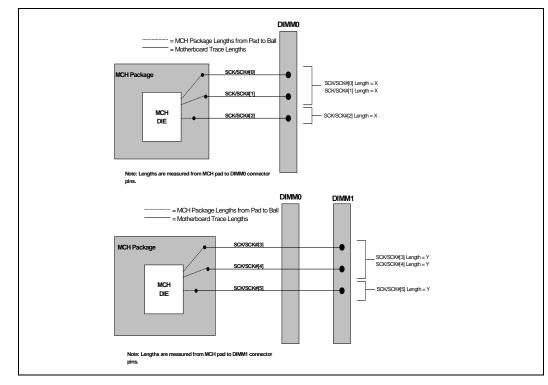

|        | 5.3.4          | Clock Sign             | als—SCK[5:0], SCK#[5:0]                                                                                                         | 93             |

|        |                | 5.3.4.1                | Routing Examples—SCK[5:0], SCK#[5:0]                                                                                            |                |

|        |                | 5.3.4.2                | Clock Group Signal Length Matching Requirements                                                                                 |                |

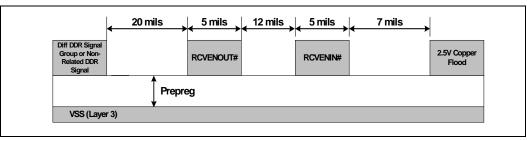

|        | 5.3.5          |                        | -RCVENOUT#, RCVENIN#                                                                                                            |                |

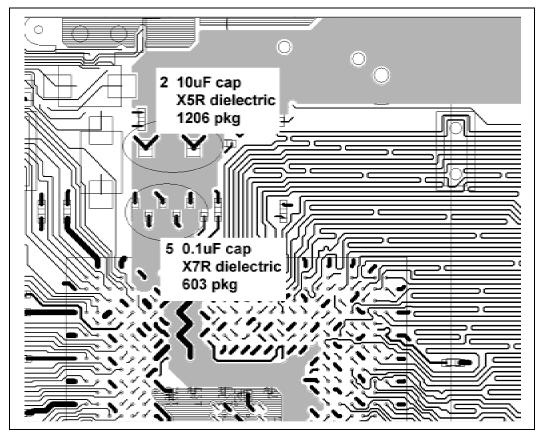

| 5.4    | •              |                        | bass Capacitor Guidelines                                                                                                       |                |

| 5.5    |                |                        | ······                                                                                                                          |                |

|        | 5.5.1          |                        | er Delivery Guidelines                                                                                                          |                |

|        | 5.5.2          |                        | System Memory Interface Decoupling Requirements                                                                                 |                |

|        |                | 5.5.2.1                | Intel <sup>®</sup> MCH System Memory High-Frequency Decoupling.                                                                 | 104            |

|        |                | 5.5.2.2                | Intel <sup>®</sup> MCH System Memory Low-Frequency Bulk                                                                         | 405            |

|        |                |                        | Decoupling                                                                                                                      |                |

|        | 5.5.3          |                        | A Decoupling Requirements                                                                                                       |                |

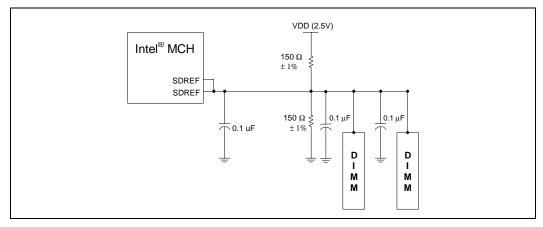

|        | 5.5.4          |                        | rence Voltage                                                                                                                   |                |

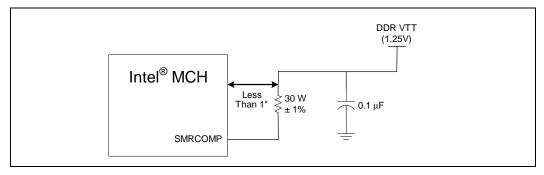

|        | 5.5.5<br>5.5.6 |                        | COMP Resistive Compensation                                                                                                     |                |

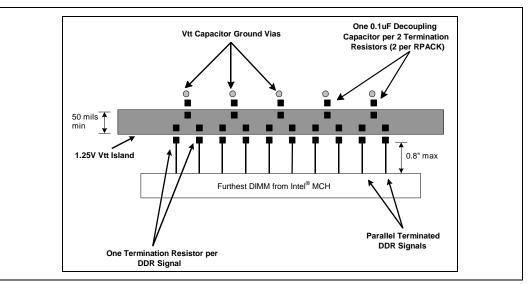

|        | 5.5.6          | 5.5.6.1                | Routing Example—DDR $V_{TT}$ Termination Island                                                                                 |                |

|        |                | 5.5.6.2                | V <sub>TT</sub> Termination Island High-Frequency Decoupling                                                                    |                |

|        |                | 5.5.6.3                | Requirements                                                                                                                    |                |

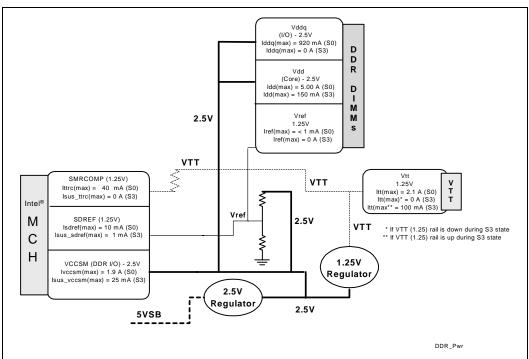

|        | 5.5.7          | DDR Volta              | ge Regulator Guidelines                                                                                                         | 110            |

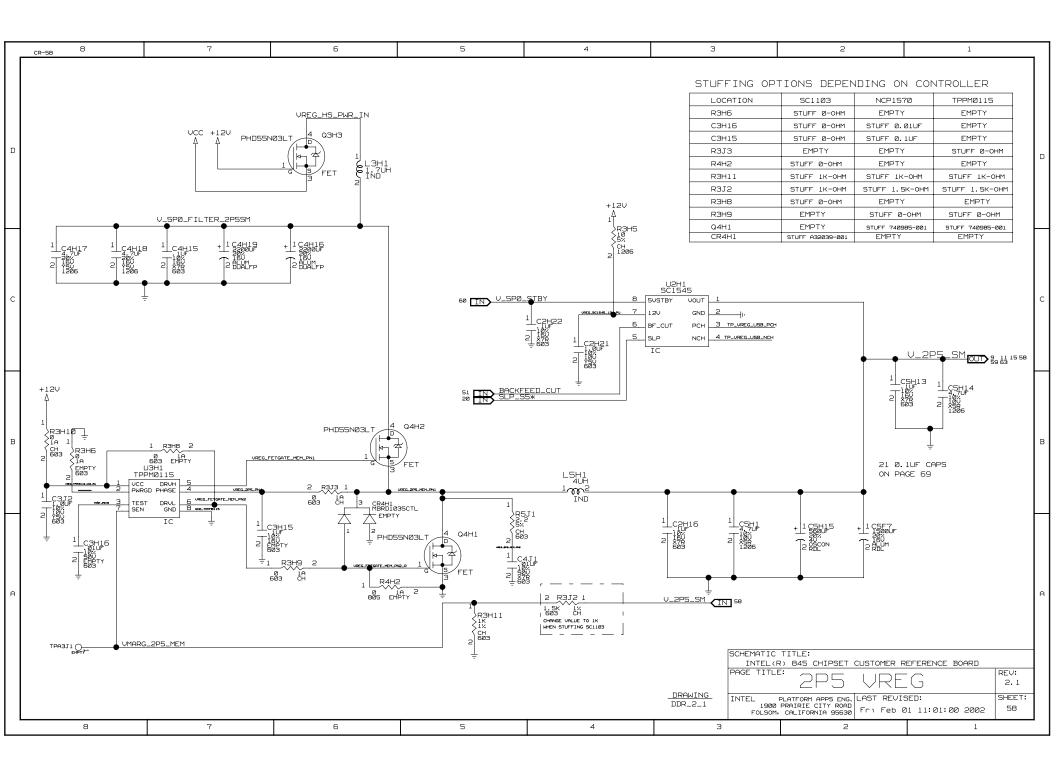

|        |                | 5.5.7.1                | Intel <sup>®</sup> 845 Chipset DDR Reference Board Power Delivery                                                               |                |

|        |                | 5.5.7.2                | DDR 2.5 V Power Plane                                                                                                           |                |

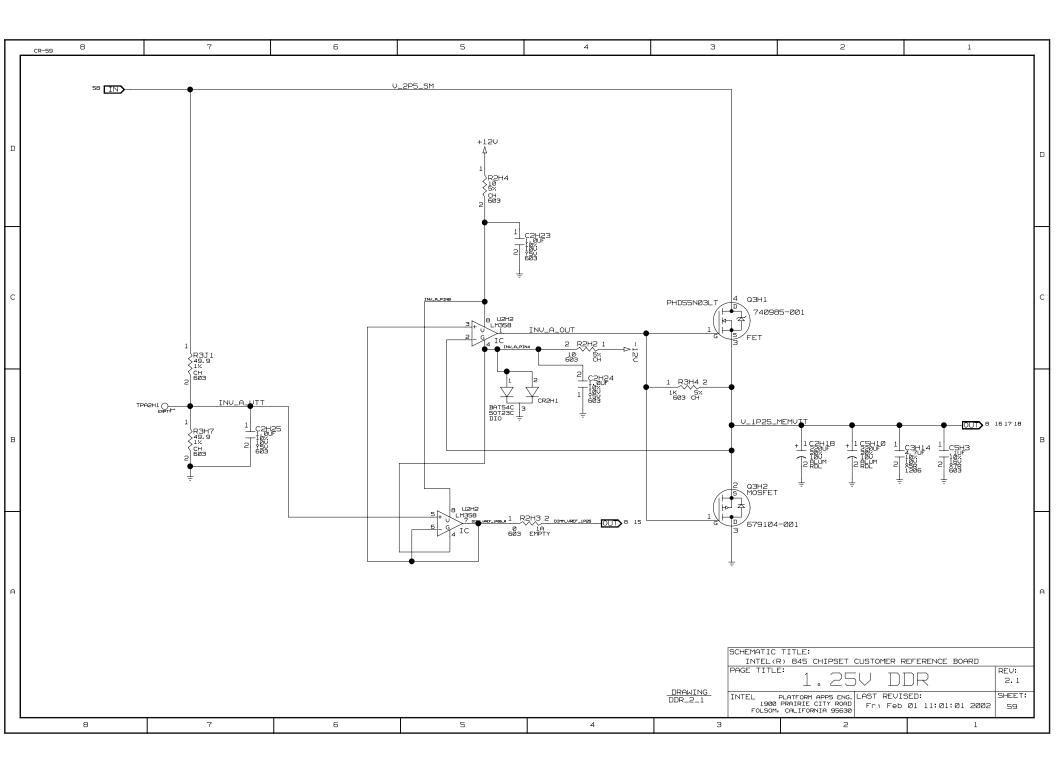

|        |                | 5.5.7.3                | DDR 1.25 V Power Plane                                                                                                          | 111            |

|        |                | 5.5.7.4                | DDR Reference Voltage (V <sub>REF</sub> )                                                                                       | 111            |

|        |                | 5.5.7.5<br>5.5.7.6     | DC and AC Electrical Characteristics (DIMM Supply Rails)<br>DC and AC Electrical Characteristics (Intel <sup>®</sup> MCH Supply | )111           |

|        |                |                        | Rails)                                                                                                                          |                |

|        |                | 5.5.7.7                | DC and AC Electrical Characteristics (V $_{TT}$ Supply Rail)                                                                    |                |

|        |                | 5.5.7.8                | DDR Voltage Regulator Reference Design Example                                                                                  |                |

|        | 5.5.8          |                        | juencing Requirements                                                                                                           | 114            |

|        |                | 5.5.8.1                | Intel® MCH Power Sequencing Requirements                                                                                        |                |

|        |                | 5.5.8.2                | DDR-SDRAM Power Sequencing Requirements                                                                                         |                |

| 5.6    |                |                        | nal Package Lengths                                                                                                             |                |

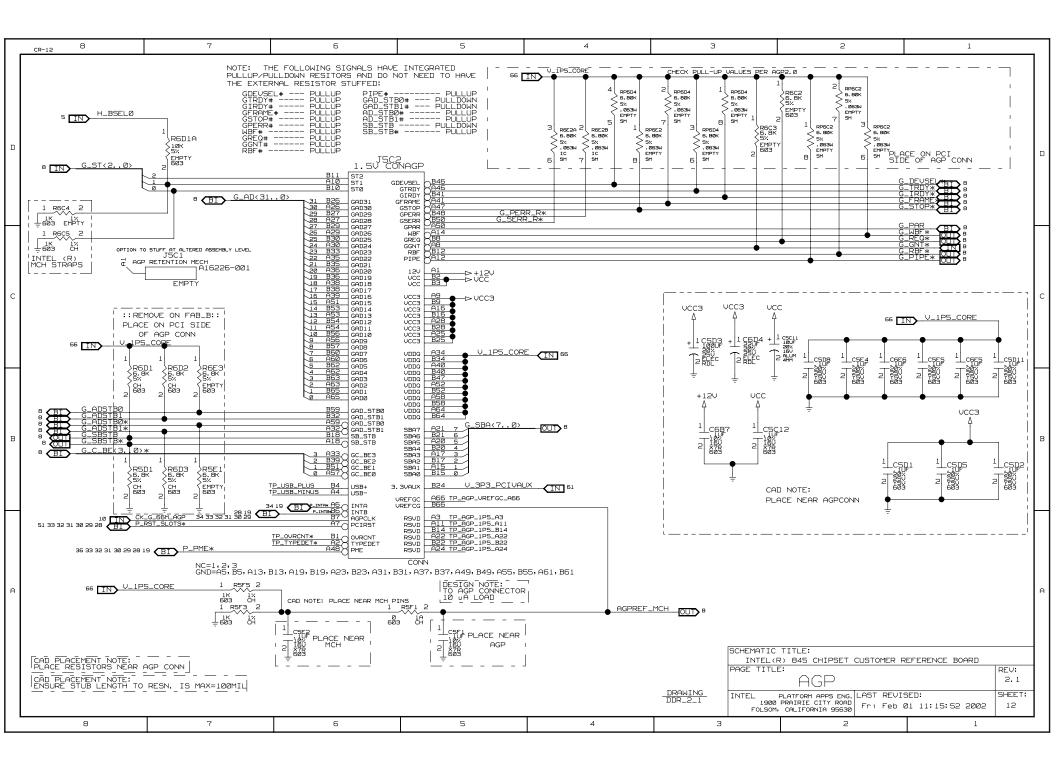

| AGP In | terface De     | esign Guide            | lines                                                                                                                           | 119            |

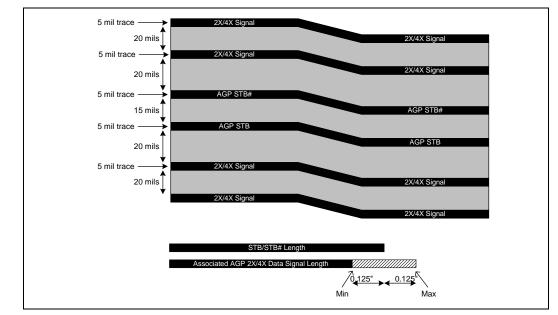

| 6.1    | AGP Rou        | iting Guidel           | ines                                                                                                                            | 120            |

|        | 6.1.1          | 1X Timing              | Domain Signal Routing Guidelines                                                                                                | 120            |

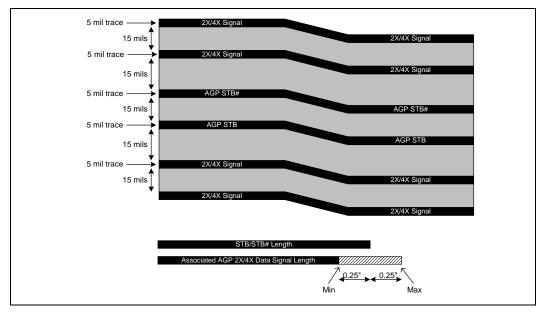

|        | 6.1.2          |                        | ing Domain Signal Routing Guidelines                                                                                            |                |

|        |                | 6.1.2.1                | Trace Lengths Less Than 6 Inches                                                                                                | 121            |

|        |                | 6.1.2.2                | Trace Lengths Greater Than 6 Inches and Less Than 7.25                                                                          |                |

|        |                |                        | Inches                                                                                                                          |                |

|        | 6.1.3          |                        | aces Trace Length Summary                                                                                                       |                |

|        | 6.1.4          |                        | ver/Ground Referencing Recommendations                                                                                          |                |

|        | 6.1.5          | V <sub>DDQ</sub> and T | TYPEDET#                                                                                                                        | 124            |

6

## int<sub>el</sub>.

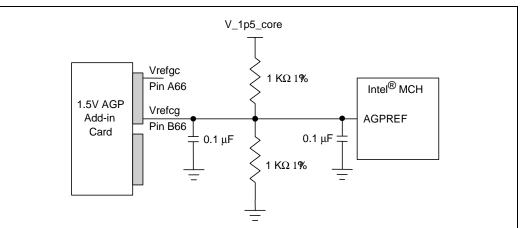

|                      | 6.1.6<br>6.1.7<br>6.1.8<br>6.1.9 | V <sub>REF</sub> Generation<br>Intel <sup>®</sup> MCH AGP Interface Buffer Compensation<br>Intel <sup>®</sup> MCH External AGP Pull-Up/Pull-Down Resistors | 125<br>126 |

|----------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

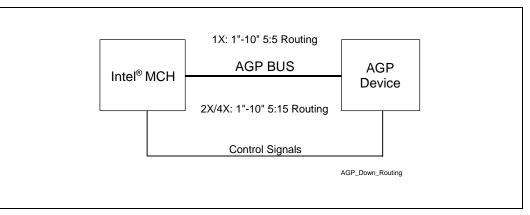

|                      | 0.1.9                            | AGP Device Down Routing Guidelines<br>6.1.9.1 1X Timing Domain Signal Routing Guidelines                                                                   |            |

|                      |                                  | 6.1.9.2 2X/4X Timing Domain Signal Routing Guidelines                                                                                                      |            |

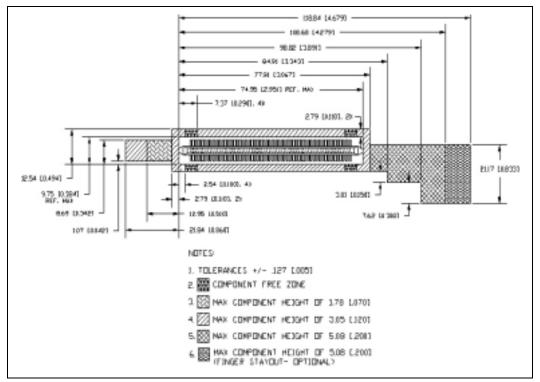

|                      | 6.1.10                           | AGP Connector                                                                                                                                              |            |

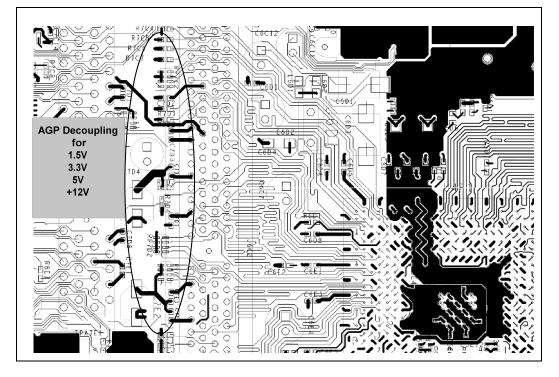

|                      | 6.1.11                           | AGP Connector Decoupling Guidelines                                                                                                                        |            |

|                      | 6.1.12                           | AGP Universal Retention Mechanism (RM)                                                                                                                     |            |

| Hub In               | terface                          | · · · ·                                                                                                                                                    | 133        |

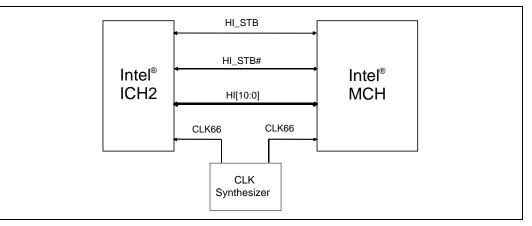

| 7.1                  | 8-Bit Hu                         | b Interface Routing Guidelines                                                                                                                             | 133        |

|                      | 7.1.1                            | 8-Bit Hub Interface Data Signals                                                                                                                           |            |

|                      | 7.1.2                            | 8-Bit Hub Interface Strobe Signals                                                                                                                         |            |

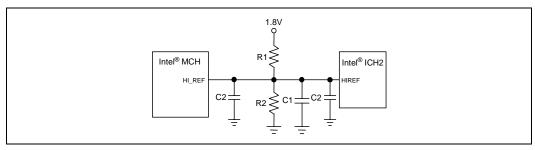

|                      | 7.1.3                            | 8-Bit Hub Interface HI_REF Generation/Distribution                                                                                                         |            |

|                      | 7.1.4                            | 8-Bit Hub Interface Compensation                                                                                                                           |            |

|                      | 7.1.5                            | 8-Bit Hub Interface Decoupling Guidelines                                                                                                                  | 135        |

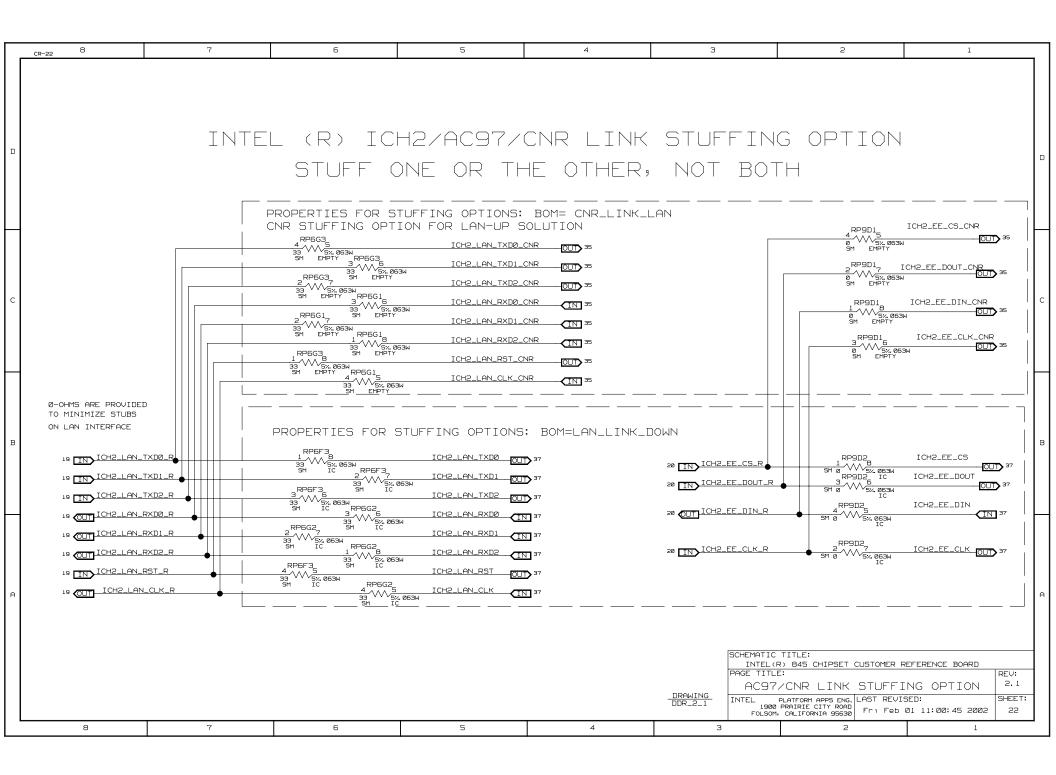

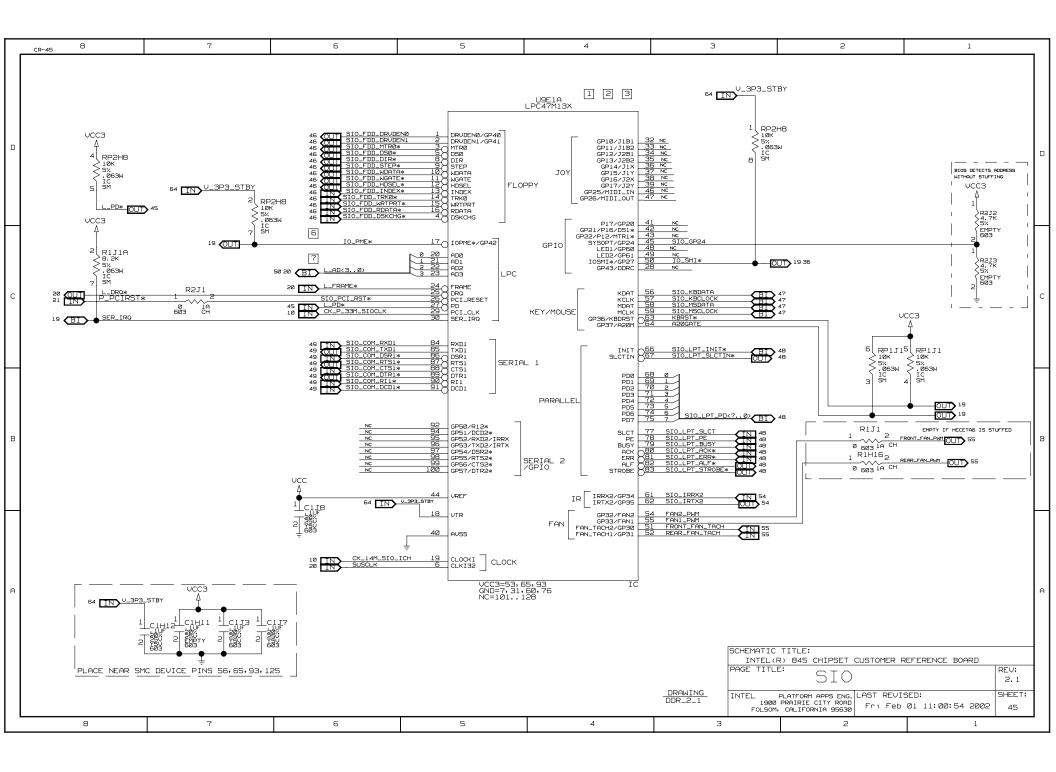

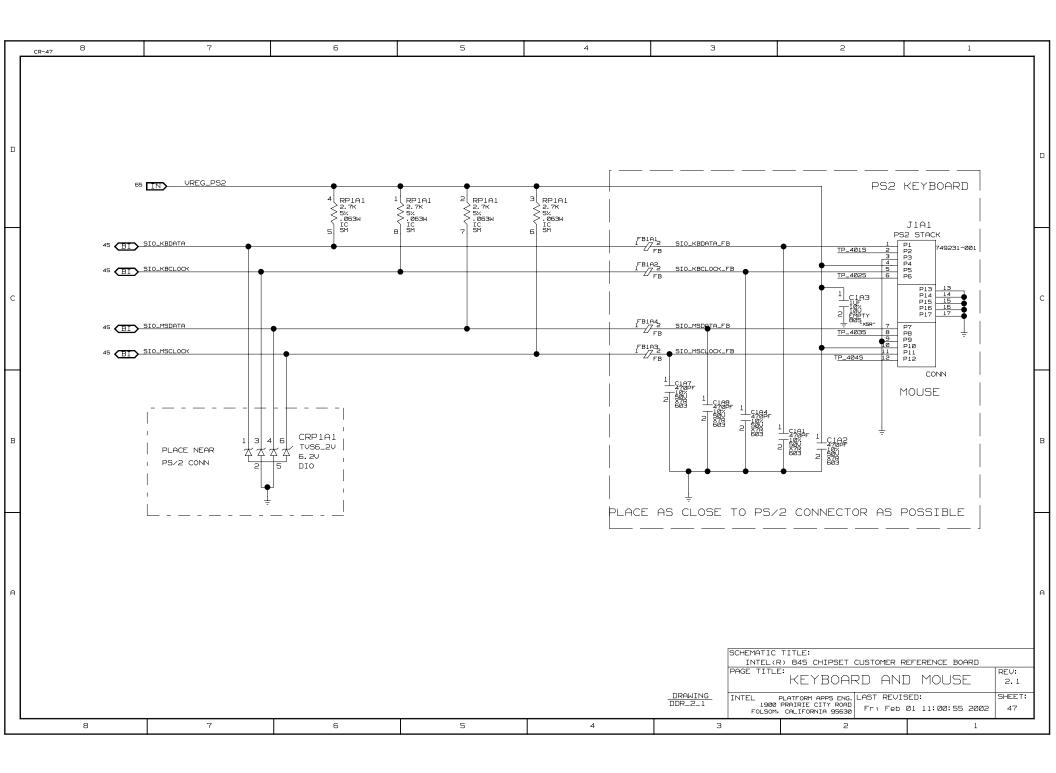

| Intel <sup>®</sup> I | /O Contro                        | ller Hub 2 (ICH 2)                                                                                                                                         | 137        |

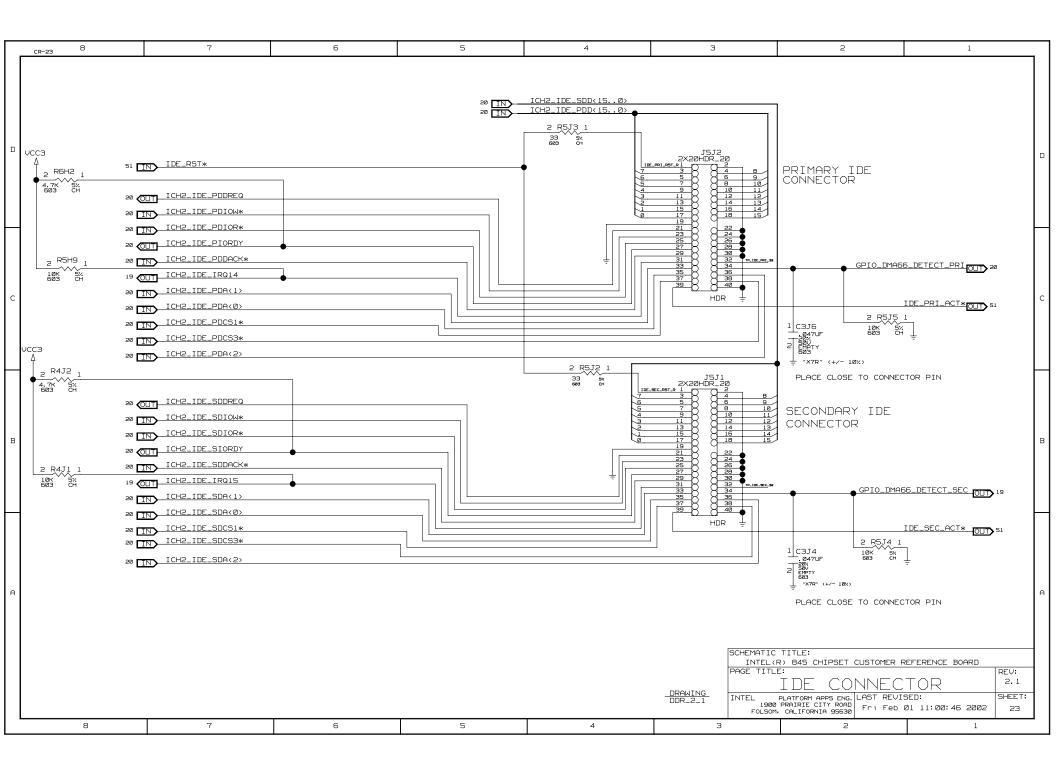

| 8.1                  | IDE Inte                         | rface                                                                                                                                                      | 137        |

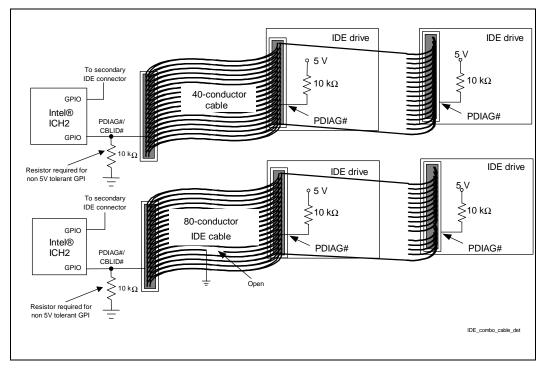

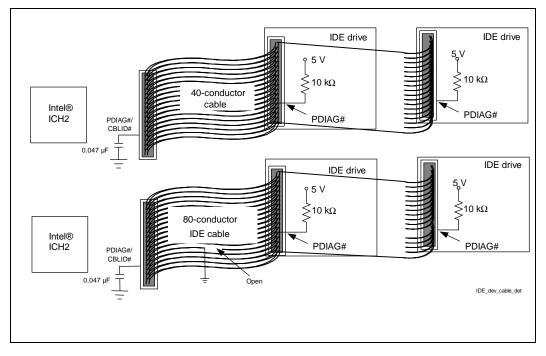

|                      | 8.1.1                            | Cabling                                                                                                                                                    | 137        |

|                      |                                  | 8.1.1.1 Cable Detection for Ultra ATA/66 and Ultra ATA/100                                                                                                 | 137        |

|                      |                                  | 8.1.1.2 Combination Host-Side/Device-Side Cable Detection                                                                                                  | 138        |

|                      |                                  | 8.1.1.3 Device-Side Cable Detection                                                                                                                        |            |

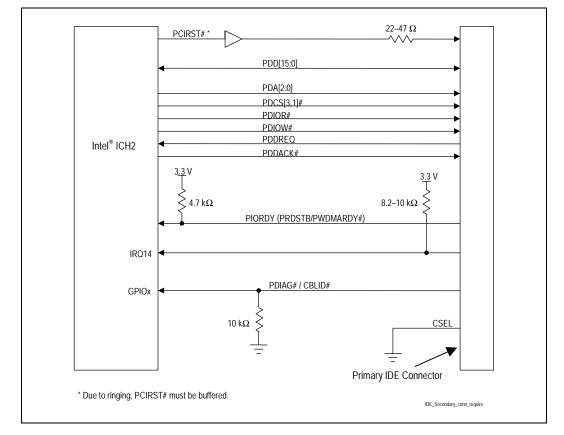

|                      | 8.1.2                            | Primary IDE Connector Requirements                                                                                                                         |            |

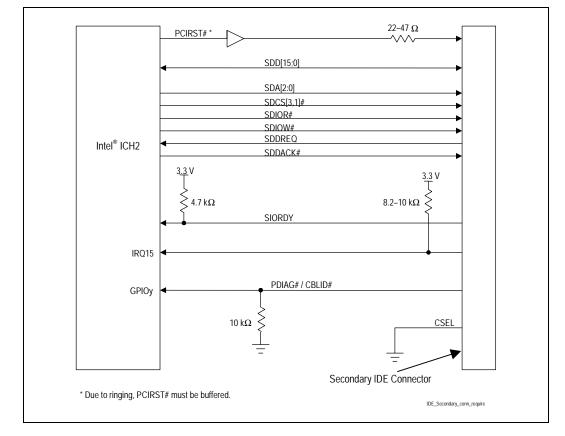

|                      | 8.1.3                            | Secondary IDE Connector Requirements                                                                                                                       |            |

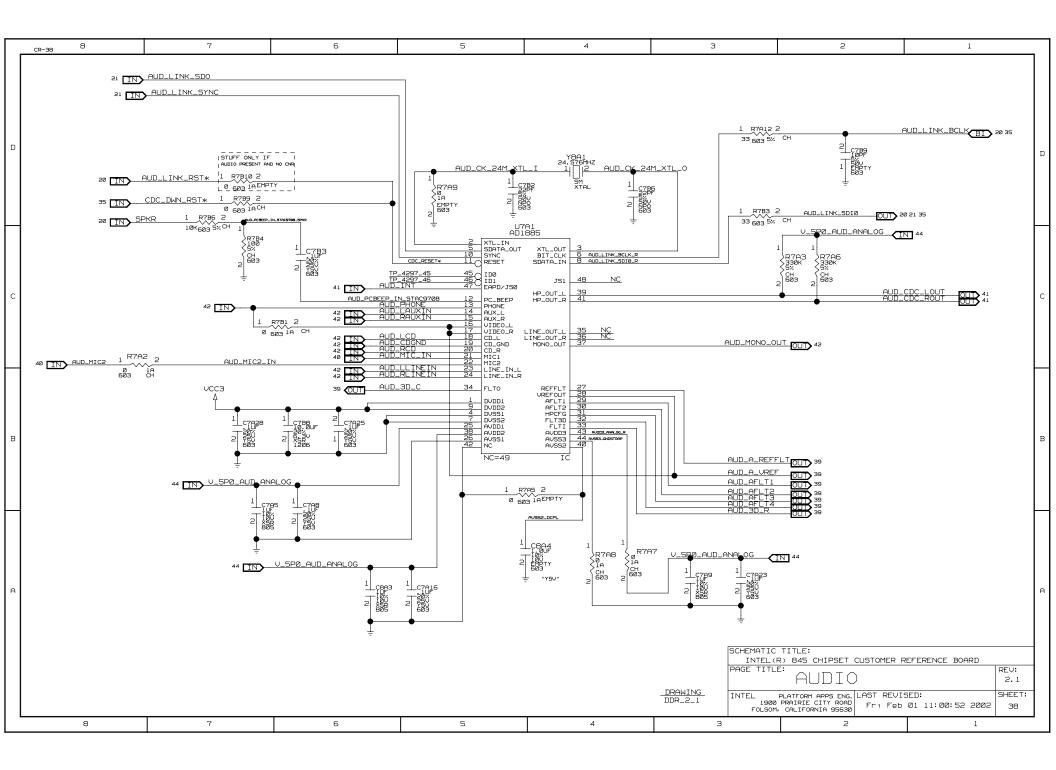

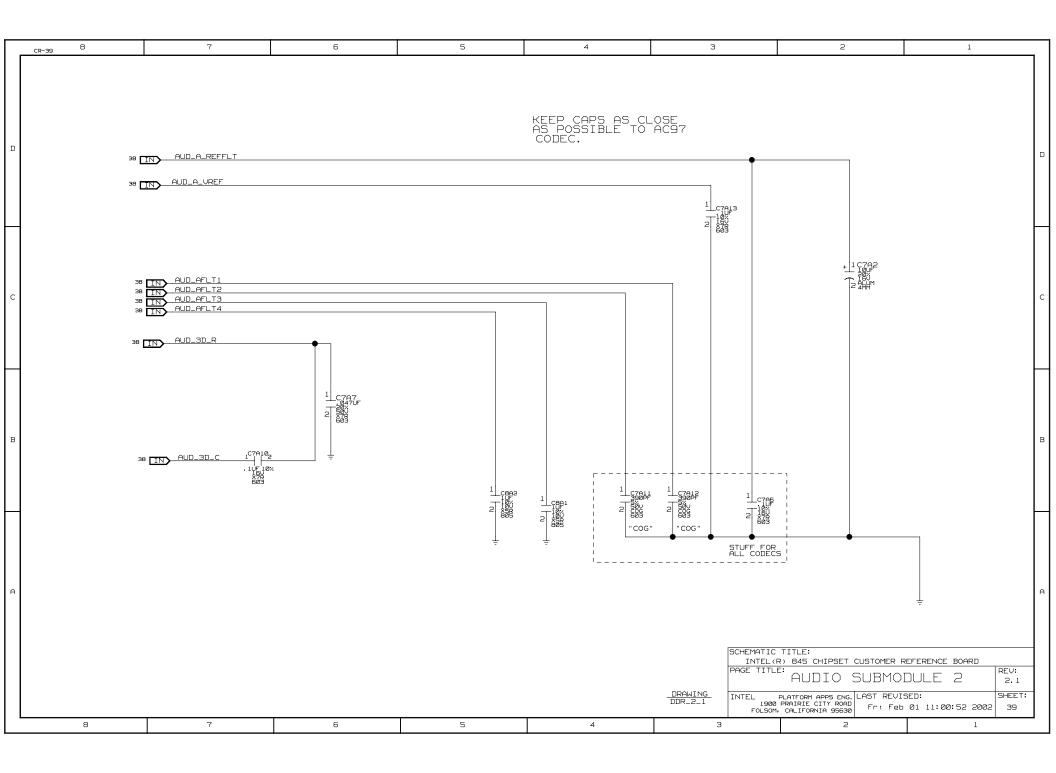

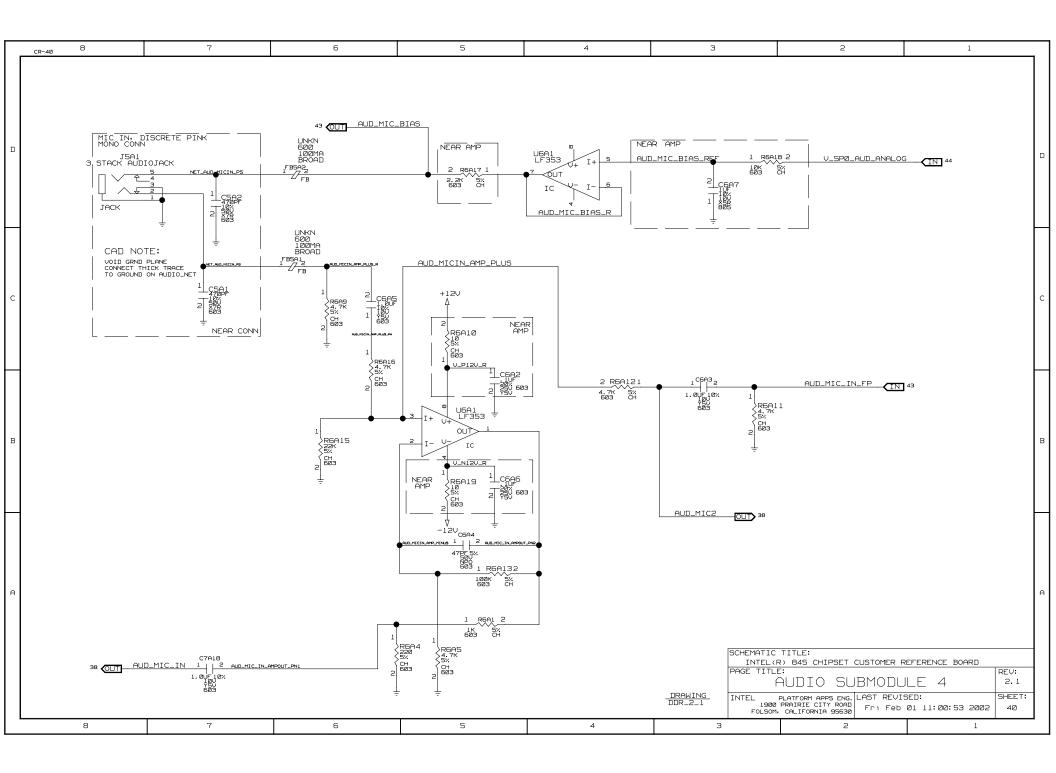

| 8.2                  |                                  |                                                                                                                                                            |            |

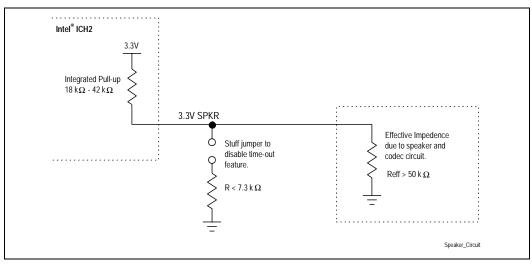

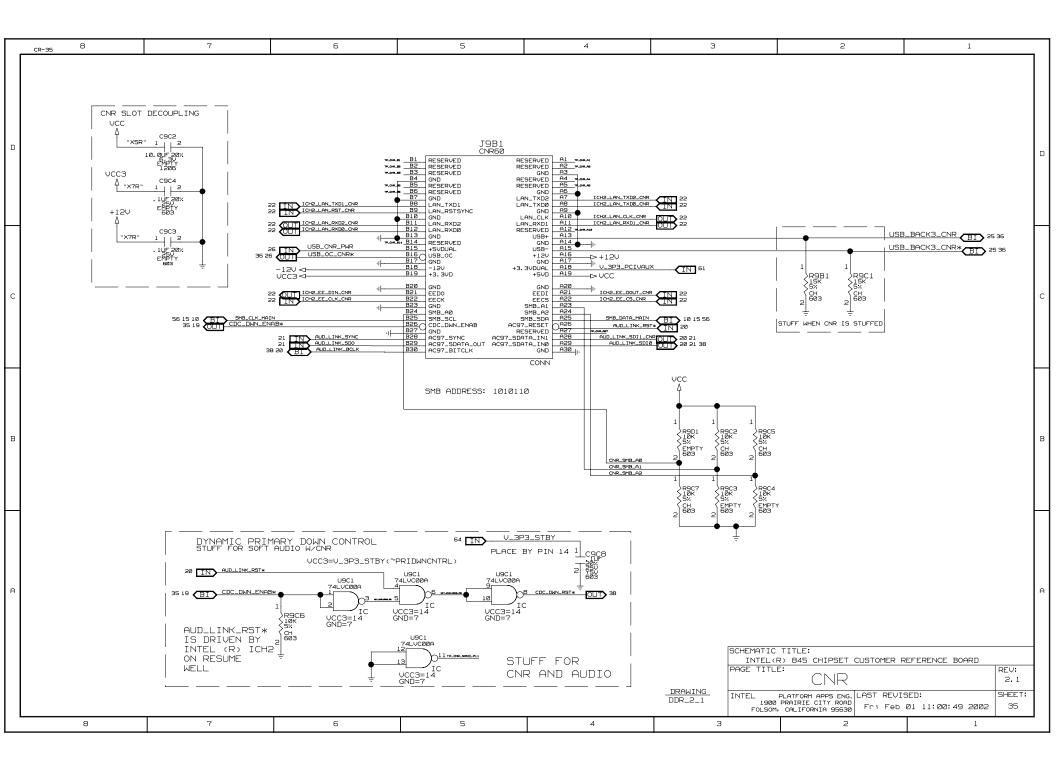

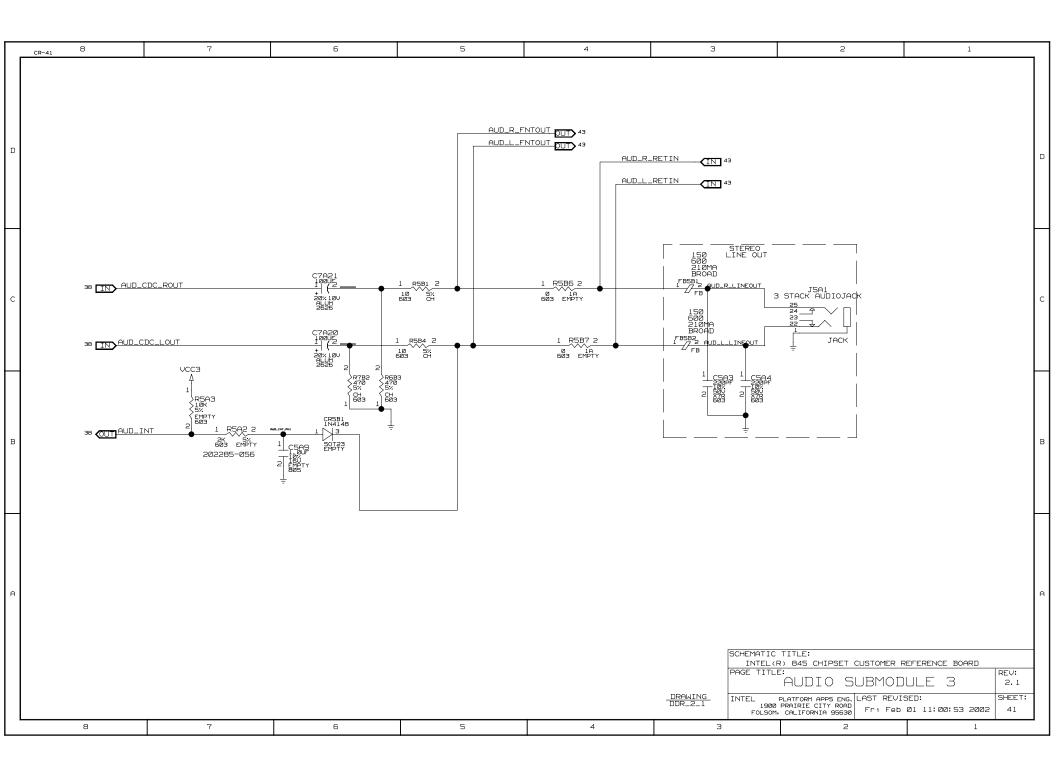

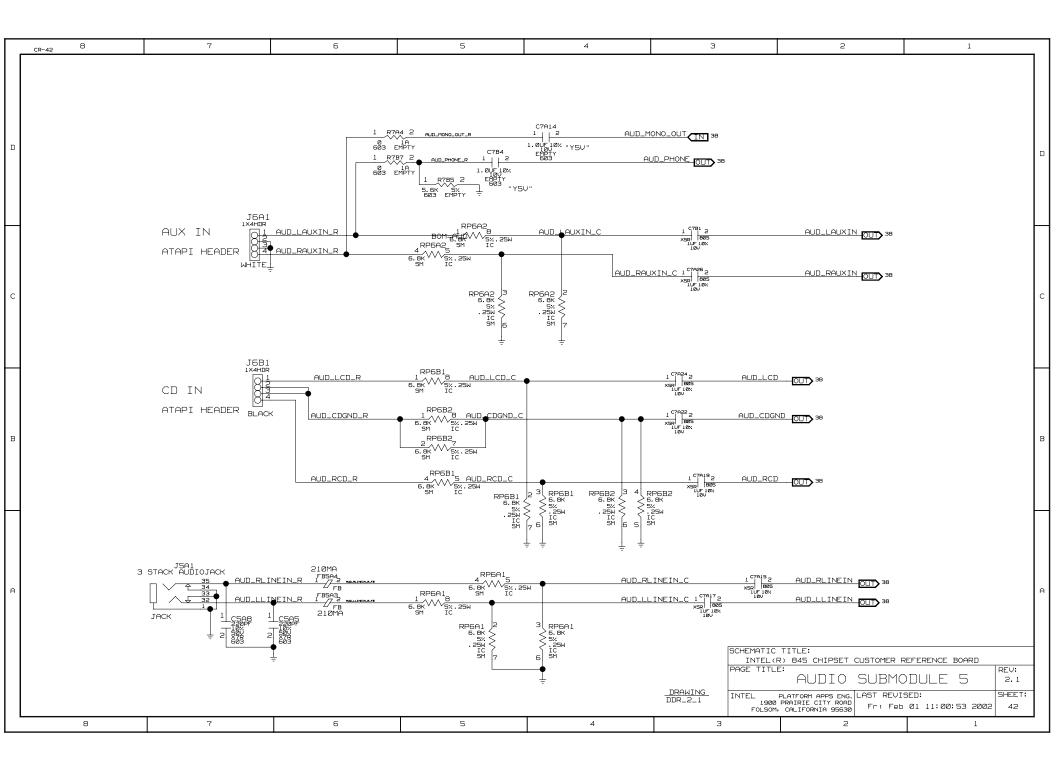

|                      | 8.2.1                            | AC '97 Audio Codec Detect Circuit and Configuration Options                                                                                                | 143        |

|                      | 8.2.2                            | Valid Codec Configurations                                                                                                                                 |            |

|                      | 8.2.3                            | SPKR Pin Consideration                                                                                                                                     |            |

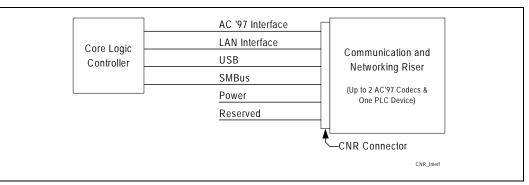

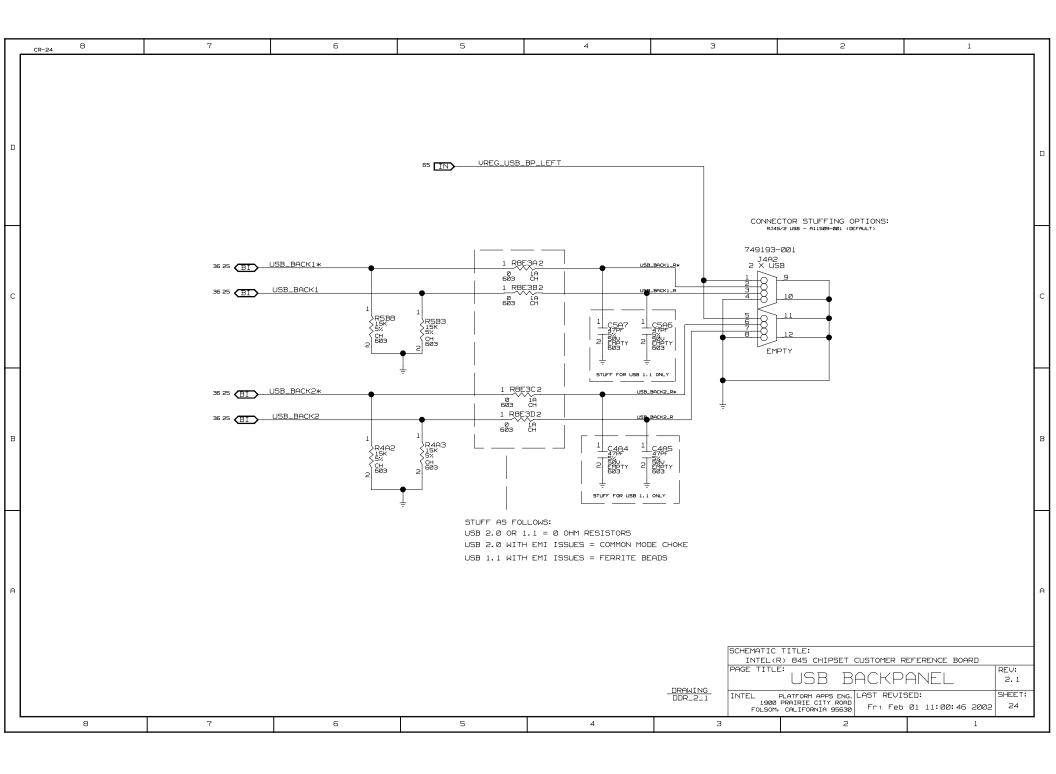

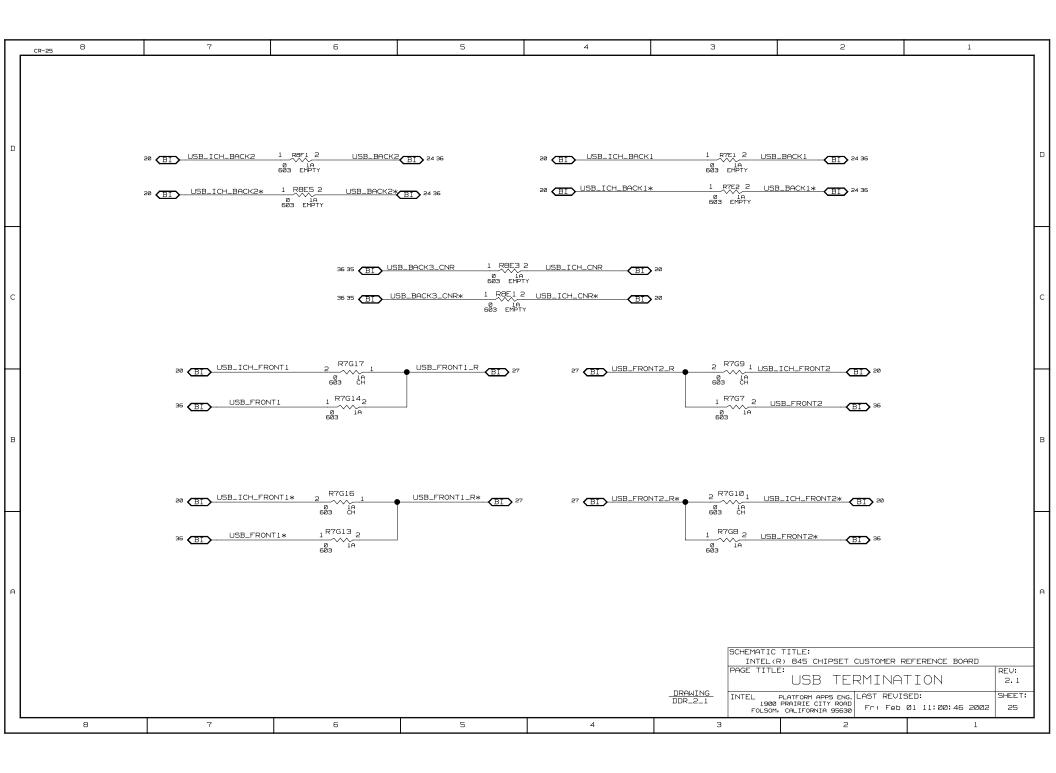

| 8.3                  |                                  |                                                                                                                                                            |            |

| 8.4                  |                                  |                                                                                                                                                            |            |

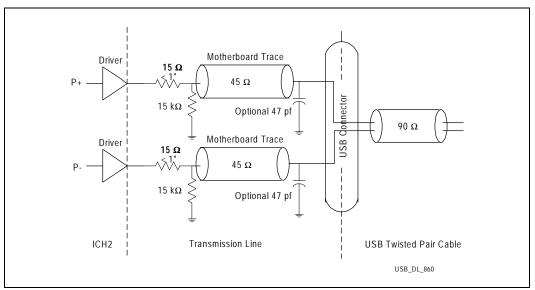

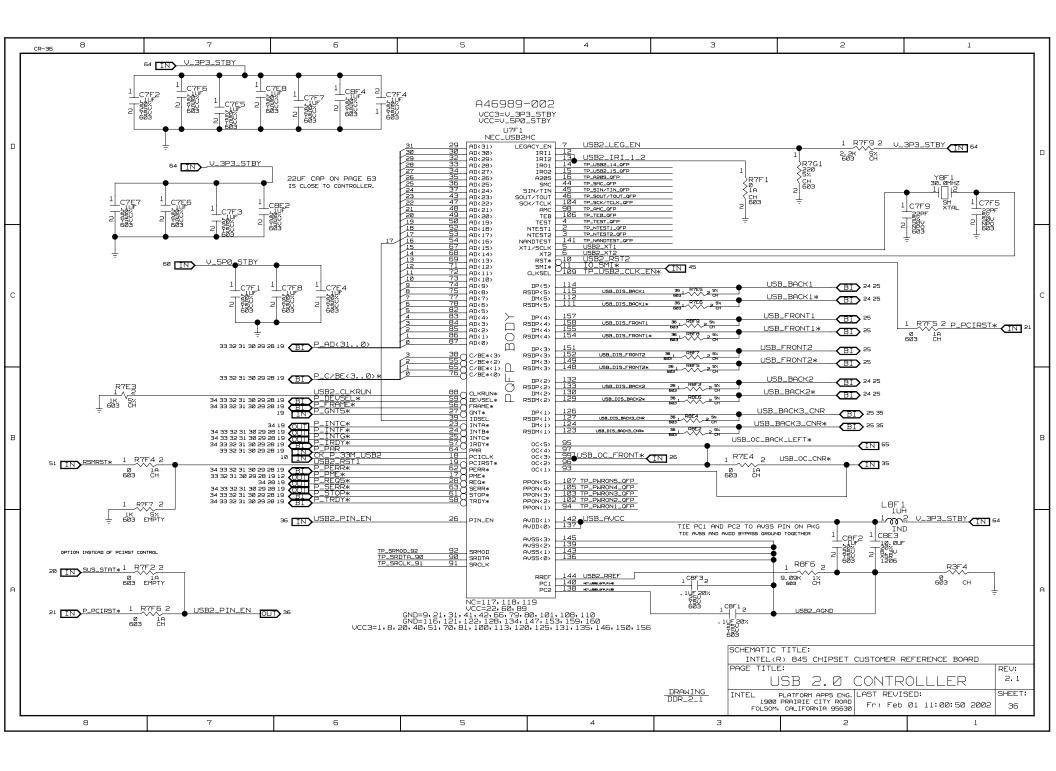

|                      | 8.4.1                            | Using Native USB interface                                                                                                                                 | 149        |

|                      | 8.4.2                            | Disabling the Native USB Interface of Intel <sup>®</sup> ICH2                                                                                              | 150        |

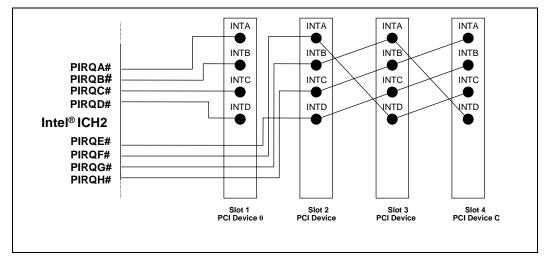

| 8.5                  | IOAPIC                           | Design Recommendation                                                                                                                                      | 151        |

|                      | 8.5.1                            | PIRQ Routing Example                                                                                                                                       | 151        |

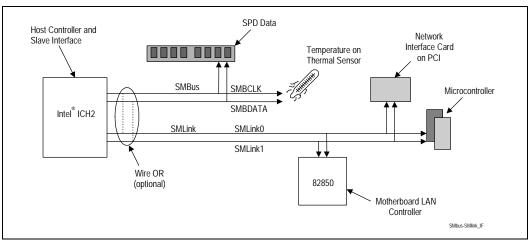

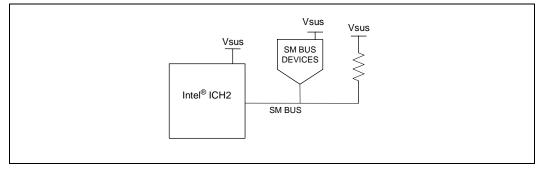

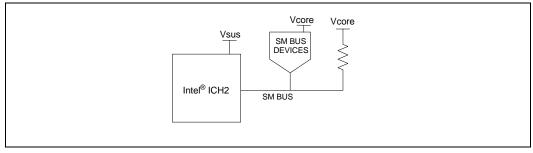

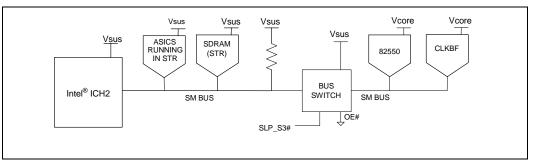

| 8.6                  | SMBus/                           | SMLink Interface                                                                                                                                           | 152        |

|                      | 8.6.1                            | SMBus Architecture & Design Considerations                                                                                                                 | 153        |

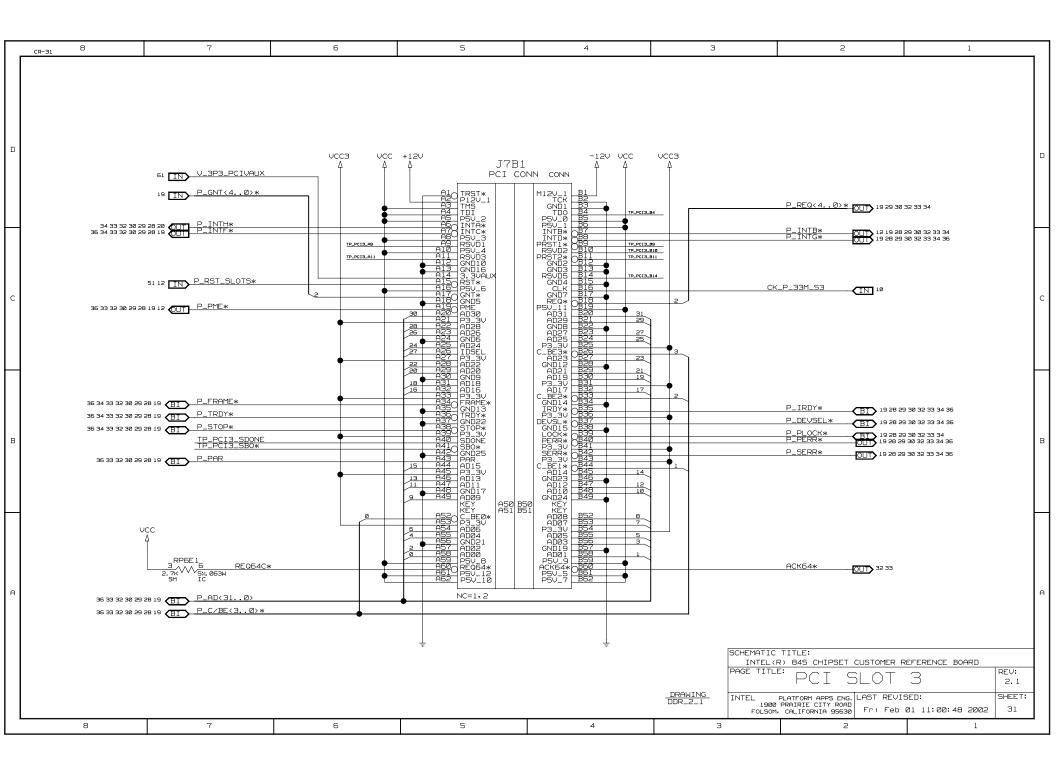

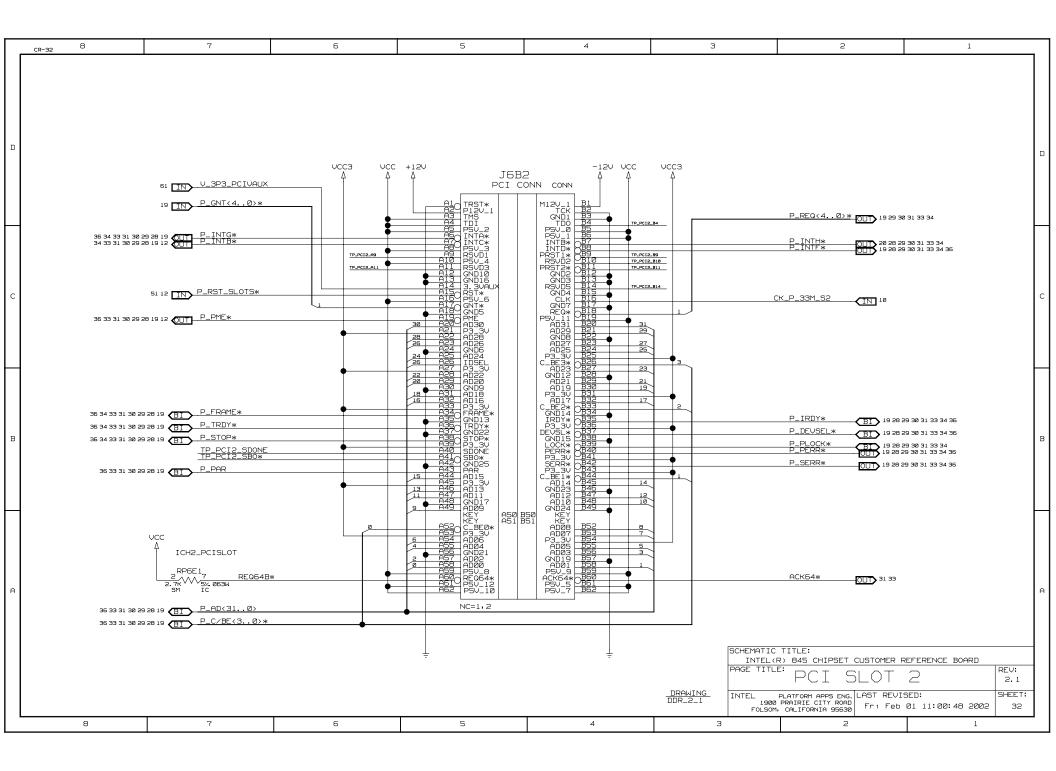

| 8.7                  | PCI                              |                                                                                                                                                            | 156        |

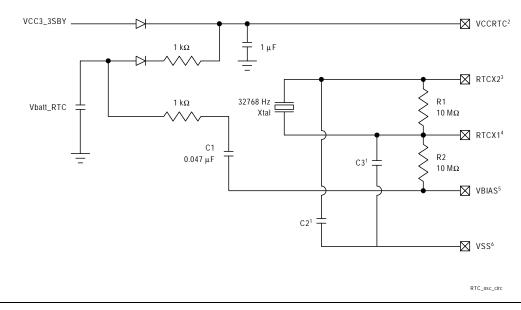

| 8.8                  | RTC                              |                                                                                                                                                            | 156        |

|                      | 8.8.1                            | RTC Crystal                                                                                                                                                | 156        |

|                      | 8.8.2                            | External Capacitors                                                                                                                                        |            |

|                      | 8.8.3                            | RTC Layout Considerations                                                                                                                                  | 158        |

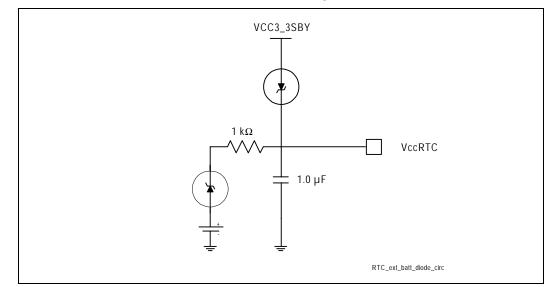

|                      | 8.8.4                            | RTC External Battery Connection                                                                                                                            |            |

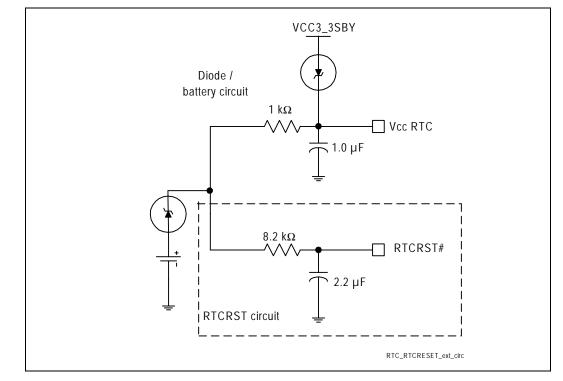

|                      | 8.8.5                            | RTC External RTCRST Circuit                                                                                                                                |            |

|                      | 8.8.6                            | RTC Routing Guidelines                                                                                                                                     |            |

|                      | 8.8.7                            | VBIAS DC Voltage and Noise Measurements                                                                                                                    |            |

|                      | 8.8.8                            | Power-Well Isolation Control Strap Requirements                                                                                                            |            |

| 8.9                  | •                                | /out Guidelines                                                                                                                                            |            |

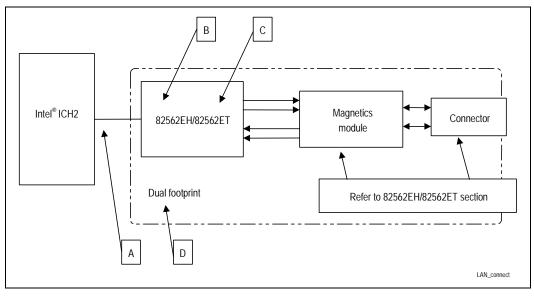

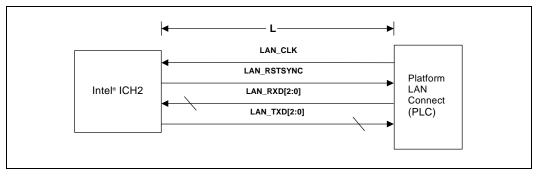

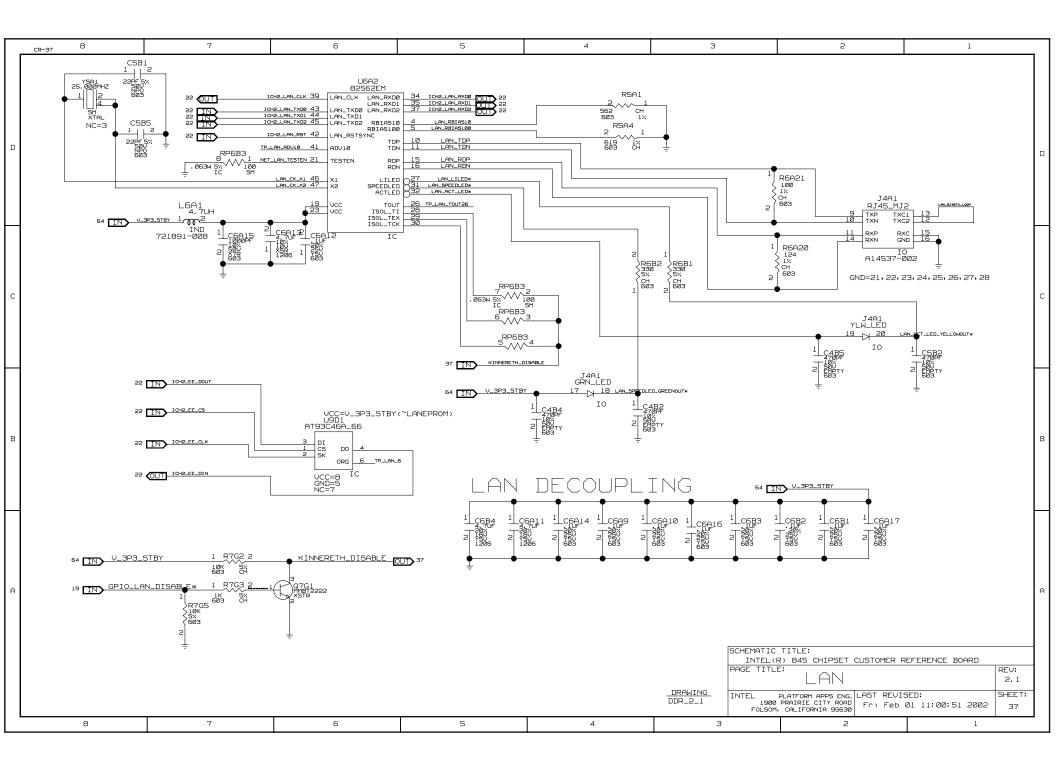

|                      | 8.9.1                            | Intel <sup>®</sup> ICH2—Platform LAN Connect Guidelines                                                                                                    |            |

|                      |                                  | 8.9.1.1 Bus Topologies                                                                                                                                     |            |

|                      |                                  | 8.9.1.2 Point-to-point Interconnect                                                                                                                        | 163        |

7

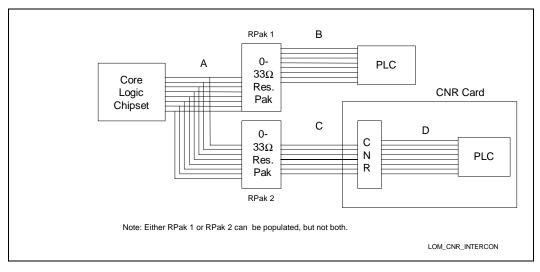

8

|    |         |                        | 8.9.1.3                | LOM /CNR Interconnect                                                      | .163 |

|----|---------|------------------------|------------------------|----------------------------------------------------------------------------|------|

|    |         |                        | 8.9.1.4                | Signal Routing and Layout                                                  | .164 |

|    |         |                        | 8.9.1.5                | Crosstalk Consideration                                                    | .164 |

|    |         |                        | 8.9.1.6                | Impedances                                                                 | .164 |

|    |         |                        | 8.9.1.7                | Line Termination                                                           | .164 |

|    |         | 8.9.2                  | General L              | AN Routing Guidelines and Considerations                                   | .165 |

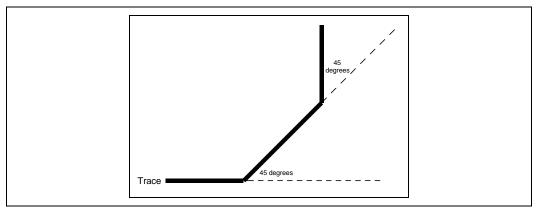

|    |         |                        | 8.9.2.1                | General Trace Routing Considerations                                       |      |

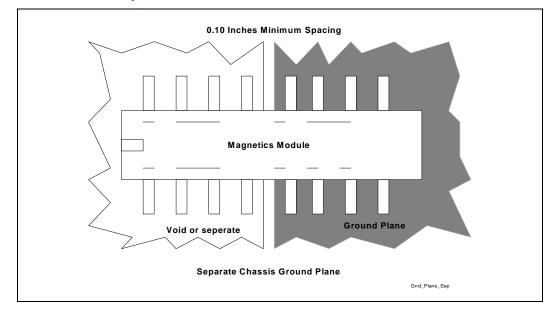

|    |         |                        | 8.9.2.2                | Power and Ground Connections                                               | .167 |

|    |         |                        | 8.9.2.3                | Common Physical Layout Issues                                              | .169 |

|    |         | 8.9.3                  | Intel <sup>®</sup> 825 | 62EH Home/PNA* Guidelines                                                  | .170 |

|    |         |                        | 8.9.3.1                | Power and Ground Connections                                               | .171 |

|    |         |                        | 8.9.3.2                | Guidelines for Intel <sup>®</sup> 82562EH Component Placement              | .171 |

|    |         |                        | 8.9.3.3                | Crystals and Oscillators                                                   | .171 |

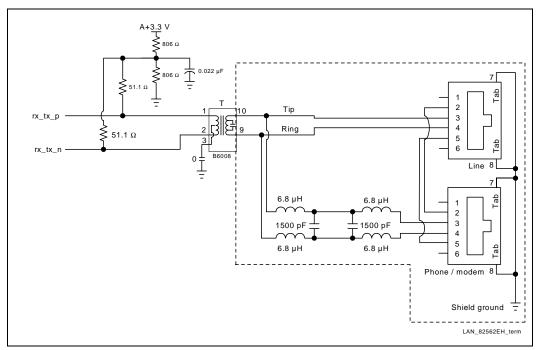

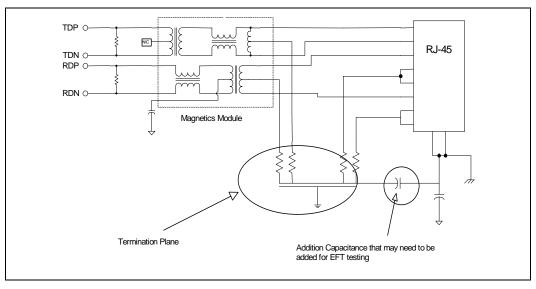

|    |         |                        | 8.9.3.4                | Phoneline HPNA Termination                                                 | .171 |

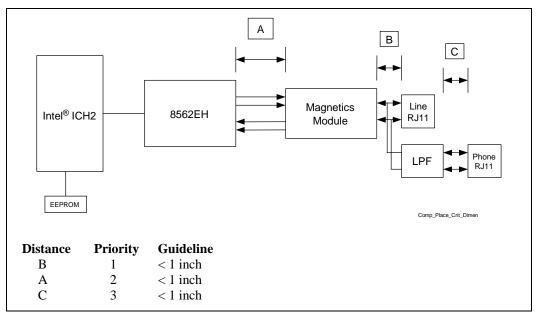

|    |         |                        | 8.9.3.5                | Critical Dimensions                                                        |      |

|    |         | 8.9.4                  | Intel <sup>®</sup> 825 | 62ET / 82562EM Guidelines                                                  | .174 |

|    |         |                        | 8.9.4.1                | Guidelines for Intel <sup>®</sup> 82562ET / 82562EM Component<br>Placement | .174 |

|    |         |                        | 8.9.4.2                | Crystals and Oscillators                                                   | .174 |

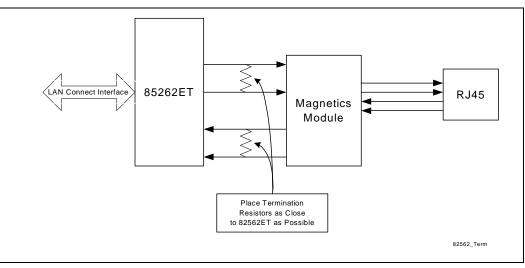

|    |         |                        | 8.9.4.3                | Intel® 82562ET / 82562EM Termination Resistors                             | .175 |

|    |         |                        | 8.9.4.4                | Critical Dimensions                                                        | .175 |

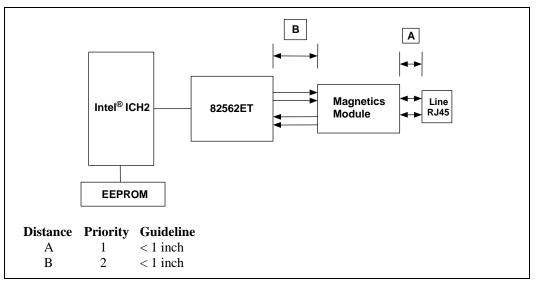

|    |         |                        | 8.9.4.5                | Distance from Intel <sup>®</sup> 82562ET to Magnetics Module               | .176 |

|    |         |                        | 8.9.4.6                | Reducing Circuit Inductance                                                | .176 |

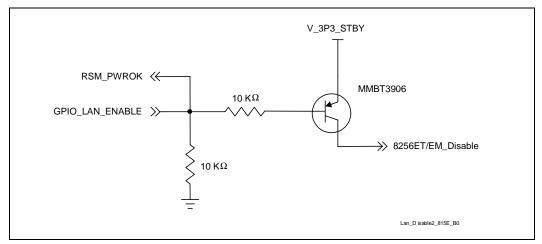

|    |         | 8.9.5                  | Intel <sup>®</sup> 825 | 62ET/82562EM Disabling Method                                              | .178 |

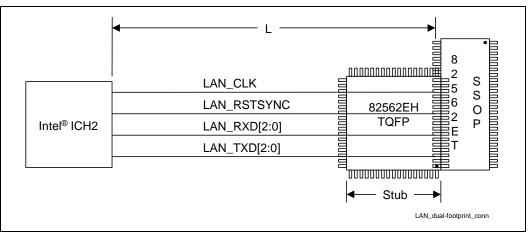

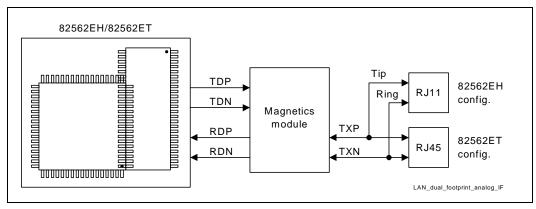

|    |         | 8.9.6                  | Intel <sup>®</sup> 825 | 62ET / 82562EH Dual Footprint Guidelines                                   | .179 |

|    | 8.10    | Intel <sup>®</sup> ICF | 12 Decoup              | ling Recommendations                                                       | .181 |

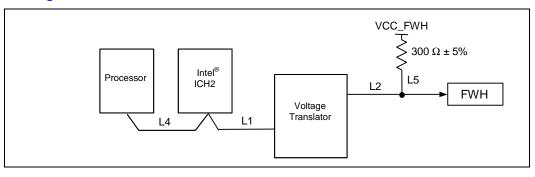

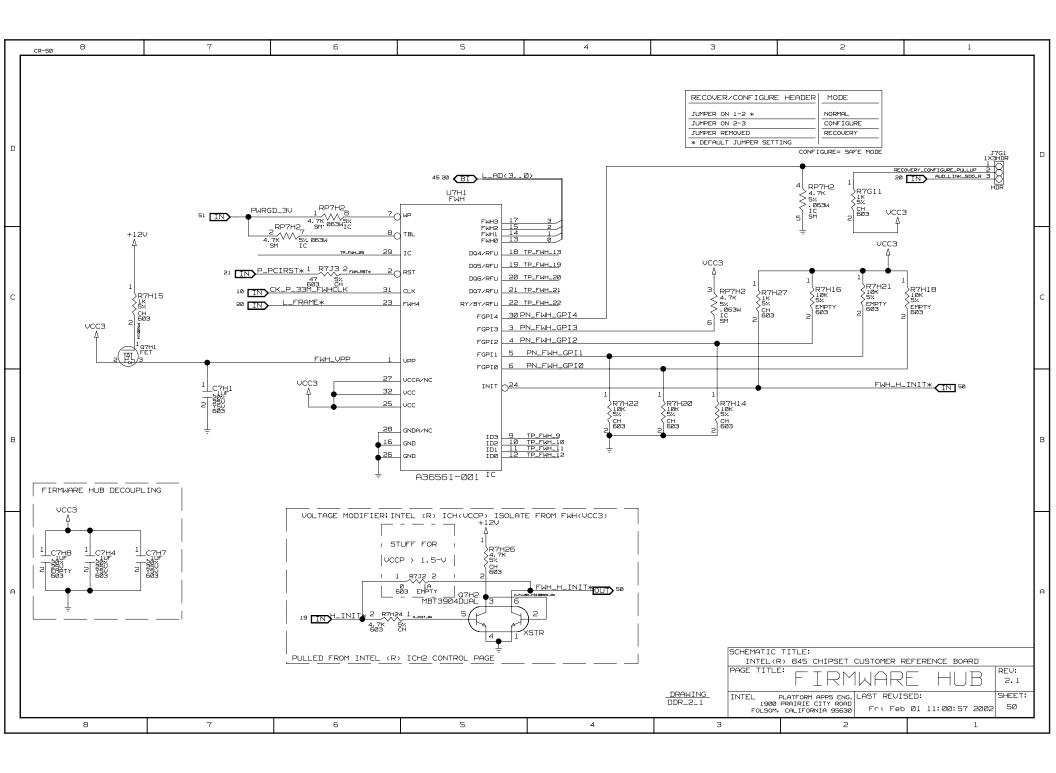

| 9  | FWH     | Guidelines             |                        |                                                                            | .183 |

|    | 9.1     | FWH Dec                | coupling               |                                                                            | .183 |

|    | 9.2     |                        |                        | gramming                                                                   |      |

|    | 9.3     |                        | -                      | Guidelines                                                                 |      |

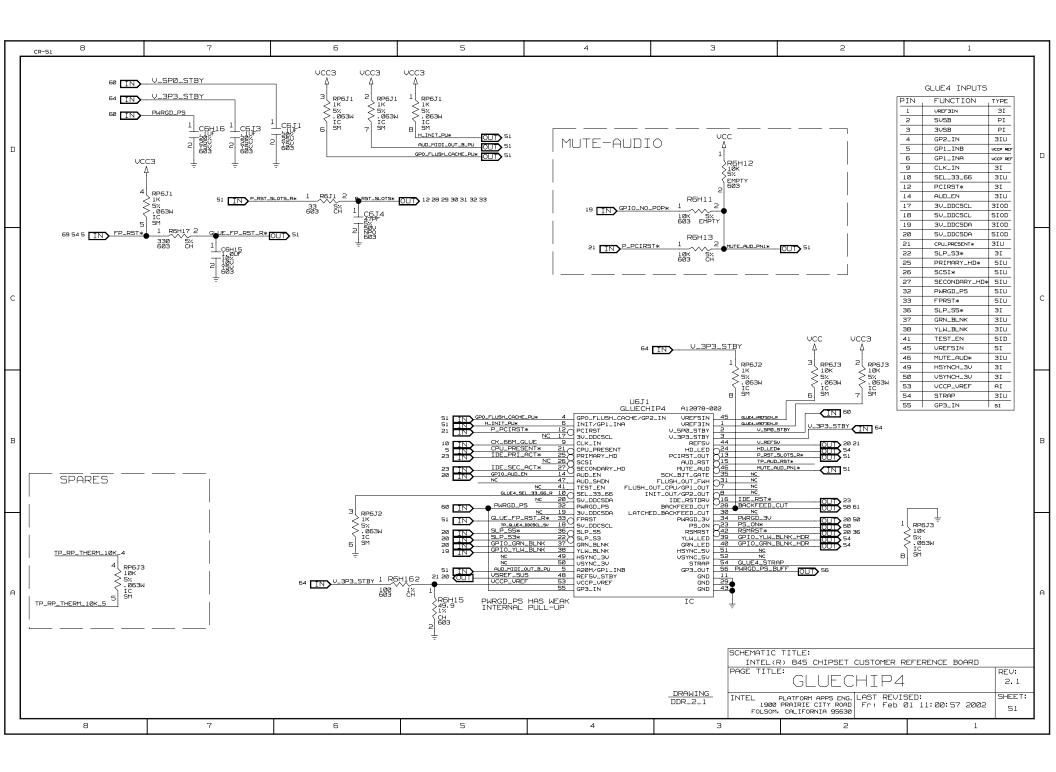

| 10 |         |                        | -                      |                                                                            |      |

| 10 |         |                        | -                      |                                                                            |      |

|    | 10.1    | •                      |                        |                                                                            |      |

|    | 10.2    | Discrete I             | Logic                  |                                                                            | .185 |

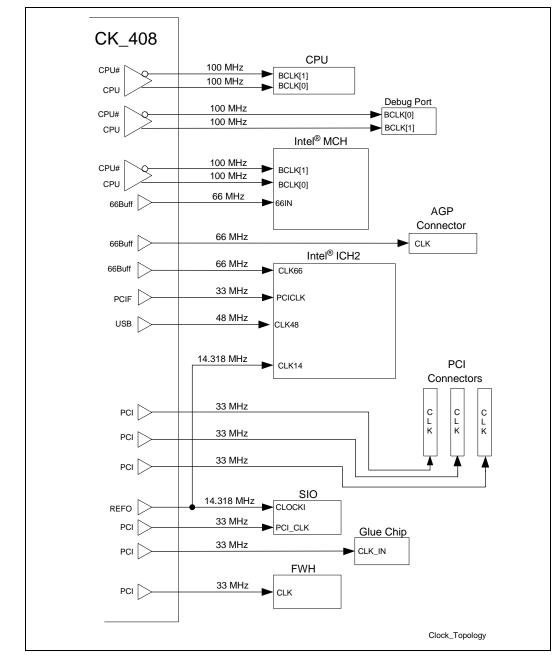

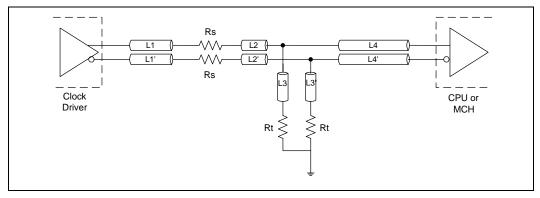

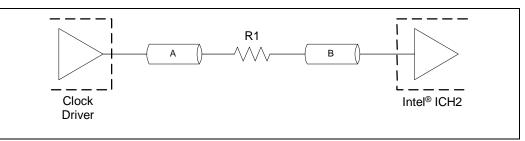

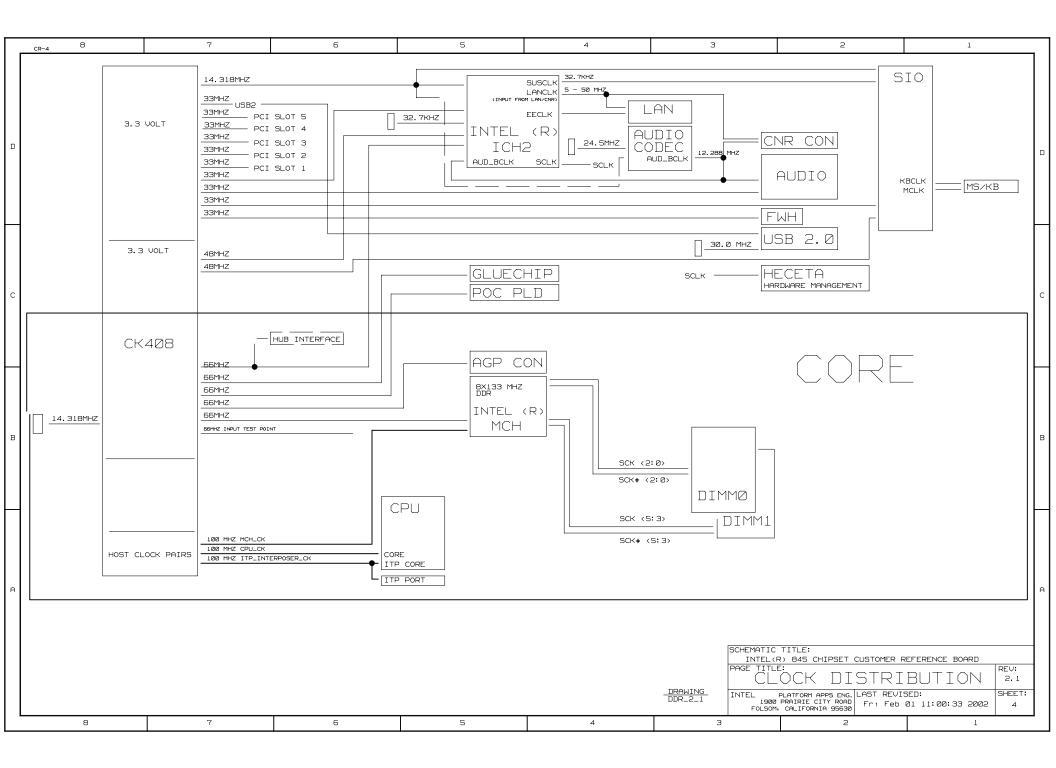

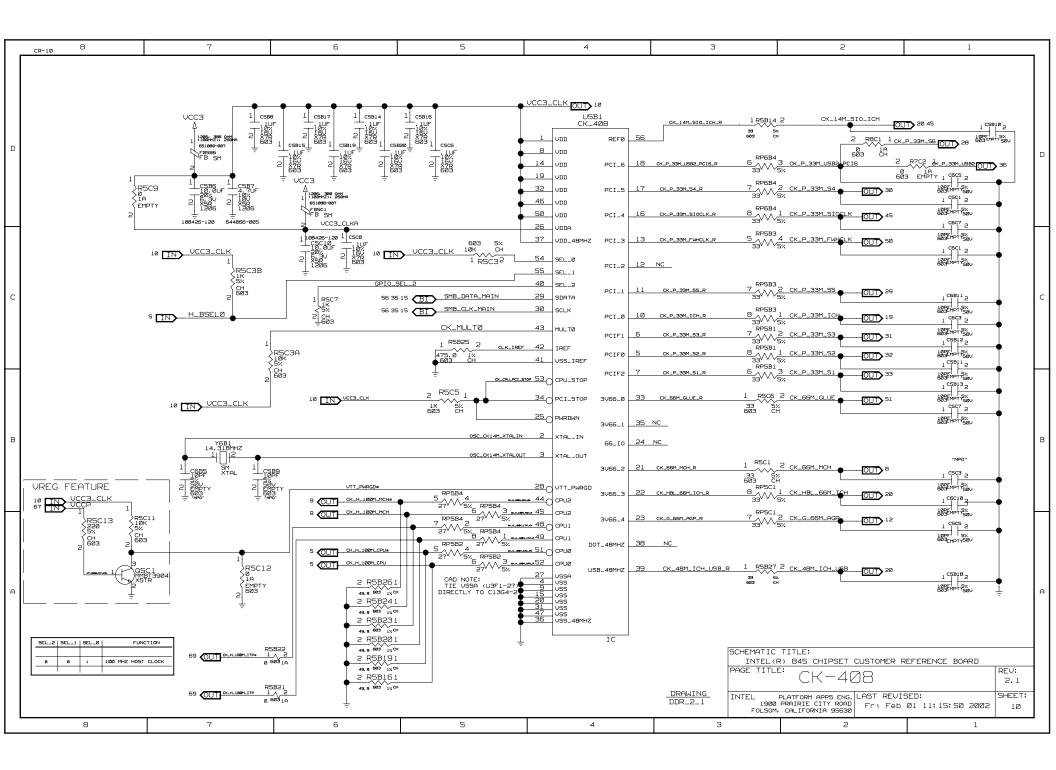

| 11 | Platfor | m Clock R              | outing Gui             | delines                                                                    | .187 |

|    | 11.1    | Clock Ge               | neration               |                                                                            | .187 |

|    | 11.2    | Clock Gro              | ologoT que             | ogy and Layout Routing Guidelines                                          | .190 |

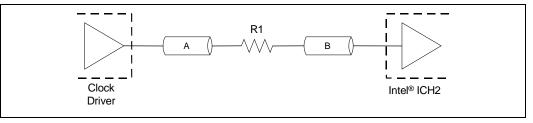

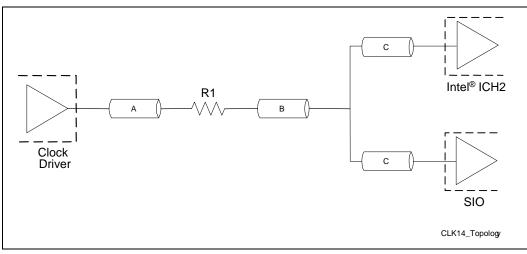

|    |         |                        |                        | _K Clock Group                                                             |      |

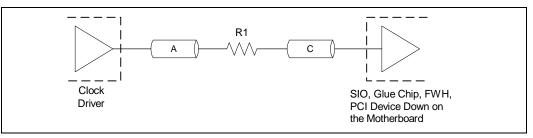

|    |         |                        |                        | ock Group                                                                  |      |

|    |         |                        |                        | Clock Group                                                                |      |

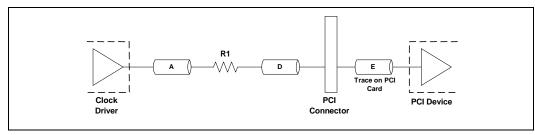

|    |         | 11.2.4                 |                        | lock Group                                                                 |      |

|    |         | 11.2.5                 |                        | ock Group                                                                  |      |

|    |         | 11.2.6                 |                        | Clock Group                                                                |      |

|    | 11.3    |                        |                        | pling                                                                      |      |

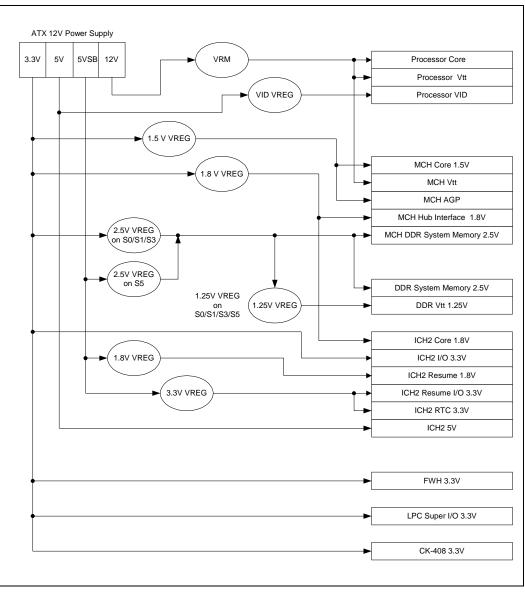

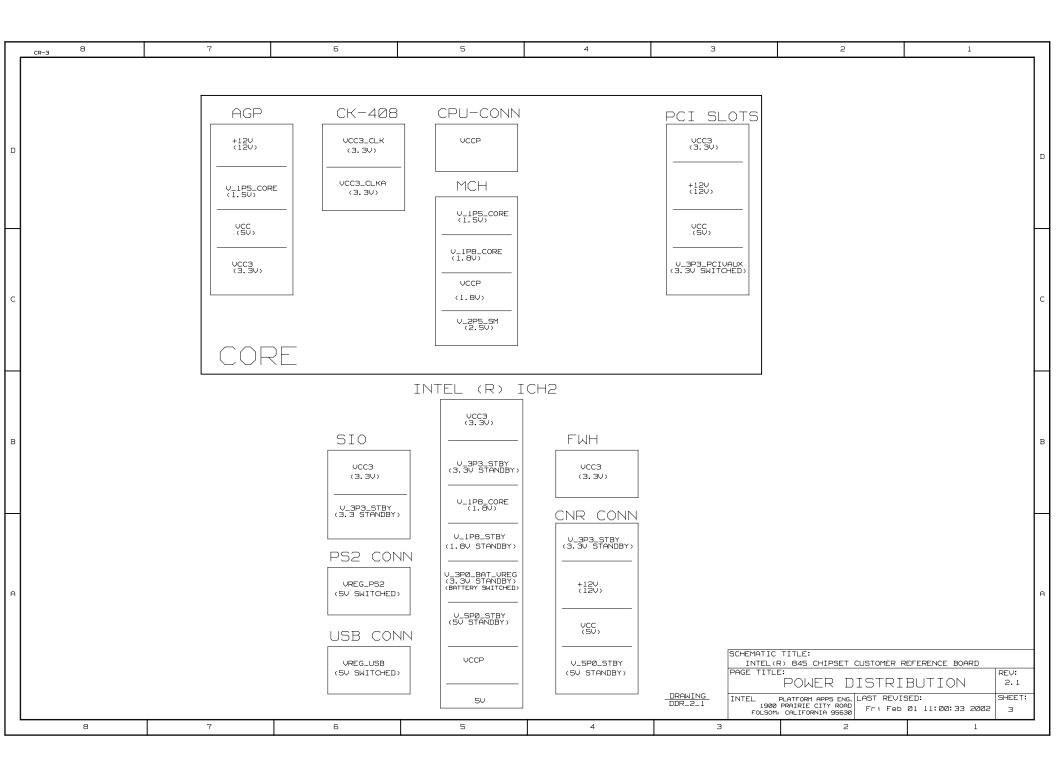

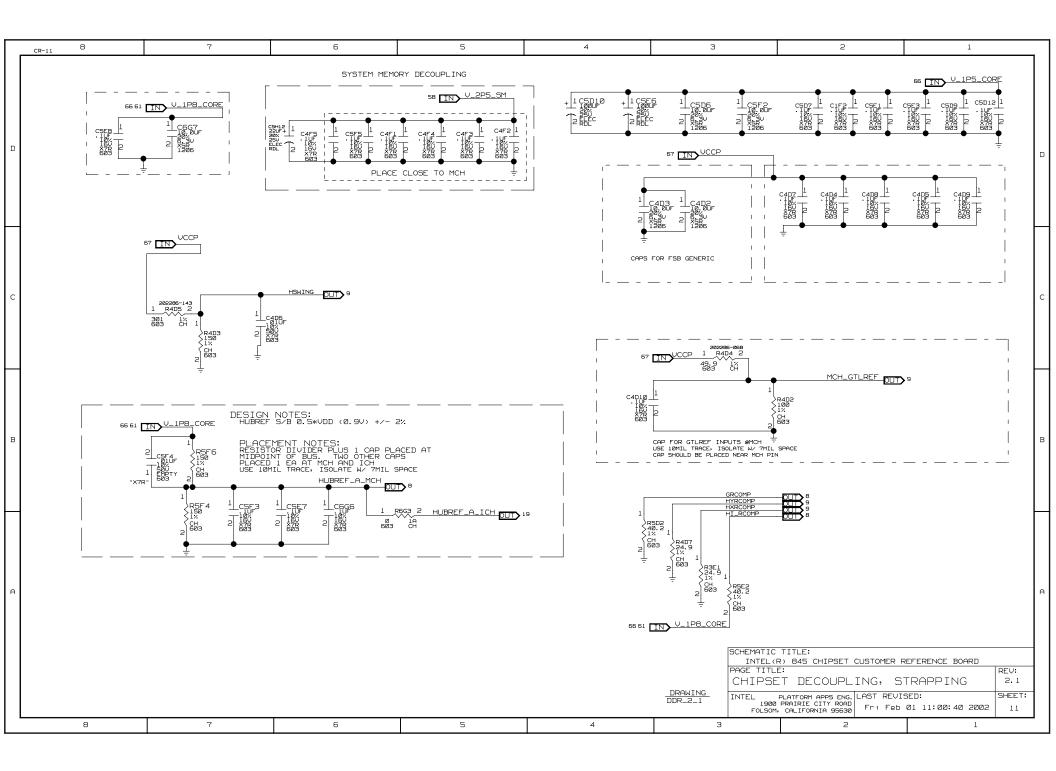

| 12 | Platfor | m Power G              | Guidelines             | · · · · ·                                                                  | .201 |

|    | 12.1    | Definition             | S                      |                                                                            | .201 |

|    | 12.1    |                        |                        | )                                                                          |      |

|    |         | -                      |                        |                                                                            |      |

|    | 12.3    |                        |                        | Delivery                                                                   |      |

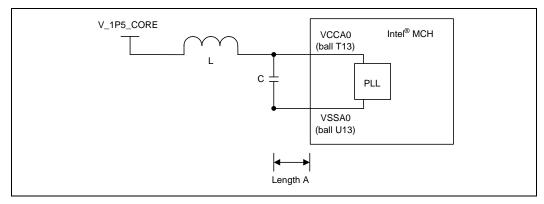

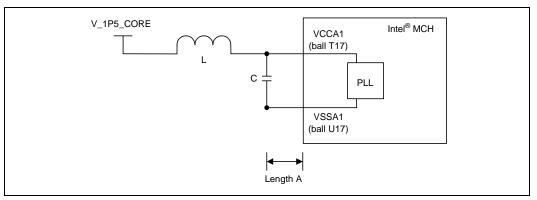

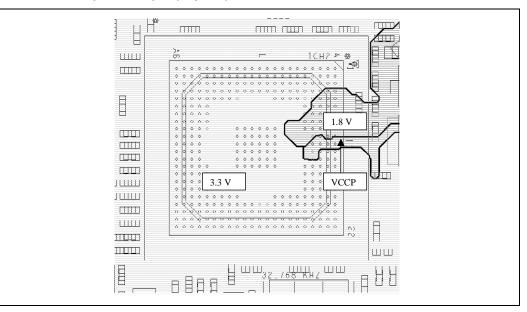

|    |         | 12.3.1                 | Intel <sup>~</sup> MC  | H PLL Power Delivery                                                       | .204 |

|    |                              | 12.3.2 Intel <sup>®</sup> MCH 1.5 V Power Delivery<br>12.3.3 Intel <sup>®</sup> MCH 1.5 V Decoupling                                                                                                                                                                                                                                                                                                                 | .206                                                                                                                                                                         |

|----|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                              | 12.3.3 Intel <sup>®</sup> MCH 1.3 V Decoupling                                                                                                                                                                                                                                                                                                                                                                       | 201                                                                                                                                                                          |

|    | 12.4                         | Intel <sup>®</sup> ICH2 Power Delivery                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                              |

|    | 12.4                         | 12.4.1 1.8 V/3.3 V Power Sequencing                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                              |

|    |                              | 12.4.1 1.6 V/S.5 V Power Sequencing<br>12.4.2 3.3 V/V <sub>SREF</sub> Sequencing                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                              |

|    |                              | 12.4.2 5.5 V/V <sub>5REF</sub> Sequencing<br>12.4.3 ATX Power Supply PWRGOOD Requirements                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                              |

|    |                              | 12.4.4 Power Management Signals                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                              |

|    | 12.5                         | CK 408 Power Delivery                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                              |

|    | 12.5                         | 12.5.1 CK_408 Power Sequencing                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                              |

|    |                              | 12.5.1 CK_408 Power Sequencing                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                              |

|    | 12.6                         | Power Supply PS_ON Considerations                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                              |

| 13 | Platfor                      | m Mechanical Guidelines                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                              |

| 10 |                              |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                              |

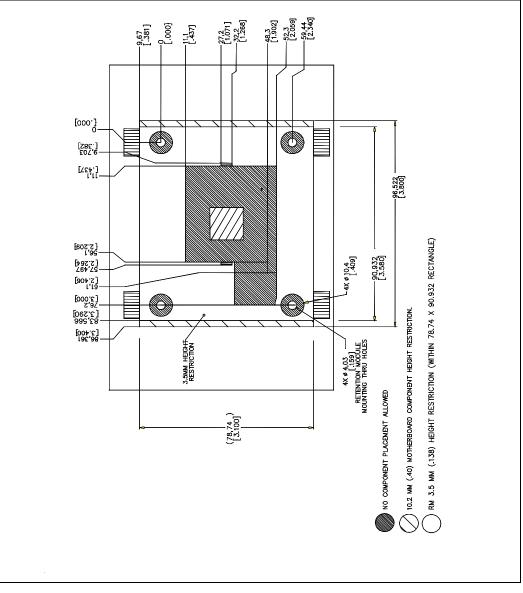

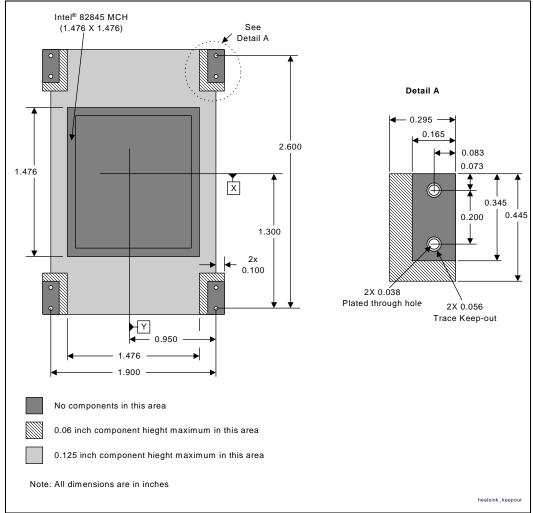

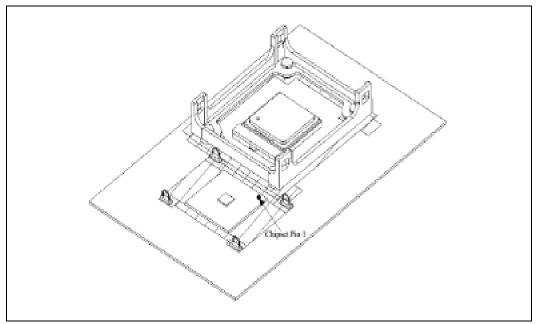

|    | 13.1                         | Intel <sup>®</sup> MCH Retention Mechanism and Keep-Outs                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                              |

| 14 |                              | natic Checklist                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                              |

|    | 14.1                         | Host Interface                                                                                                                                                                                                                                                                                                                                                                                                       | .221                                                                                                                                                                         |

|    | 14.2                         | Memory Interface                                                                                                                                                                                                                                                                                                                                                                                                     | .225                                                                                                                                                                         |

|    |                              | 14.2.1 DDR-SDRAM                                                                                                                                                                                                                                                                                                                                                                                                     | .225                                                                                                                                                                         |

|    | 14.3                         | AGP Interface                                                                                                                                                                                                                                                                                                                                                                                                        | .227                                                                                                                                                                         |

|    | 14.4                         | Hub Interface                                                                                                                                                                                                                                                                                                                                                                                                        | .229                                                                                                                                                                         |

|    | 14.5                         | Intel <sup>®</sup> ICH2 Interface                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                              |

|    | 14.6                         | Miscellaneous Intel <sup>®</sup> MCH Signals                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                              |

|    | 14.7                         | Clock Interface CK_408                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                              |

|    |                              |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                              |

|    | 14.8                         | Power and Ground                                                                                                                                                                                                                                                                                                                                                                                                     | .240                                                                                                                                                                         |

| 15 | Intel <sup>®</sup> 8         | 345 Chipset Design Layout Checklist                                                                                                                                                                                                                                                                                                                                                                                  | .241                                                                                                                                                                         |

|    |                              | System Bus                                                                                                                                                                                                                                                                                                                                                                                                           | .241                                                                                                                                                                         |

|    | 15.1                         | - /                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                              |

|    | 15.1                         | 15.1.1 System Bus                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                              |

|    | 15.1                         | •                                                                                                                                                                                                                                                                                                                                                                                                                    | .241                                                                                                                                                                         |

|    | 15.1<br>15.2                 | 15.1.1 System Bus                                                                                                                                                                                                                                                                                                                                                                                                    | .241<br>.243                                                                                                                                                                 |

|    |                              | <ul><li>15.1.1 System Bus</li><li>15.1.2 Decoupling, V<sub>REF</sub>, and Filtering</li></ul>                                                                                                                                                                                                                                                                                                                        | .241<br>.243<br>.245                                                                                                                                                         |

|    |                              | 15.1.1       System Bus         15.1.2       Decoupling, V <sub>REF</sub> , and Filtering         System Memory (DDR)                                                                                                                                                                                                                                                                                                | .241<br>.243<br>.245<br>.245                                                                                                                                                 |

|    | 15.2                         | 15.1.1       System Bus         15.1.2       Decoupling, V <sub>REF</sub> , and Filtering.         System Memory (DDR)                                                                                                                                                                                                                                                                                               | .241<br>.243<br>.245<br>.245<br>.248                                                                                                                                         |

|    | 15.2                         | 15.1.1       System Bus         15.1.2       Decoupling, V <sub>REF</sub> , and Filtering         System Memory (DDR)                                                                                                                                                                                                                                                                                                | .241<br>.243<br>.245<br>.245<br>.248<br>.248                                                                                                                                 |

|    | 15.2                         | 15.1.1       System Bus         15.1.2       Decoupling, V <sub>REF</sub> , and Filtering         System Memory (DDR)                                                                                                                                                                                                                                                                                                | .241<br>.243<br>.245<br>.245<br>.245<br>.248<br>.248<br>.248                                                                                                                 |

|    | 15.2                         | 15.1.1       System Bus         15.1.2       Decoupling, V <sub>REF</sub> , and Filtering.         System Memory (DDR)                                                                                                                                                                                                                                                                                               | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.248                                                                                                                 |

|    | 15.2<br>15.3                 | 15.1.1System Bus15.1.2Decoupling, VREF, and Filtering.System Memory (DDR)15.2.12-DIMM DDR-SDRAM.AGP15.3.11X Signals:15.3.22X/4X Signals:15.3.3Decoupling, Compensation, and VREF                                                                                                                                                                                                                                     | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.248<br>.249<br>.250                                                                                                 |

|    | 15.2<br>15.3                 | 15.1.1       System Bus         15.1.2       Decoupling, V <sub>REF</sub> , and Filtering.         System Memory (DDR)                                                                                                                                                                                                                                                                                               | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.248<br>.249<br>.250<br>.250                                                                                         |

|    | 15.2<br>15.3                 | 15.1.1       System Bus         15.1.2       Decoupling, V <sub>REF</sub> , and Filtering.         System Memory (DDR)                                                                                                                                                                                                                                                                                               | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.248<br>.249<br>.250<br>.250<br>.250                                                                                 |

|    | 15.2<br>15.3<br>15.4         | 15.1.1System Bus15.1.2Decoupling, $V_{REF}$ , and Filtering.System Memory (DDR)15.2.12-DIMM DDR-SDRAM.AGP15.3.11X Signals:15.3.22X/4X Signals:15.3.3Decoupling, Compensation, and $V_{REF}$ .HUB Interface15.4.1Interface Signals.15.4.2Decoupling, Compensation, and $V_{REF}$ .Clocks: CK_40815.5.1Decoupling.                                                                                                     | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.248<br>.249<br>.250<br>.250<br>.250<br>.251                                                                         |

|    | 15.2<br>15.3<br>15.4         | 15.1.1System Bus15.1.2Decoupling, $V_{REF}$ , and Filtering.System Memory (DDR)15.2.12-DIMM DDR-SDRAM.AGP15.3.11X Signals:15.3.22X/4X Signals:15.3.3Decoupling, Compensation, and $V_{REF}$ .HUB Interface15.4.1Interface Signals.15.4.2Decoupling, Compensation, and $V_{REF}$ .Clocks: CK_408                                                                                                                      | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.248<br>.249<br>.250<br>.250<br>.250<br>.251<br>.253                                                                 |

|    | 15.2<br>15.3<br>15.4<br>15.5 | 15.1.1System Bus15.1.2Decoupling, $V_{REF}$ , and Filtering.System Memory (DDR)15.2.12-DIMM DDR-SDRAM.AGP15.3.11X Signals:15.3.22X/4X Signals:15.3.3Decoupling, Compensation, and $V_{REF}$ .HUB Interface15.4.1Interface Signals.15.4.2Decoupling, Compensation, and $V_{REF}$ .Clocks: CK_40815.5.1Decoupling.                                                                                                     | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.249<br>.250<br>.250<br>.250<br>.251<br>.253<br>.253                                                                 |

|    | 15.2<br>15.3<br>15.4<br>15.5 | 15.1.1System Bus15.1.2Decoupling, $V_{REF}$ , and Filtering.System Memory (DDR)15.2.12-DIMM DDR-SDRAM.AGP15.3.11X Signals:15.3.22X/4X Signals:15.3.3Decoupling, Compensation, and $V_{REF}$ HUB Interface15.4.1Interface Signals.15.4.2Decoupling, Compensation, and $V_{REF}$ Clocks: CK_40815.5.1Decoupling.Intel <sup>®</sup> ICH2                                                                                | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.249<br>.250<br>.250<br>.250<br>.251<br>.253<br>.253<br>.253                                                         |

|    | 15.2<br>15.3<br>15.4<br>15.5 | 15.1.1System Bus15.1.2Decoupling, $V_{REF}$ , and Filtering.System Memory (DDR)15.2.12-DIMM DDR-SDRAM.AGP15.3.11X Signals:15.3.22X/4X Signals:15.3.3Decoupling, Compensation, and $V_{REF}$ HUB Interface15.4.1Interface Signals.15.4.2Decoupling, Compensation, and $V_{REF}$ Clocks: CK_40815.5.1Decoupling.Intel <sup>®</sup> ICH215.6.1IDE                                                                       | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.249<br>.250<br>.250<br>.250<br>.251<br>.253<br>.253<br>.253<br>.253                                                 |

|    | 15.2<br>15.3<br>15.4<br>15.5 | 15.1.1System Bus15.1.2Decoupling, $V_{REF}$ , and FilteringSystem Memory (DDR)15.2.12-DIMM DDR-SDRAMAGP15.3.11X Signals:15.3.22X/4X Signals:15.3.3Decoupling, Compensation, and $V_{REF}$ HUB Interface15.4.1Interface Signals.15.4.2Decoupling, Compensation, and $V_{REF}$ Clocks: CK_40815.5.1Decoupling.Intel <sup>®</sup> ICH215.6.1IDE.15.6.2AC '9715.6.3USB 1.115.6.4RTC                                      | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.248<br>.248<br>.249<br>.250<br>.250<br>.250<br>.251<br>.253<br>.253<br>.253<br>.253<br>.254<br>.254                 |

|    | 15.2<br>15.3<br>15.4<br>15.5 | 15.1.1System Bus15.1.2Decoupling, $V_{REF}$ , and FilteringSystem Memory (DDR)15.2.12-DIMM DDR-SDRAMAGP15.3.11X Signals:15.3.22X/4X Signals:15.3.3Decoupling, Compensation, and $V_{REF}$ HUB Interface15.4.1Interface Signals.15.4.2Decoupling, Compensation, and $V_{REF}$ Clocks: CK_40815.5.1Decoupling, Compensation, and $V_{REF}$ Intel <sup>®</sup> ICH215.6.1IDE15.6.2AC '9715.6.3USB 1.115.6.4RTC15.6.5LAN | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.248<br>.248<br>.249<br>.250<br>.250<br>.250<br>.251<br>.253<br>.253<br>.253<br>.253<br>.254<br>.254<br>.255         |

|    | 15.2<br>15.3<br>15.4<br>15.5 | 15.1.1System Bus15.1.2Decoupling, $V_{REF}$ , and Filtering.System Memory (DDR)15.2.12-DIMM DDR-SDRAM.AGP15.3.11X Signals:15.3.22X/4X Signals:15.3.3Decoupling, Compensation, and $V_{REF}$ .HUB Interface15.4.1Interface Signals.15.4.2Decoupling, Compensation, and $V_{REF}$ .Clocks: CK_40815.5.1Decoupling.Intel <sup>®</sup> ICH215.6.3USB 1.115.6.4RTC.15.6.5LAN.15.6.6Intel <sup>®</sup> ICH2 Decoupling.    | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.248<br>.248<br>.248<br>.249<br>.250<br>.250<br>.250<br>.251<br>.253<br>.253<br>.253<br>.254<br>.254<br>.255<br>.256 |

|    | 15.2<br>15.3<br>15.4<br>15.5 | 15.1.1System Bus15.1.2Decoupling, $V_{REF}$ , and FilteringSystem Memory (DDR)15.2.12-DIMM DDR-SDRAMAGP15.3.11X Signals:15.3.22X/4X Signals:15.3.3Decoupling, Compensation, and $V_{REF}$ HUB Interface15.4.1Interface Signals.15.4.2Decoupling, Compensation, and $V_{REF}$ Clocks: CK_40815.5.1Decoupling, Compensation, and $V_{REF}$ Intel <sup>®</sup> ICH215.6.1IDE15.6.2AC '9715.6.3USB 1.115.6.4RTC15.6.5LAN | .241<br>.243<br>.245<br>.245<br>.248<br>.248<br>.248<br>.248<br>.248<br>.248<br>.249<br>.250<br>.250<br>.250<br>.251<br>.253<br>.253<br>.253<br>.254<br>.255<br>.256<br>.256 |

## int<sub>el</sub>.

| 15.8                | Power      |                      | 256 |

|---------------------|------------|----------------------|-----|

|                     | 15.8.1     | Filtering            | 256 |

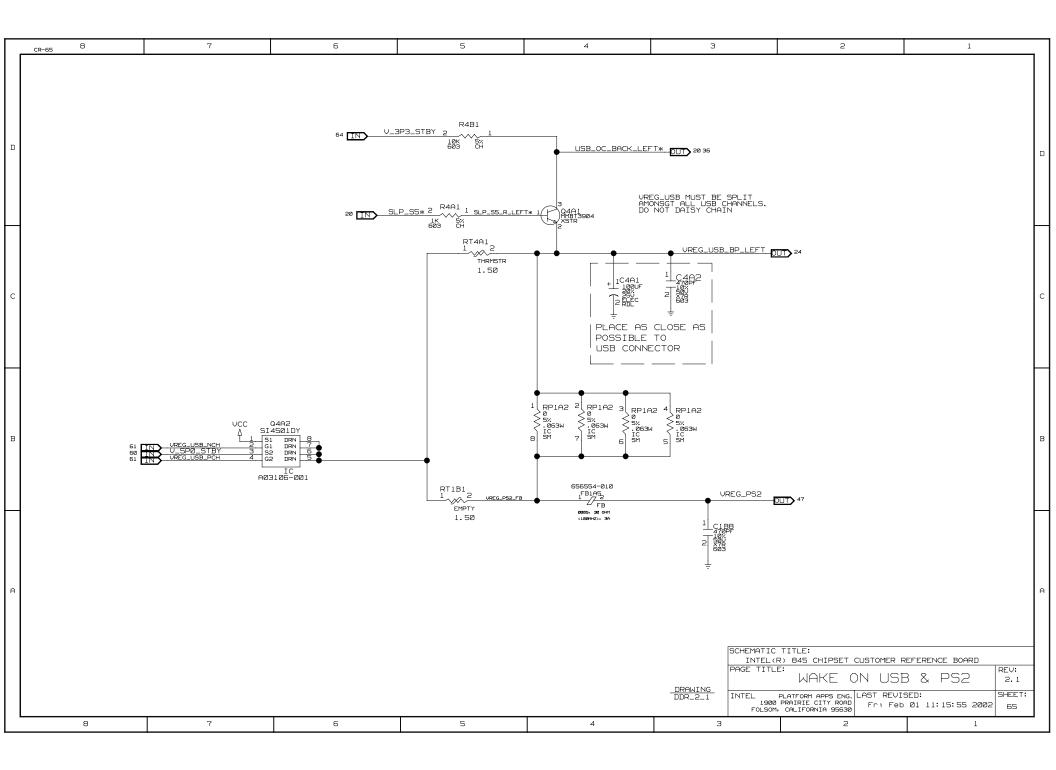

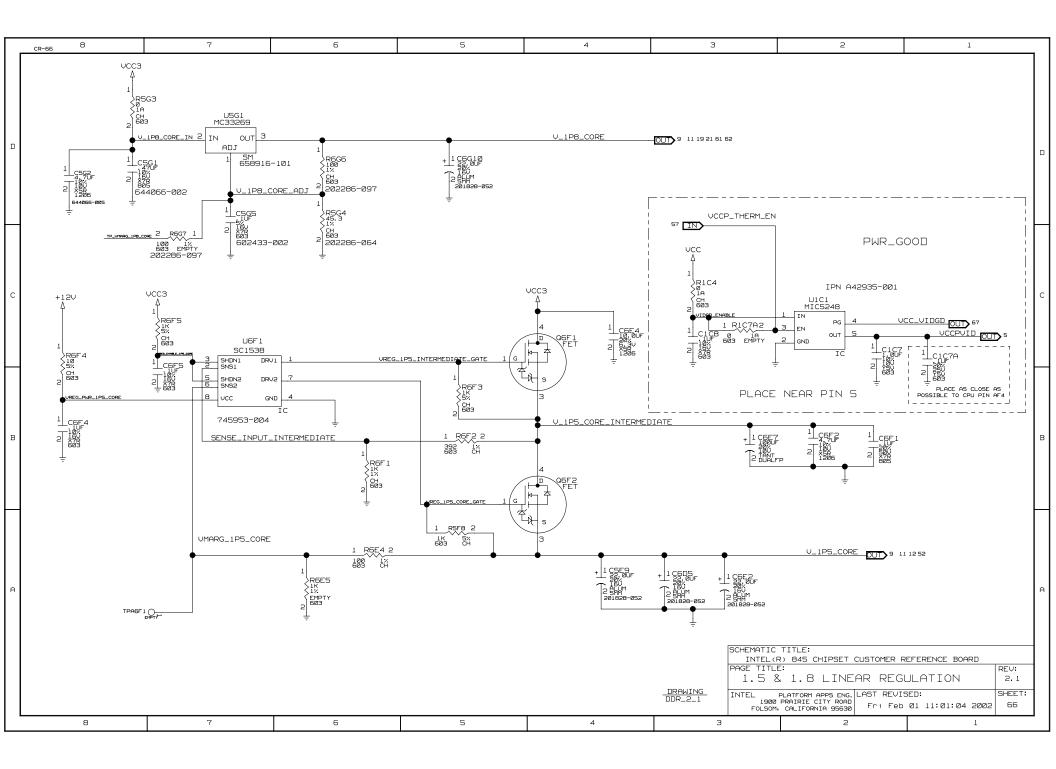

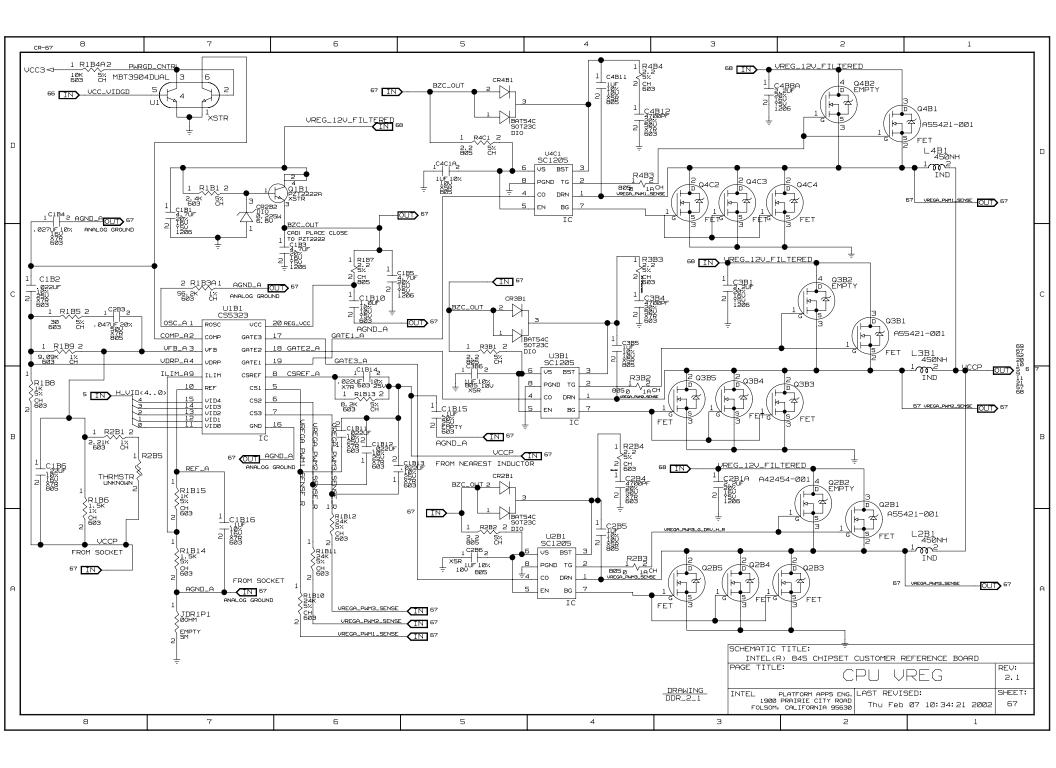

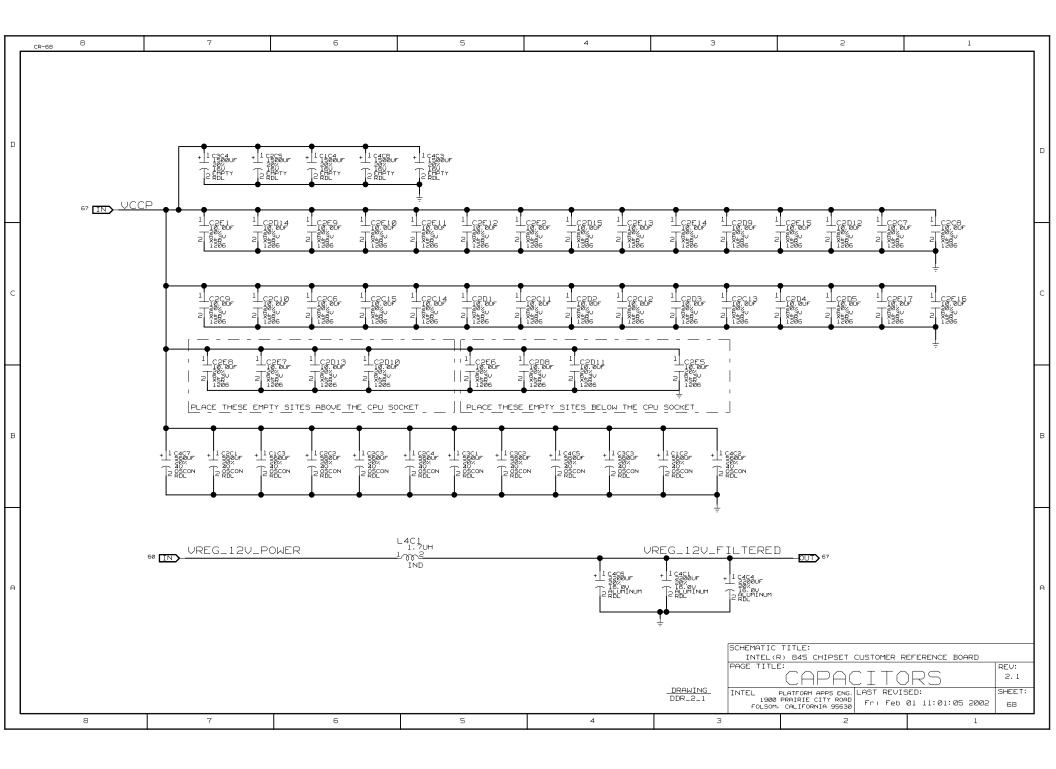

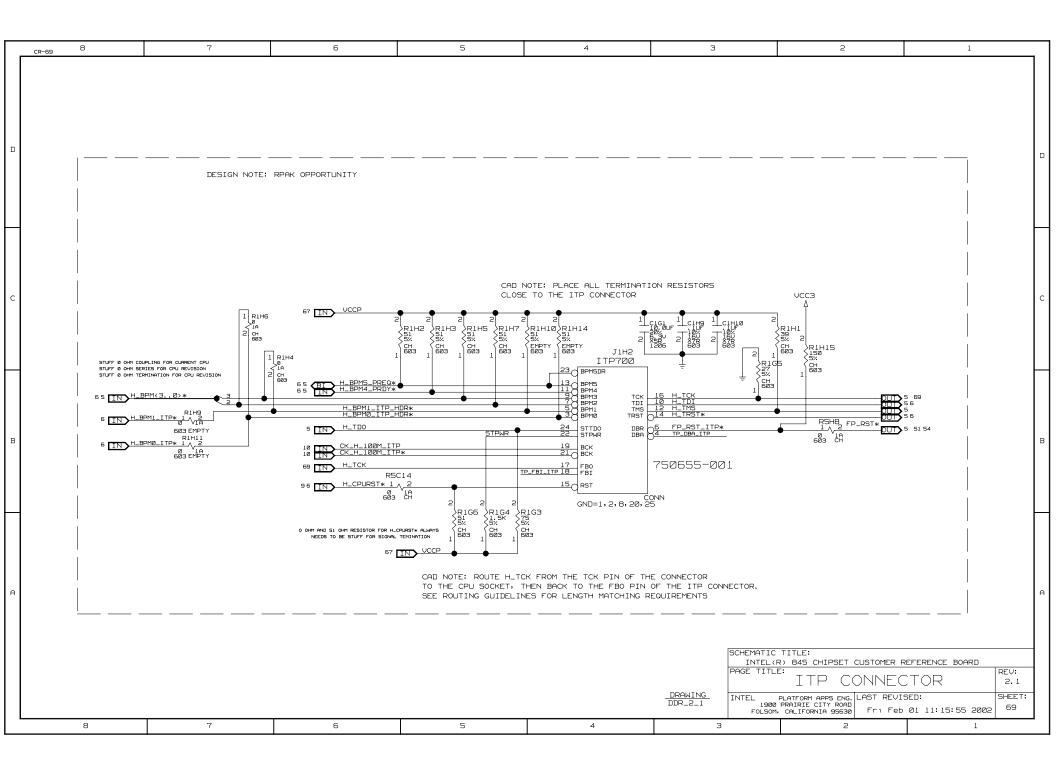

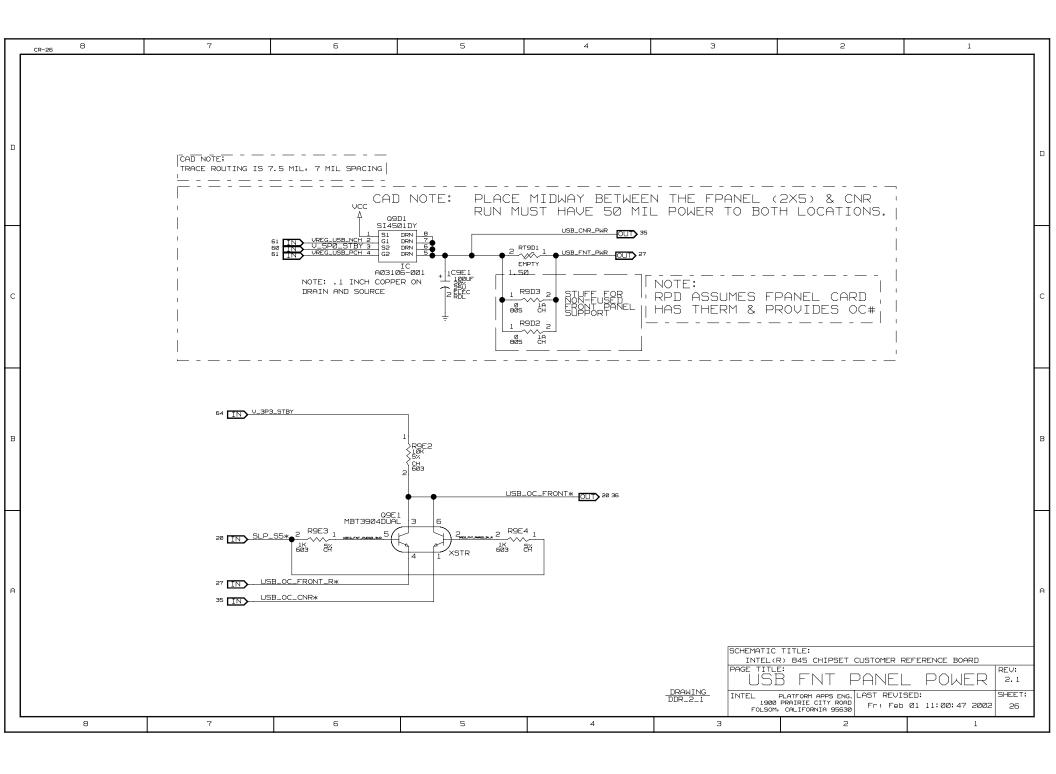

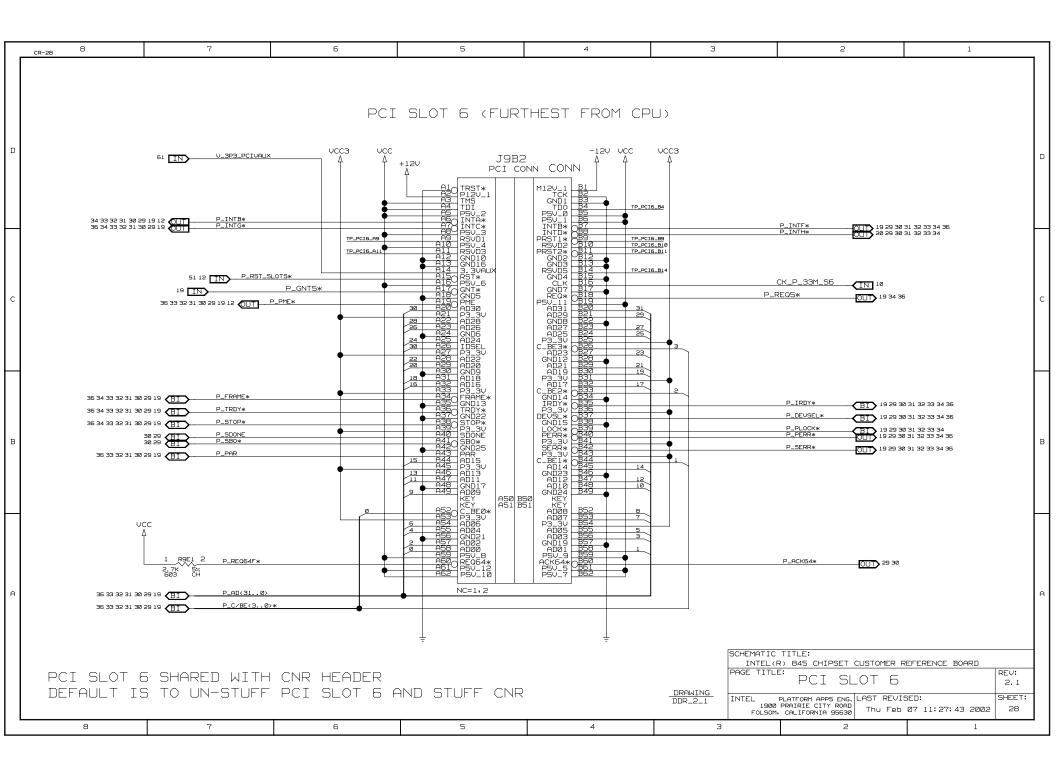

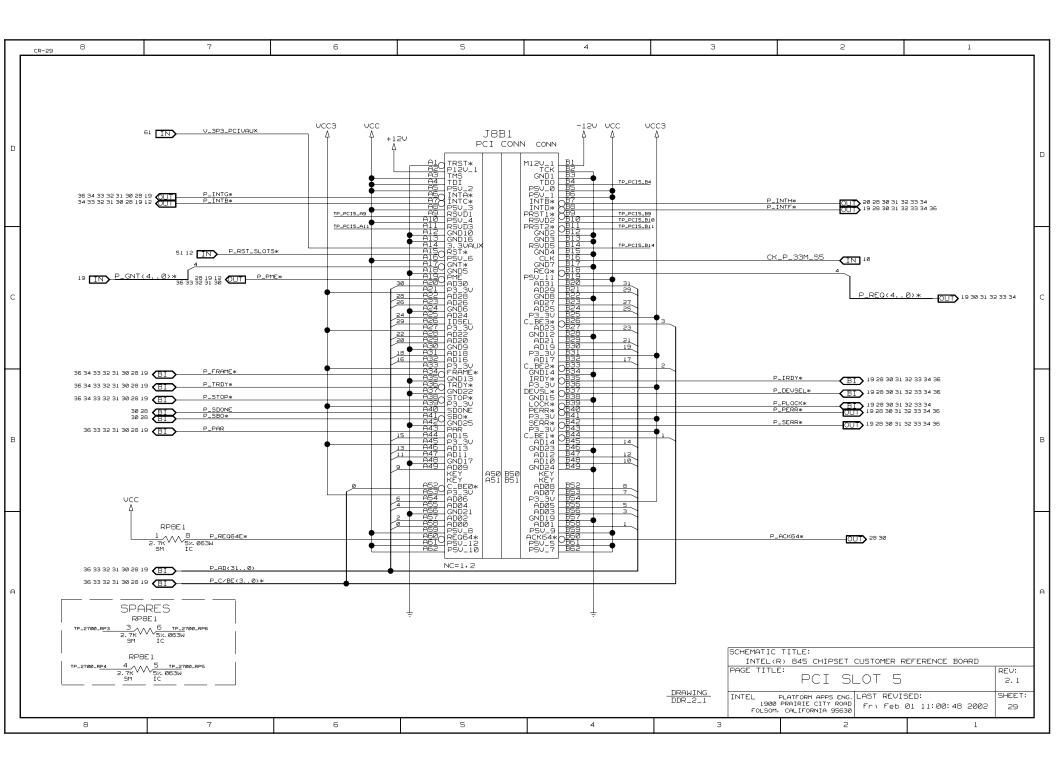

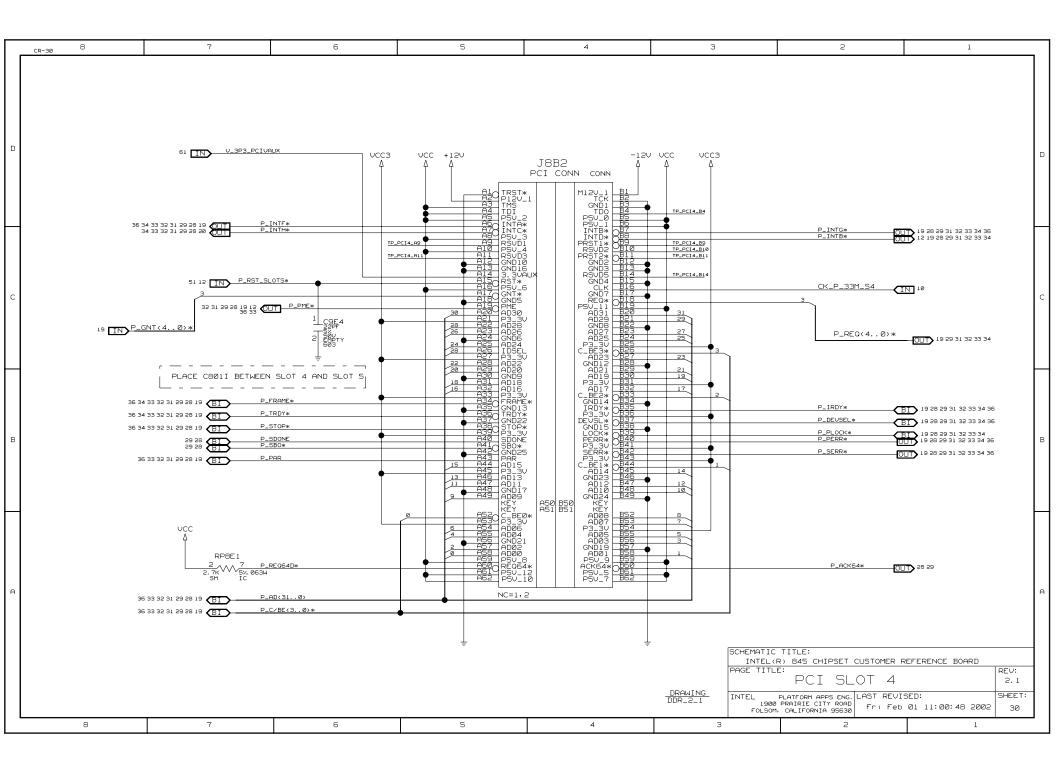

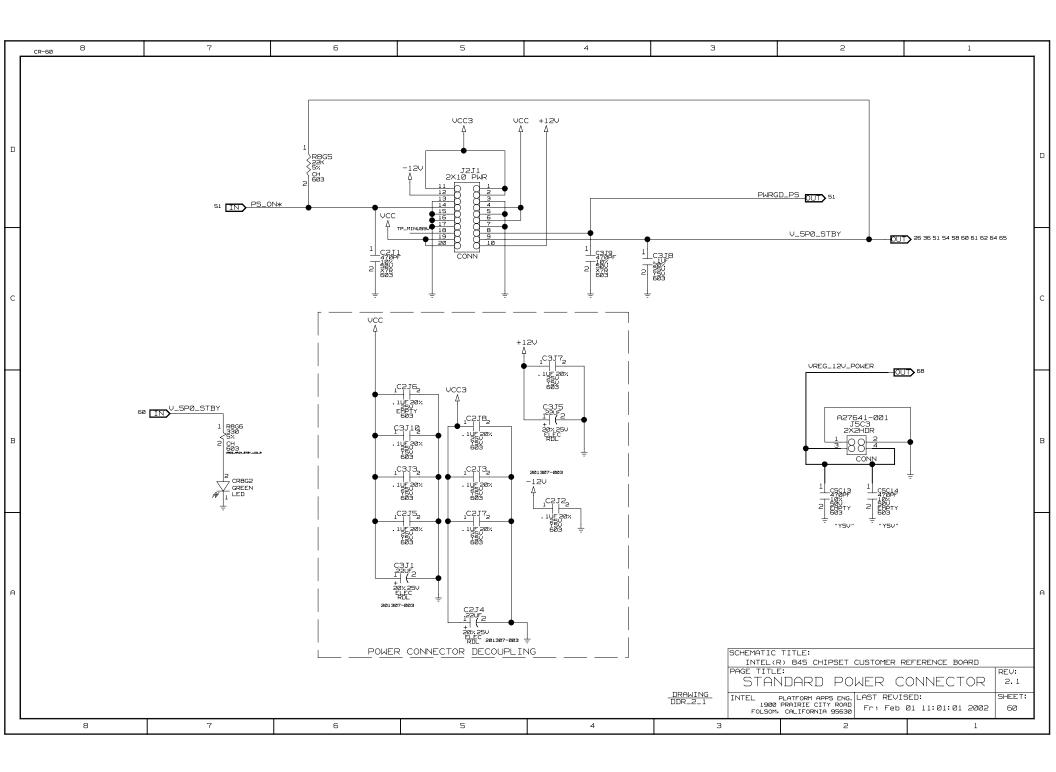

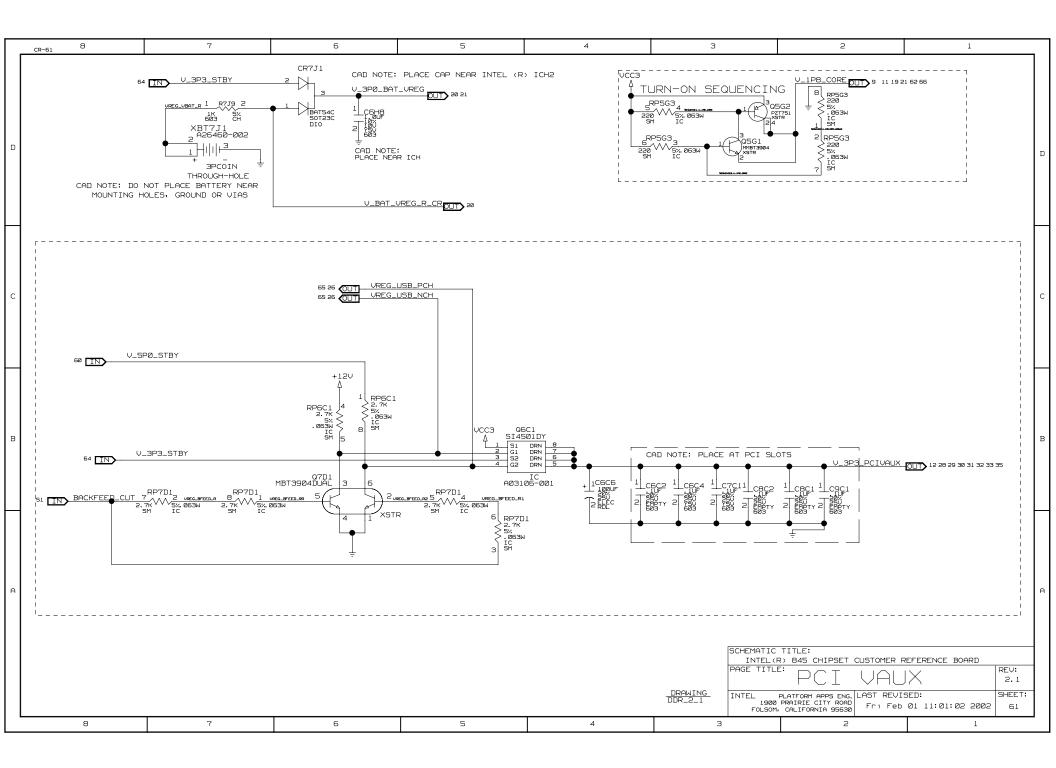

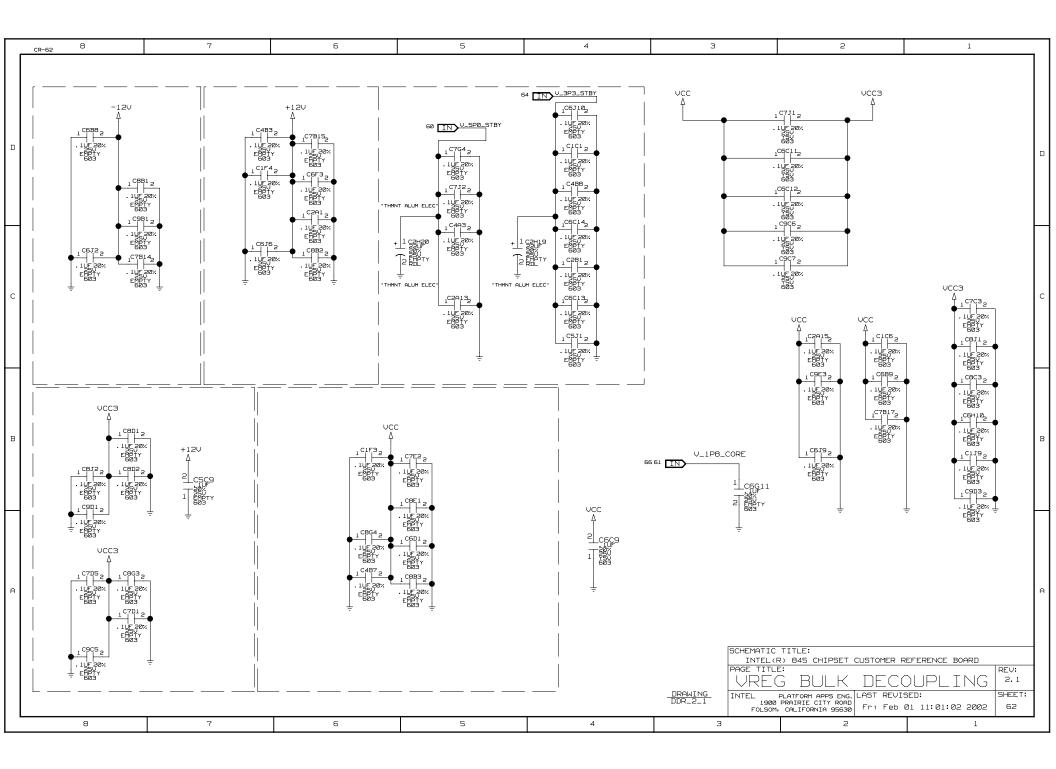

| Appendix A: Custome | er Referer | nce Board Schematics | 257 |

### **Figures**

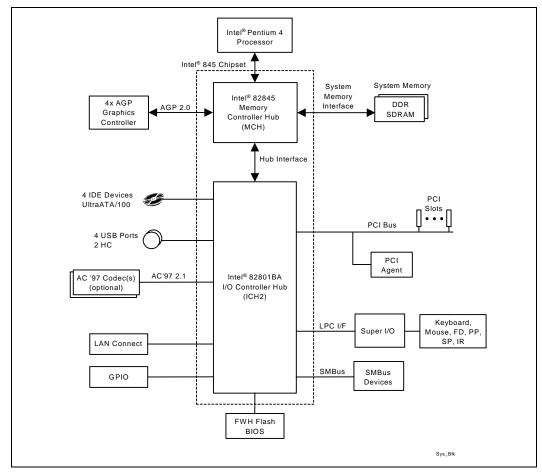

| Figure 1. Typical System Configuration                                                                                     |    |

|----------------------------------------------------------------------------------------------------------------------------|----|

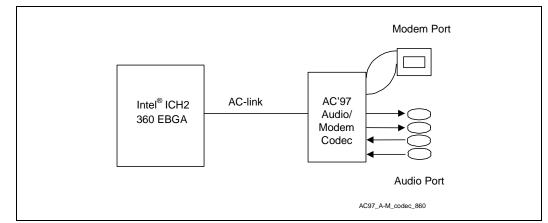

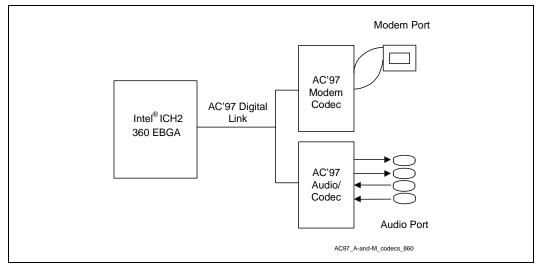

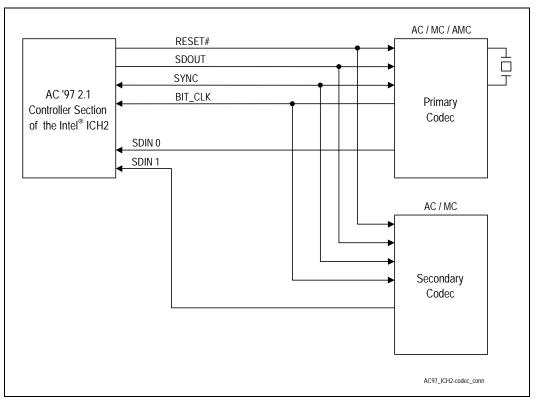

| Figure 2. AC '97 with Audio/Modem Codec                                                                                    | 27 |

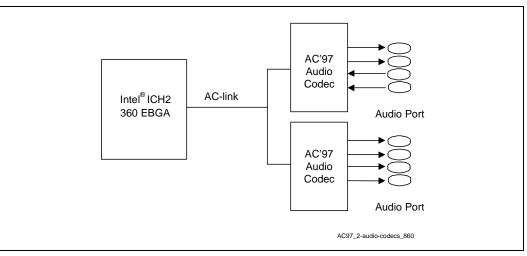

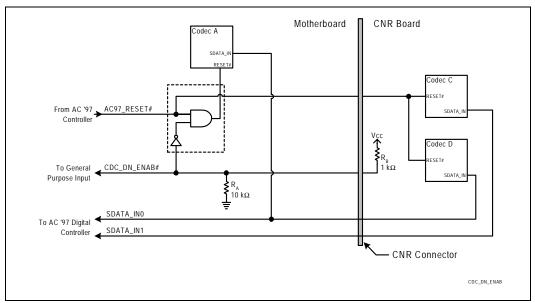

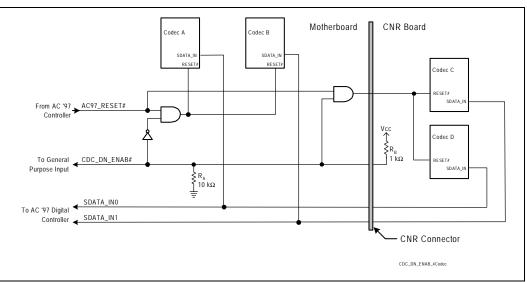

| Figure 3. AC '97 with Audio Codecs (4 Channel Secondary)                                                                   |    |

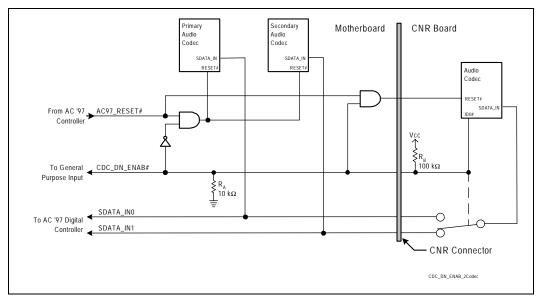

| Figure 4. AC '97 with Audio and Modem Codecs                                                                               |    |

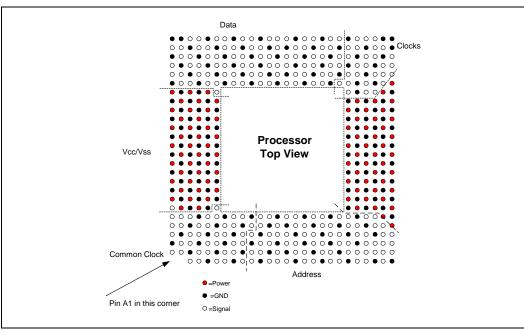

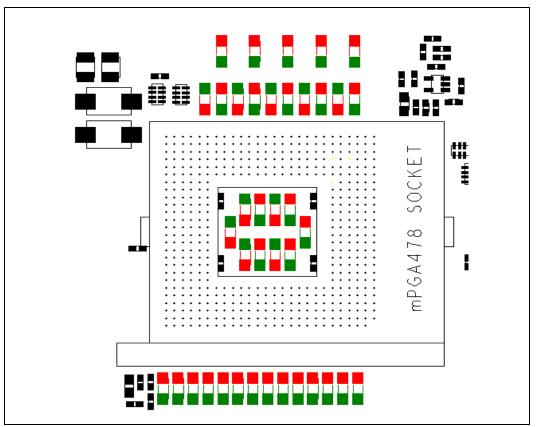

| Figure 5. Pentium <sup>®</sup> 4 Processor Component Quadrant Layout (Top View–47                                          |    |

| Package)                                                                                                                   | 29 |

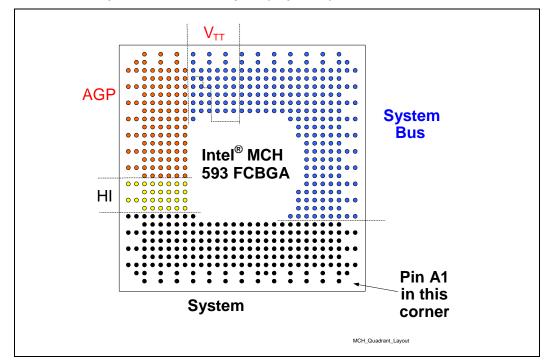

| Figure 6. Intel <sup>®</sup> MCH Component Quadrant Layout (Top View)                                                      | 30 |

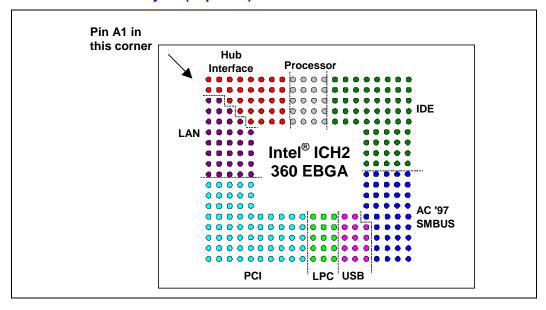

| Figure 7. Intel <sup>®</sup> ICH2 Quadrant Layout (Top View)                                                               | 30 |

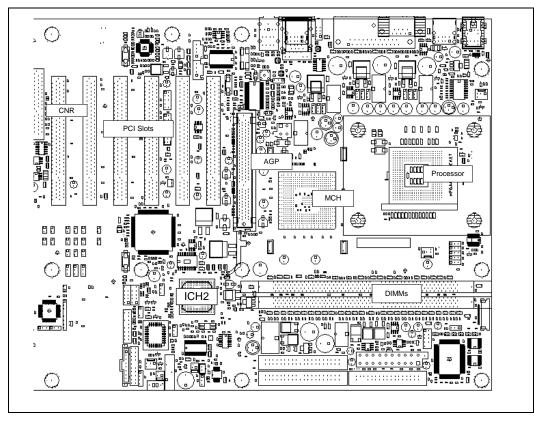

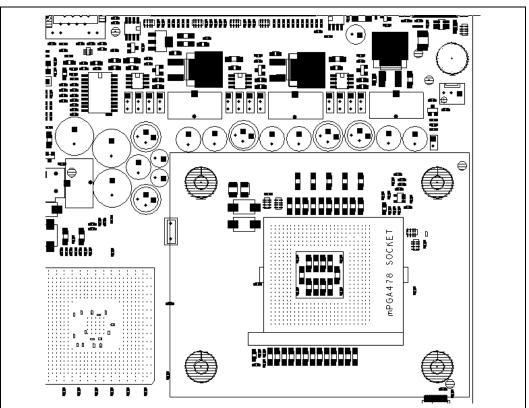

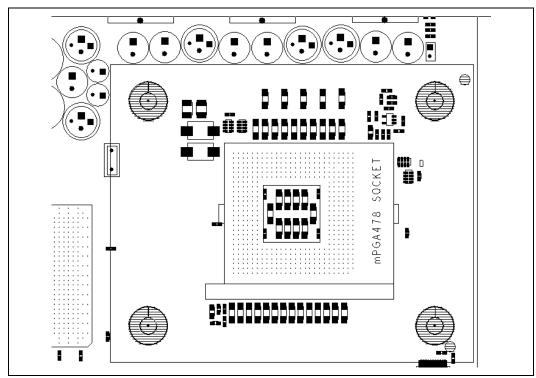

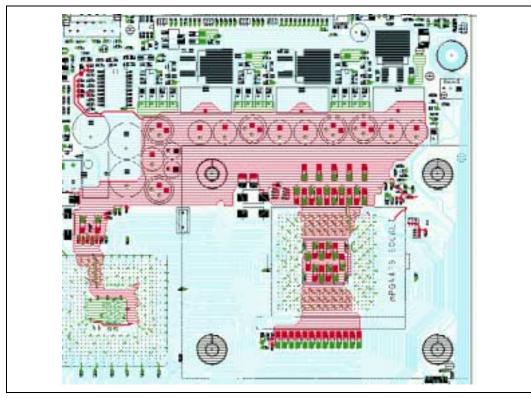

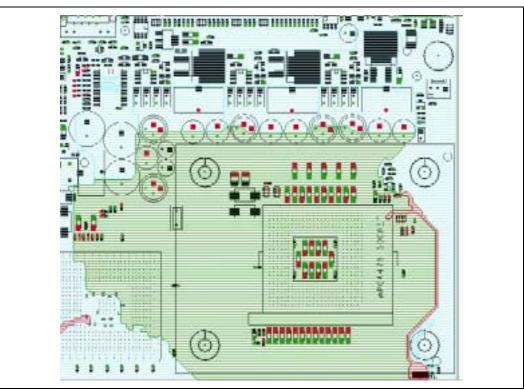

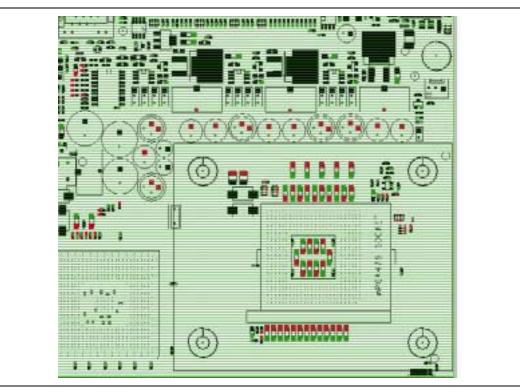

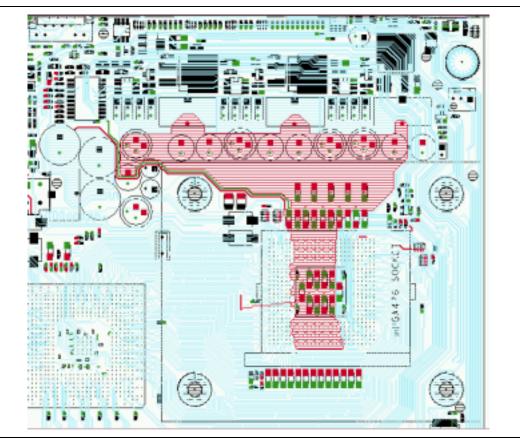

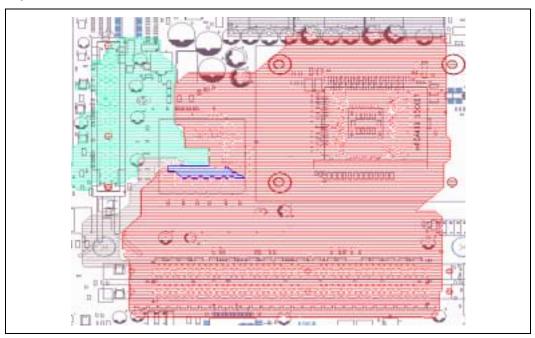

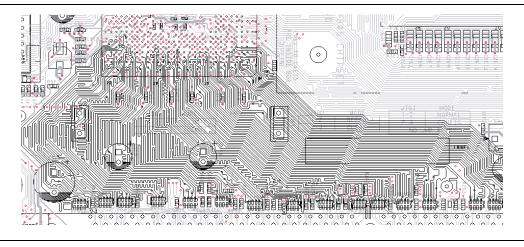

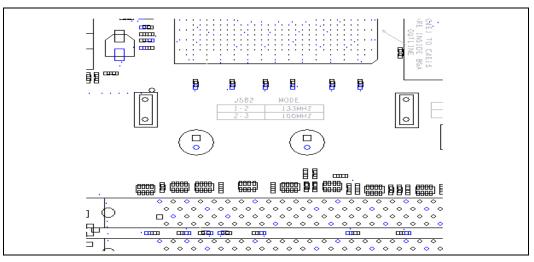

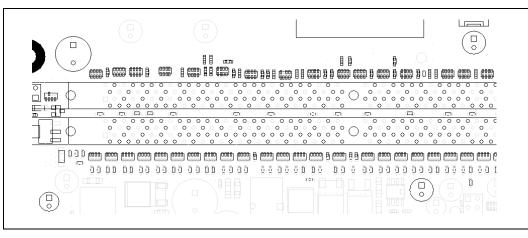

| Figure 8. Component Placement Example using DDR-SDRAM DIMMs                                                                | 31 |

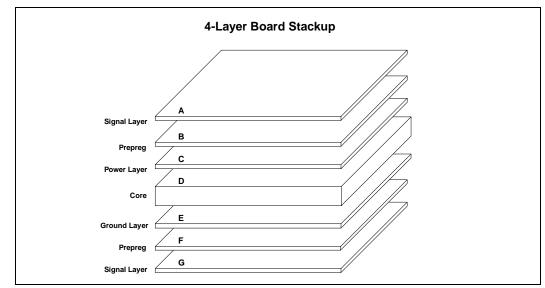

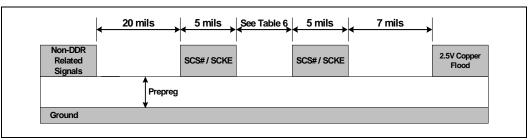

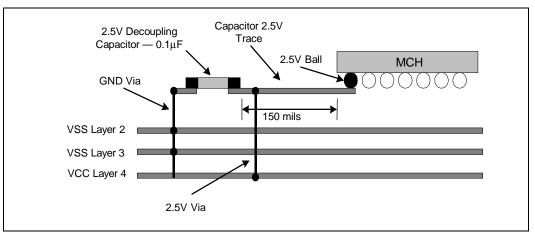

| Figure 9. 4-layer PCB Stack-Up                                                                                             | 32 |

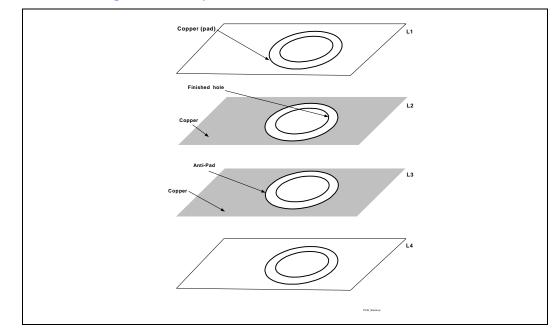

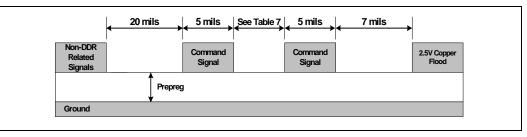

| Figure 10. PCB Technologies—Stack-Up                                                                                       | 34 |

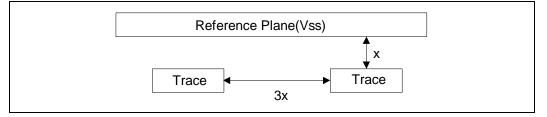

| Figure 11. Cross Sectional View of 3:1 Ratio                                                                               |    |

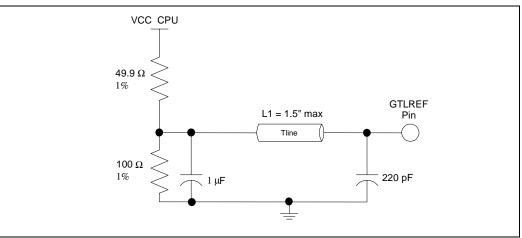

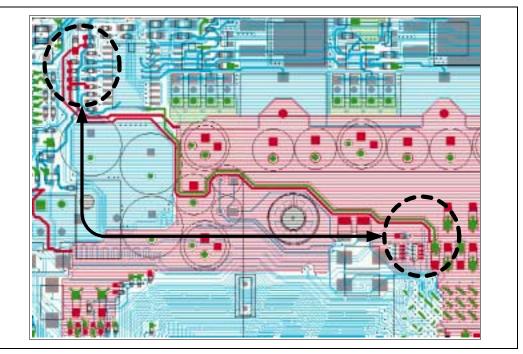

| Figure 12. GTLREF Routing                                                                                                  | 37 |

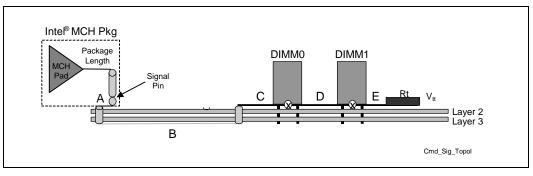

| Figure 13. Processor Topology                                                                                              | 41 |

| Figure 14. Routing Illustration for FERR#                                                                                  |    |

| Figure 15. Routing Illustration for PROCHOT#                                                                               |    |

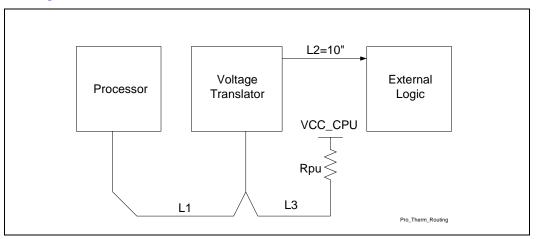

| Figure 16. Routing Illustration for THERMTRIP#                                                                             |    |

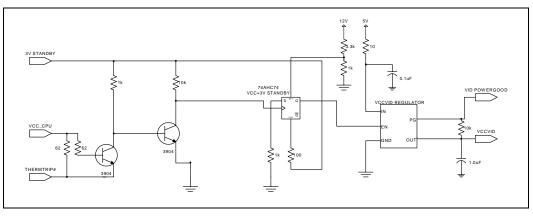

| Figure 17. THERMTRIP# Power Down Circuit                                                                                   |    |

| Figure 18. Routing Illustration for A20M#, IGNNE#, LINT[1:0], SLP#, SMI#, a                                                |    |

| STPCLK#                                                                                                                    |    |

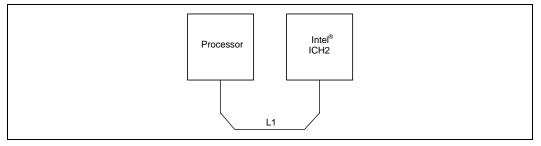

| Figure 19. Routing Illustration for INIT#                                                                                  |    |