## Smarc

## User Manual

## SM-C93

SMARC® Rel. 2.1.1 compliant module with the Intel® Atom™ x6000E Series and Intel® Pentium® and Celeron® N and J Series processors (formerly Elkhart Lake) for FuSa applications

## **REVISION HISTORY**

| Revision | Date                           | Note                   | Rif |

|----------|--------------------------------|------------------------|-----|

| 1.0      | 19 <sup>th</sup> April 2021    | First official release | AR  |

| 1.1      | 23 <sup>rd</sup> December 2021 | Safety Policy included | SO  |

|          |                                |                        |     |

#### All rights reserved. All information contained in this manual is proprietary material of SECO S.p.A.

Unauthorized use, duplication, or modification by any means without prior consent of SECO S.p.A. is prohibited.

Every effort has been made to ensure the accuracy of this manual. However, SECO S.p.A. accepts no responsibility for any inaccuracies, errors or omissions herein. SECO S.p.A. reserves the right to change precise specifications without prior notice to supply the best product possible.

For further information on this module or other SECO products, but also to get the required assistance for any and possible issues, please contact us using the dedicated web form available at http://www.seco.com (registration required).

Our team is ready to assist.

## INDEX

| Chapter | 1. INTRODUCTION             | . 4 |

|---------|-----------------------------|-----|

| 1.1     | Warranty                    | 5   |

| 1.2     | Information and assistance  | 6   |

| 1.3     | RMA number request          | 6   |

| 1.4     | Safety                      | 7   |

| 1.5     | Electrostatic Discharges    | 7   |

| 1.6     | RoHS compliance             |     |

| 1.7     | Safety Policy               | 8   |

| 1.8     | Terminology and definitions |     |

| 1.9     | Reference specifications    | 12  |

| Chapter | 2. OVERVIEW                 | 14  |

| 2.1     | Introduction                | 15  |

| 2.2     | Technical Specifications    | 16  |

| 2.3     | Electrical Specifications   | 18  |

| 2.3.    | 1 Power Consumption         | 18  |

| 2.3.    |                             |     |

| 2.4     | Mechanical Specifications   | 20  |

| 2.5     | Supported Operating Systems |     |

| 2.6     | Block Diagram               |     |

| Chapter | 3. CONNECTORS               | 22  |

| 3.1     | Introduction                | 23  |

| 3.2     | Connectors description      | 24  |

| 3.2.    |                             |     |

| Chapter | 4. Appendices               | 51  |

| 4.1     | Thermal Design              | 52  |

# Chapter 1. INTRODUCTION

- Warranty

- Information and assistance

- RMA number request

- Safety

- Electrostatic Discharges

- RoHS compliance

- Terminology and definitions

- Reference specifications

## 1.1 Warranty

This product is subject to the Italian Law Decree 24/2002, acting European Directive 1999/44/CE on matters of sale and warranties to consumers.

The warranty on this product lasts for 1 year.

Under the warranty period, the Supplier guarantees the buyer assistance and service for repairing, replacing or credit of the item, at the Supplier's own discretion.

Shipping costs that apply to non-conforming items or items that need replacement are to be paid by the customer.

Items cannot be returned unless previously authorised by the supplier.

The authorisation is released after completing the specific form available on the web-site <a href="https://www.seco.com/us/support/online-rma.html">https://www.seco.com/us/support/online-rma.html</a> (RMA Online). The RMA authorisation number must be put both on the packaging and on the documents shipped with the items, which must include all the accessories in their original packaging, with no signs of damage to, or tampering with, any returned item.

The error analysis form identifying the fault type must be completed by the customer and has must accompany the returned item.

If any of the above-mentioned requirements for RMA is not satisfied, the item will be shipped back and the customer will have to pay any and all shipping costs.

Following a technical analysis, the supplier will verify if all the requirements, for which a warranty service applies, are met. If the warranty cannot be applied, the Supplier will calculate the minimum cost of this initial analysis on the item and the repair costs. Costs for replaced components will be calculated separately.

Warning!

All changes or modifications to the equipment not explicitly approved by SECO S.p.A. could impair the equipment's functionality and could void the warranty

### 1.2 Information and assistance

What do I have to do if the product is faulty?

SECO S.p.A. offers the following services:

- SECO website: visit <a href="http://www.seco.com">http://www.seco.com</a> to receive the latest information on the product. In most of the cases it is possible to find useful information to solve the problem.

- SECO Sales Representative: the Sales Rep can help to determine the exact cause of the problem and search for the best solution.

- SECO Help-Desk: contact SECO Technical Assistance. A technician is at disposal to understand the exact origin of the problem and suggest the correct solution.

E-mail: technical.service@seco.com

Fax (+39) 0575 350210

- Repair center: it is possible to send the faulty product to the SECO Repair Centre. In this case, follow this procedure:

- o Returned items must be accompanied by a RMA Number. Items sent without the RMA number will be not accepted.

- o Returned items must be shipped in an appropriate package. SECO is not responsible for damages caused by accidental drop, improper usage, or customer neglect.

Note: Please have the following information before asking for technical assistance:

- Name and serial number of the product;

- Description of Customer's peripheral connections;

- Description of Customer's software (operating system, version, application software, etc.);

- A complete description of the problem;

- The exact words of every kind of error message encountered.

## 1.3 RMA number request

To request an RMA number, please visit SECO's web-site. On the home page, please select "RMA Online" and follow the procedure described.

An RMA Number will be sent within 1 working day (only for on-line RMA requests).

## 1.4 Safety

The SM-C93 module uses only extremely low voltages.

While handling the board, please use extreme caution to avoid any kind of risk or damages to electronic components.

Always switch the power off, and unplug the power supply unit, before handling the board and/or connecting cables or other boards.

Avoid using metallic components - like paper clips, screws and similar - near the board when connected to a power supply, to avoid short circuits due to unwanted contacts with other board components.

If the board has become wet, never connect it to any external power supply unit or battery.

Check carefully that all cables are correctly connected and that they are not damaged.

## 1.5 Electrostatic Discharges

The SM-C93 module, like any other electronic product, is an electrostatic sensitive device: high voltages caused by static electricity could damage some or all the devices and/or components on-board.

Whenever handling a SM-C93 module, ground yourself through an anti-static wrist strap. Placement of the board on an anti-static surface is also highly recommended.

## 1.6 RoHS compliance

The SM-C93 module is designed using RoHS compliant components and is manufactured on a lead-free production line. It is therefore fully RoHS compliant.

## 1.7 Safety Policy

In order to meet the safety requirements of EN62368-1:2014 standard for Audio/Video, information and communication technology equipment, the SM-C93 Module shall be:

- used inside a fire enclosure made of non-combustible material or V-1 material (the fire enclosure is not necessary if the maximum power supplied to the module never exceeds 100 W, even in worst-case fault);

- used inside an enclosure; the enclosure is not necessary if the temperature of the parts likely to be touched never exceeds 70 °C;

- installed inside an enclosure compliant with all applicable IEC 62368-1 requirements;

The manufacturer which includes a SM-C93 module in his end-user product shall:

- verify the compliance with B.2 and B.3 clauses of the EN62368-1 standard when the module works in its own final operating condition

- Prescribe temperature and humidity range for operating, transport and storage conditions;

- Prescribe to perform maintenance on the module only when it is off and has already cooled down;

- Prescribe that the connections from or to the Module have to be compliant to ES1 requirements;

- The module in its enclosure must be evaluated for temperature and airflow considerations.

## 1.8 Terminology and definitions

ACPI Advanced Configuration and Power Interface, an open industrial standard for the board's devices configuration and power management

AHCI Advanced Host Controller Interface, a standard which defines the operation modes of SATA interface

API Application Program Interface, a set of commands and functions that can be used by programmers for writing software for specific Operating

Systems

AVC Advanced Video Coding, a video compression standard, also known as H.264

BIOS Basic Input / Output System, the Firmware Interface that initializes the board before the OS starts loading

CAN Bus Controller Area network, a protocol designed for in-vehicle communication

DDC Display Data Channel, a kind of I2C interface for digital communication between displays and graphics processing units (GPU)

DDR Double Data Rate, a typology of memory devices which transfer data both on the rising and on the falling edge of the clock.

DP Display Port, a type of digital video display interface

eDP embedded Display Port, a type of digital video display interface developed especially for internal connections between boards and digital displays

GBE Gigabit Ethernet

Gbps Gigabits per second

GND Ground

GPI/O General purpose Input/Output

HEVC High Efficiency Video Coding, a video compression standard, also known as H.265

HD Audio High Definition Audio, most recent standard for hardware codecs developed by Intel® in 2004 for higher audio quality

HDMI High Definition Multimedia Interface, a digital audio and video interface

Inter-Integrated Circuit Bus, a simple serial bus consisting only of data and clock line, with multi-master capability

Inter-Integrated Circuit Sound, an audio serial bus protocol interface developed by Philips (now NXP) in 1986

JPEG/MJPEG Joint Photographic Experts Group, standard method for lossy compression of digital images. Motion JPEG is a video compression format

LAN Local Area Network

LPDDR4 Low-Power Double Data Rate Synchronous Dynamic Random Access Memory, 4th generation

LVDS Low Voltage Differential Signalling, a standard for transferring data at very high speed using inexpensive twisted pair copper cables, usually used

for video applications

Mbps Megabits per second

MIPI Mobile Industry Processor Interface alliance

MMC/eMMC MultiMedia Card / embedded MMC, a type of memory card, having the same interface as the SD card. The eMMC is the embedded version of

the MMC. They are devices that incorporate the flash memories on a single BGA chip.

MPEG2 Standard for the generic coding of moving pictures and associated audio information

MVC Multiview Video Coding, a stereoscopic video coding standard for video compression

N.A. Not ApplicableN.C. Not Connected

OpenCL Open Computing Language, specifies programming languages for programming different devices and API

OpenGL Open Graphics Library, an Open Source API dedicated to 2D and 3D graphics

Open Vector Graphics, an Open Source API dedicated to hardware accelerated 2D vector graphics

OS Operating System

PCI-e Peripheral Component Interface Express

PHY Abbreviation of Physical, it is the device implementing the Physical Layer of ISO/OSI-7 model for communication systems

PWM Pulse Width Modulation

PWR Power

RGMII Reduced Gigabit Media Independent Interface, a standard interface between the Ethernet Media Access Control (MAC) and the Physical Layer

(PHY)

SATA Serial Advance Technology Attachment, a differential full duplex serial interface for Hard Disks

SD Secure Digital, a memory card type

SDIO Secure Digital Input/Output, an evolution of the SD standard that allows the use of the same SD interface to drive different Input/Output devices,

like cameras, GPS, Tuners and so on.

SGET Standardization Group for Embedded Technologies

SMARC Smart Mobility Architecture, a computer Module standard maintained by the SGET

SM Bus System Management Bus, a subset of the I2C bus dedicated to communication with devices for system management, like a smart battery and

other power supply-related devices.

SOC System-on-a-chip

SPI Serial Peripheral Interface, a 4-Wire synchronous full-duplex serial interface which is composed of a master and one or more slaves, individually

enabled through a Chip Select line.

TBM To be measured

TMDS Transition-Minimized Differential Signalling, a method for transmitting high speed serial data, normally used on DVI and HDMI interfaces

UART Universal Asynchronous Receiver-Transmitter, is an asynchronous serial interface where data format and transmission speed are configurable

UEFI Unified Extensible Firmware Interface, a specification defining the interface between the OS and the board's firmware. It is meant to replace the

original BIOS interface

USB Universal Serial Bus

VP8 Open video compression format, a traditional block-based transform coding format

VP9 Successor to VP8, customized for video greater than 1080p

WMV9 Series 9 of Windows Media Video, a video compression format inlcuding native support for interlaced video, non-square pixels, and frame

interpolation

## 1.9 Reference specifications

Here below it is a list of applicable industry specifications and reference documents.

| Reference                                                | Link                                                                                                                       |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| ACPI                                                     | https://uefi.org/specifications                                                                                            |

| AHCI                                                     | http://www.intel.com/content/www/us/en/io/serial-ata/ahci.html                                                             |

| CAN Bus                                                  | http://www.bosch-semiconductors.de/en/ubk_semiconductors/safe/ip_modules/can_literature/can_literature.html                |

| DDC                                                      | http://www.vesa.org                                                                                                        |

| DP, eDP                                                  | http://www.vesa.org                                                                                                        |

| FastEthernet                                             | http://standards.ieee.org/about/get/802/802.3.html                                                                         |

| Gigabit Ethernet                                         | https://standards.ieee.org/standard/802_3-2018.html                                                                        |

| HD Audio                                                 | http://www.intel.com/content/dam/www/public/us/en/documents/product-specifications/high-definition-audio-specification.pdf |

| HDMI                                                     | http://www.hdmi.org/index.aspx                                                                                             |

| I2C                                                      | http://www.nxp.com/documents/other/UM10204_v5.pdf                                                                          |

| 12S                                                      | https://www.sparkfun.com/datasheets/BreakoutBoards/I2SBUS.pdf                                                              |

| Intel <sup>®</sup> Atom <sup>™</sup> Elkhart Lake family | https://ark.intel.com/content/www/us/en/ark/products/codename/80644/Elkhart-lake.html#@Embedded                            |

| LVDS                                                     | http://www.ti.com/ww/en/analog/interface/lvds.shtml and http://www.ti.com/lit/ml/snla187/snla187.pdf                       |

| MIPI                                                     | http://www.mipi.org                                                                                                        |

| MMC/eMMC                                                 | http://www.jedec.org/committees/jc-649                                                                                     |

| OpenGL                                                   | http://www.opengl.org                                                                                                      |

| OpenVG                                                   | http://www.khronos.org/openvg                                                                                              |

| PCI Express                                              | http://www.pcisig.com/specifications/pciexpress                                                                            |

| SATA                                                     | https://www.sata-io.org                                                                                                    |

| SMARC Design Guide 2.0                                   | https://sget.org/wp-content/uploads/2018/09/SMARC_DG_V2.pdf                                                                |

| SMARC Hardware Specification 2.1.1                       | https://sget.org/wp-content/uploads/2020/05/SMARC_V211.pdf                                                                 |

| SD Card Association                                      | https://www.sdcard.org/home                                                                                                |

| SDIO                | https://www.sdcard.org/developers/overview/sdio                                      |

|---------------------|--------------------------------------------------------------------------------------|

| SM Bus              | http://www.smbus.org/specs                                                           |

| TMDS                | http://www.siliconimage.com/technologies/tmds                                        |

| UEFI                | http://www.uefi.org                                                                  |

| USB 2.0 and USB OTG | http://www.usb.org/developers/docs/usb_20_070113.zip                                 |

| USB 3.0             | https://usb.org.10-1-108-210.causewaynow.com/sites/default/files/usb_32_20191024.zip |

## Chapter 2. OVERVIEW

- Introduction

- Technical Specifications

- Electrical Specifications

- Mechanical Specifications

- Supported Operating Systems

- Block Diagram

### 2.1 Introduction

The SM-C93 is a SMARC Rel. 2.1.1 compliant module based on the Intel® Atom® x6000E Series and Intel® Pentium® and Celeron® N and J Series processors (formerly Elkhart Lake) for FuSa applications, a series of Dual / Quad SOCs with 64-bit instruction set.

These new family of processors offers different use conditions, such as PC Client, Embedded and Industrial targets and is optimized for usage in vertical applications for IOT including Industrial, Office Automation, Retail, Gaming, Healthcare, Transportation.

New features introduced by Elkhart Lake are, but not limited to the following: Time Sensitive Network (TSN) and Time Coordinate Computing (TCC) for real-time and responsive applications, Scalability and consolidation of temporally deterministic workloads, In band and OOB remote manageability (reboot/power-on/power-off), Platform Trust Technology (PTT), Dynamic Application Loader (DAL) and Secure Guard Extension (SGX), Intel Programmable Service Engine, Intel UHD Graphics, media, and display supporting, Fully Integrated Voltage Regulator (FIVR). Last but not least, this is the first Intel product designed with functional safety capabilities, made available by Intel® Safety Island (SI), a functional safety IP integrated into the Elkhart Lake Platform Control Hub (PCH), intended to raise the safety level of the platform with a single source for managing the safety faults of the SOC.

These SOCs embed all the features usually obtained by combination of CPU + platform Controller hubs, all in one single IC, which allows, therefore, the system minimisation and performance optimisation, which is essential for boards with sizes so reduced as for SMARC ("Smart Mobility ARChitecture") form factor, offering the computing abilities of a standard board, with the possibilities of combining with a ready-to-use carrier board like the SECO CSM-B79 or customised carrier board.

The Embedded Memory Controller allows the integration of up to 16GB of LPDDR4 Memory directly soldered onboard with In-Band Error Correction Code supported (Safety related feature) and speed up to 4267MT/s on single rank and 3733MT/s on dual rank.

All SOCs embed an Intel® Gen11 UHD Graphics controller with up to 32 Execution Units, which offer high graphical performances, with support for Microsoft® DirectX12.1, OpenGL 4.5, OpenGL™ 1.2, OpenGL ES 3.1, Vulkan 1.1 and HW acceleration for video encoding and decoding of HEVC (H.265), H.264, VP8, VP9, JPEG/MJPEG. It is also possible the HW video decoding only of MPEG2, VC-1.

This embedded GPU is able to drive three independent displays, by using the interfaces available on SMARC connector: one DP++ 1.4, one HMDI 1.4 or DP++ 1.4 and one eDP 1.3 or Dual Channel 18/24bit LVDS (factory alternatives).

Mass Storage capabilities of the board include one external S-ATA Gen3 channel, a standard 4-bit SD interface and one optional eMMC 5.1 Drive soldered on board (Safety related), with up to 128GB capabilities.

Other than the interfaces already discussed previously, on SMARC connector there are the signals necessary for the implementation of 2x GbE, up to 6 ports in USB2.0 only and up to 2 Super Speed (SS) ports (i.e. USB 3.1 Gen2 compliant), 4 x PCI-Express Gen3 lanes, HD and I<sup>2</sup>S Audio interfaces, CAN, I<sup>2</sup>C, SPI and SM buses, up to 14 GPIOs, HS-UART and UART interfaces.

Interfacing to the board comes through a single card edge connector, whose pinout is defined by SMARC specifications Rel.2.1.1. For external interfacing to standard devices, a carrier board with a 230-pin MXM connector is needed. This board will implement all the routing of the interface signals to external standard connectors, as well as integration of other peripherals/devices not already included in SM-C93 CPU module.

Please refer to following chapter for a complete list of all peripherals integrated and characteristics.

## 2.2 Technical Specifications

#### **Processors**

Intel® Atom™ x6000E CPUs certified for FuSa, compliant to IEC 61508 and ISO 13849 requirements for Functional Safety and Safety Integrity Levels:

- Atom™ x6427FE Quad Core @1.9GHz (no Turbo) 12W TDP w/ IBECC, IHS and TCC, FuSa Certified - Ind. Temp. Range

- Atom™ x6200FE Dual Core @1.0GHz (no Turbo) 4.5W TDP no Graphics w/ IBECC, IHS and TCC, FuSa Certified- Ind. Temp. Range

Other Intel Atom™ x6000E, Pentium® and Celeron® N and J Series CPUs:

- Celeron® J6413 Quad Core @ 1.8GHz (3.0GHZ Turbo) 10W TDP Comm. Temp. Range

- Celeron® N6211 Dual Core @1.2GHz (3.0GHZ Turbo) 6.5W TDP Comm. Temp. Range

- Pentium® J6426 Quad Core @2.0GHz (3.0GHZ Turbo) 10W TDP Comm. Temp.

Range

- Pentium® N6415 Quad Core @1.2GHz (3.0GHZ Turbo) 6.5W TDP Comm. Temp. Range

- Atom™ x6211E Dual Core @1.3GHz (3.0GHZ Turbo) 6W TDP w/ IBECC and IHS -Ind. Temp. Range

- Atom™ x6413E Quad Core @1.5GHz (3.0GHZ Turbo) 9W TDP w/ IBECC and IHS -Ind. Temp. Range

- Atom<sup>™</sup> x6425E Quad Core @2.0GHz (3.0GHZ Turbo) 12W TDP w/ IBECC and IHS

Ind. Temp. Range

- Atom™ x6212RE Dual Core @1.2GHz (no Turbo) 6W TDP w/ IBECC, IHS and TCC

Ind. Temp. Range

- Atom™ x6414RE Quad Core @1.5GHz (no Turbo) 9W TDP w/ IBECC, IHS and TCC Ind. Temp. Range

- Atom™ x6425RE Quad Core @1.9GHz (no Turbo) 12W TDP w/ IBECC, IHS and TCC - Ind. Temp. Range

(\*) IHS: Integrated Heatspreader; TCC: Time Coordinated Computing

#### Memory

32-bit LPDDR4x Soldered Down Memory

Up to 16GB Quad Channel with In-Band Error Correction Code (IBECC, Safety Related feature) supported

4GB Dual Channel, 8GB or 16GB Quad Channel

Speed:4267MT/s single rank (1GB/2GB/4GB/8GB), 3733MT/s dual rank (16GB)

#### Graphics

Up to 3 independent displays

Integrated Gen11 UHD Graphics controller with up to 32 EU

4K HW decoding and encoding of HEVC (H.265), H.264, VP8/ VP9, WMV9/VC1 (decoding only)

DirectX 12.1, OpenGL ES 3.1, OpenGL 4.5, OpenCL™ 1.2, Vulkan 1.0

#### Video Interfaces

eDP 1.3 or Dual Channel 18/24bit LVDS interface (factory options) 2 x DP++ 1.4 or 1x DP++ 1.4 and 1x HDMI 1.4 interfaces

#### Video Resolution

Up to 4096 x 2160 @60Hz

#### Mass Storage

1 x external S-ATA Gen3 Channel

SDIO interface

Optional eMMC 5.1 drive soldered on-board (Safety Related)

#### PCI Express

Up to 4 x PCI-e Gen3 Lanes

#### Networking

2x Gigabit Ethernet PHY with precision clock synchronization and synchronous Ethernet clock output for IEEE 1588 (Safety Related – Black channel). Optional SERDES (SGMII) Interface for additional third Gigabit Ethernet (factory option, alternative to fourth PCI-e lane)

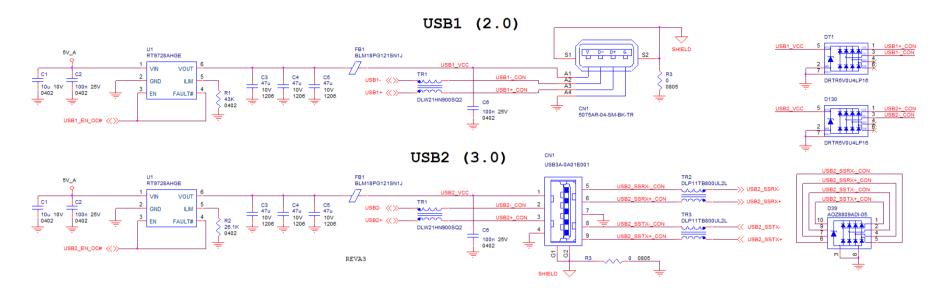

#### **USB**

6 x USB 2.0 Host Ports 2 x USB 3.1 Gen2 Ports

#### Audio

**HD** Audio interface

#### Serial ports

2 x HS-UARTs (Safety Related) 2 x UARTs

#### **CAN Bus**

2 x CAN interfaces

#### Other Interfaces

Up to 14x GPIOs SM Bus Power Management Signals I2C Bus 1x SPI interface for boot 1x General Purpose SPI or eSPI (Factory Alternatives)

#### **Functional Safety Features**

FuSa Interface signals for IEC 61508 and ISO 13849

Power supply voltage: +5V<sub>DC</sub> and +3.3V\_RTC

#### **Operating System**

Microsoft® Windows 10 Enterprise (64 bit) Linux Yocto 64-bit Operating temperature:

Commercial version  $0^{\circ}\text{C} \div +60^{\circ}\text{C}^{**}$ . Industrial version  $-40^{\circ}\text{C} \div +85^{\circ}\text{C}^{**}$ .

Dimensions: 50 x82 mm (1.97" x 3.23")

\*\* Measured at any point of SECO standard heatspreader for this product, during any and all times (including start-up). Actual temperature will widely depend on application, enclosure and/or environment. Upon customer to consider application-specific cooling solutions for the final system to keep the heatspreader temperature in the range indicated. Please also check paragraph 4.1

## 2.3 Electrical Specifications

According to SMARC specifications, the SM-C93 module needs to be supplied only with an external +5V<sub>DC</sub> power supply.

For Real Time Clock working and CMOS memory data retention, it is also needed a backup battery voltage. All these voltages are supplied directly through card edge fingers (see connector's pinout). All remaining voltages needed for board's working are generated internally from +5V<sub>DC</sub> power rail.

#### 2.3.1 Power Consumption

SM-C93 module, like all SMARC modules, needs a carrier board for its normal working. All connections with the external world come through this carrier board, which provide also the required voltage to the board, deriving it from its power supply source. Anyway, it has been possible to measure power consumption directly on VDD\_IN power rail (5V<sub>DC</sub>) that supplies the board. Power consumption must be intended as average value (30 seconds acquisition).

|                                                          |        |                                             |                          |       |        |                                            |                                                                       | Config | uration |                                            |                                                                    |       |        |                                                                                             |                                       |       |

|----------------------------------------------------------|--------|---------------------------------------------|--------------------------|-------|--------|--------------------------------------------|-----------------------------------------------------------------------|--------|---------|--------------------------------------------|--------------------------------------------------------------------|-------|--------|---------------------------------------------------------------------------------------------|---------------------------------------|-------|

| Status                                                   |        | 16GB L<br>128GB<br>4 x F<br>LVDS and<br>TPN | eMMC<br>PCI-e<br>2x DP++ |       |        | 8GB L<br>128GB<br>4 x F<br>LVDS and<br>TPM | um® J6425<br>PDDR4<br>eMMC<br>PCI-e<br>I 2x DP++<br>I 2.0<br>mp Range |        | lr      | 16GB L<br>128GB<br>4 x F<br>eDP and<br>TPM | M x6425RE<br>PDDR4<br>eMMC<br>PCI-e<br>2x DP++<br>1 2.0<br>p Range |       |        | ntel <b>Atom</b> <sup>TI</sup><br>8GB LF<br>64GB 4 x F<br>LVDS and<br>TPM<br>Fu:<br>Ind Tem | eMMC<br>PCI-e<br>2x DP++<br>2.0<br>Sa |       |

|                                                          | Avg V  | alue                                        | Peak \                   | /alue | Avg V  | alue                                       | Peak \                                                                | /alue  | Avg V   | 'alue                                      | Peak V                                                             | /alue | Avg V  | alue                                                                                        | Peak V                                | 'alue |

| Idle – (Win10) –<br>power saving<br>configuration        | 3.5W   | 0.7A                                        | 6.22W                    | 1.24A | 2.46W  | 0.49A                                      | 6.79W                                                                 | 1.35A  | 6W      | 1.2A                                       | 6.3W                                                               | 1.26A | 6.97W  | 1.39A                                                                                       | 9.71W                                 | 1.94A |

| OS Boot – (Win10)                                        | 5.68W  | 1.13A                                       | 12.63W                   | 2.52A | 6.28W  | 1.25A                                      | 9.41W                                                                 | 1.88A  | 7.85W   | 1.57A                                      | 13.6W                                                              | 2.72A | 6.83W  | 1.36A                                                                                       | 12.61W                                | 2.52A |

| Video reproduction<br>@1080p                             | 4.34W  | 0.54A                                       | 9.96W                    | 2A    | 4.27W  | 0.85A                                      | 11W                                                                   | 2.2A   | 6.53W   | 1.31A                                      | 9.12W                                                              | 1.82A | 7.38W  | 1.47A                                                                                       | 9.49W                                 | 1.9A  |

| Video reproduction 4K                                    | 6.71W  | 1.34A                                       | 10.64W                   | 2.12A | 6W     | 1.2A                                       | 11.83W                                                                | 2.36A  | 7.76W   | 1.55A                                      | 10.47W                                                             | 2.09A | 7.76W  | 1.55A                                                                                       | 10.47A                                | 2.09A |

| Intel PTU (package power limit and TURBO Enabled)        | 16.12W | 3.22A                                       | 19.96W                   | 3.98A | 11.22W | 2.24A                                      | 16.29W                                                                | 3.25A  | 13.68W  | 2.73A                                      | 14.52W                                                             | 2.9A  | 13.39W | 2.68A                                                                                       | 14.03W                                | 2.8A  |

| Intel PTU (without<br>power limits and<br>TURBO Enabled) | 22.91W | 4.58A                                       | 24.2W                    | 4.83A | 17.36W | 3.47A                                      | 18.92W                                                                | 3.98A  | 14.46W  | 2.89A                                      | 15.74W                                                             | 3.15A | 14.39W | 2.87A                                                                                       | 15.6W                                 | 3.12A |

Independently by the SOC mounted onboard, the following power consumptions are common to all boards:

Battery Backup power consumption: 3.11µA Soft-Off State power consumption: 174mA Suspend State power consumption: 176mA

#### 2.3.2 Power Rails meanings

In all the tables contained in this manual, Power rails are named with the following meaning:

VDD\_IN: Module power input voltage. +5V voltage directly coming from the card edge connector, internally named as 5V\_DSW.

VDD\_RTC: Low current RTC circuit backup power. 3V coin cell voltage coming from the edge card for supplying the RTC clock on the Elkhart Lake SOCs.

- +3.3V\_DSW: +3.3 Deep Sleep Well, derived internally from 5V\_DSW

- +3.3V\_RUN: +3.3 Switched voltage, derived internally from +3.3V\_DSW

- +3.3V\_ALW: +3.3 Always-on voltage, derived internally from +3.3V\_DSW

- +1.8V\_ALW: +1.8 Always-on voltage, derived internally from 5V\_DSW

- +1.8V\_RUN: +1.8 Switched voltage, derived internally from +1.8V\_ALW

- +1.8V\_DSW: +1.8 Deep sleep well, derived internally from +3.3V\_DSW

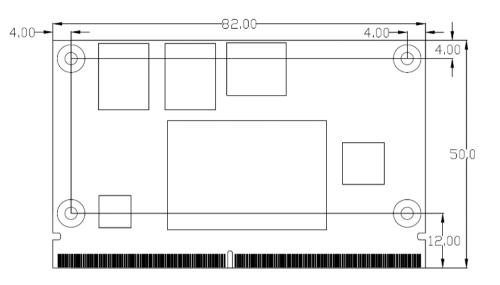

## 2.4 Mechanical Specifications

According to SMARC $^{\circ}$  specifications, the board dimensions are: 50 x 82 mm (1.97" x 3.23") including the pin numbering and edge finger pattern.

Printed circuit of the board is made of twelve layers, some of them are ground planes, for disturbance rejection.

The MXM connector accommodates various connector heights for different carrier board applications needs.

When using different connector heights, please consider that, according to SMARC specifications, components placed on bottom side of SM-C93 will have a maximum height of 1.3mm. Keep this value in mind when choosing the MXM connector's height, if there is the need to place components on the carrier board in the zone below the SMARC module.

## 2.5 Supported Operating Systems

SM-C93 module supports the following operating systems:

- Microsoft® Windows 10 Enterprise (64 bit)

- Linux Yocto 64-bit

SECO will offer the BSP (Board Support Package) for these O.Ss, to reduce at minimum SW development of the board, supplying all the drivers and libraries needed for use both with the SMARC board and the Carrier Board, assuming that the Carrier Board is designed following SECO SMARC Design Guide, with the same IC's.

For further details, please visit <a href="https://www.seco.com">https://www.seco.com</a>.

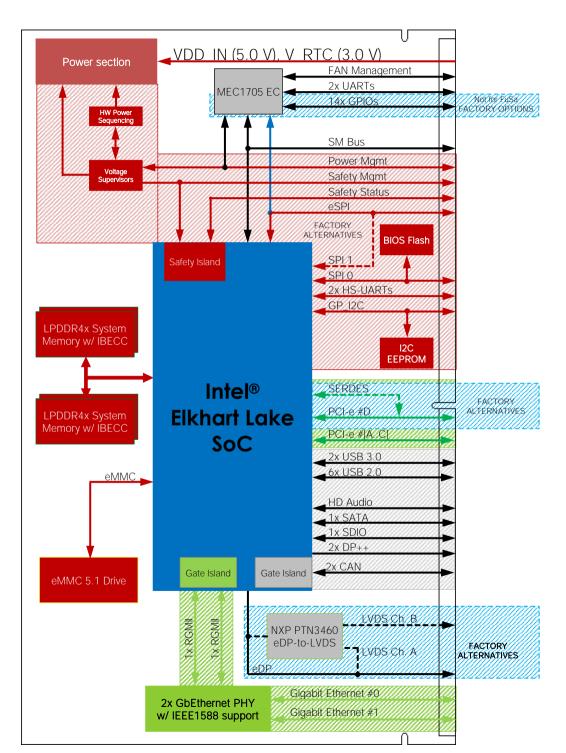

## 2.6 Block Diagram

Safety Related features

Safety Related Black-Channel features

Not Safety Related features

# Chapter 3. CONNECTORS

- Introduction

- Connectors description

## 3.1 Introduction

According to SMARC specifications, all interfaces to the board are available through a single card edge connector.

Card Edge golden finger, pin P156

Card Edge golden finger, pin P156

## 3.2 Connectors description

#### 3.2.1 SMARC Connector

According to SMARC Rel 2.1 specification, all interface signals are reported on the card edge connector, which is a 314-pin Card Edge that can be inserted into standard low profile 314 pin 0.5mm right pitch angle connector that was originally defined for use with MXM3 graphics cards.

Not all signals contemplated in the SMARC Rel 2.1 are implemented on card edge connector, therefore, please refer to the following table for a list of effective signals reported on the card edge connector.

For accurate signals description, please consult the following paragraphs.

| SMARC Golden Finger Connector – CN1 |      |            |         |         |               |           |              |  |  |

|-------------------------------------|------|------------|---------|---------|---------------|-----------|--------------|--|--|

| TOP SIDE                            |      |            |         |         | ВО            | TTOM SIDE |              |  |  |

| SIGNAL GROUP                        | Type | Pin name   | Pin nr. | Pin nr. | Pin name      | Type      | SIGNAL GROUP |  |  |

|                                     |      |            |         | S1      | PROCHOT       | I/O       | FUSA         |  |  |

| MANAGEMENT                          | I    | SMB_ALERT# | P1      | S2      | FUSA_PWRFAIL# | I/O       | FUSA         |  |  |

|                                     |      | GND        | P2      | S3      | GND           |           |              |  |  |

|                                     |      | N.C.       | Р3      | S4      | CHXPMICEN     | T         | FUSA         |  |  |

|                                     |      | N.C        | P4      | S5      | N.C.          |           |              |  |  |

| GBE                                 | I/O  | GBE1_SDP   | P5      | S6      | N.C.          |           |              |  |  |

| GBE                                 | I/O  | GBE0_SDP   | P6      | S7      | N.C.          |           |              |  |  |

|                                     |      | N.C.       | P7      | S8      | N.C.          |           |              |  |  |

|                                     |      | N.C        | P8      | S9      | N.C.          |           |              |  |  |

|                                     |      | GND        | P9      | S10     | GND           |           |              |  |  |

|                                     |      | N.C.       | P10     | S11     | N.C.          |           |              |  |  |

|                                     |      | N.C        | P11     | S12     | N.C.          |           |              |  |  |

|                                     |      | GND        | P12     | S13     | GND           |           |              |  |  |

|                                     |      | N.C.       | P13     | S14     | N.C.          |           |              |  |  |

|                                     |      | N.C        | P14     | S15     | N.C.          |           |              |  |  |

|                                     |      | GND        | P15     | S16     | GND           |           |              |  |  |

|                                     |      | N.C.       | P16     | S17     | GBE1_MDI0+    | I/O       | GBE          |  |  |

|                 |     | N.C            | P17 | S18 | GBE1_MDI0-                   | 1/0 | GBE            |

|-----------------|-----|----------------|-----|-----|------------------------------|-----|----------------|

|                 |     | GND            | P18 | S19 | GBE1_LINK100#                | Ο   |                |

| GBE             | I/O | GBE0_MDI3-     | P19 | S20 | GBE1_MDI1+                   | I/O | GBE            |

| GBE             | I/O | GBE0_MDI3+     | P20 | S21 | GBE1_MDI1-                   | I/O | GBE            |

| GBE             | Ο   | GBE0_LINK100#  | P21 | S22 | GBE1_LINK1000#               | 0   |                |

| GBE             | Ο   | GBE0_LINK1000# | P22 | S23 | GBE1_MDI2+                   | I/O | GBE            |

| GBE             | I/O | GBE0_MDI2-     | P23 | S24 | GBE1_MDI2-                   | I/O | GBE            |

| GBE             | I/O | GBE0_MDI2+     | P24 | S25 | GND                          |     |                |

| GBE             | Ο   | GBEO_LINK_ACT# | P25 | S26 | GBE1_MDI3-                   | I/O | GBE            |

| GBE             | I/O | GBE0_MDI1-     | P26 | S27 | GBE1_MDI3+                   | I/O | GBE            |

| GBE             | I/O | GBE0_MDI1+     | P27 | S28 | N.C.                         |     |                |

|                 |     | N.C.           | P28 | S29 | SERDES_0_TX+ /<br>PCIE_D_TX+ | Ο   | SERDES / PCI-e |

| GBE             | I/O | GBE0_MDI0-     | P29 | S30 | SERDES_0_TX- /<br>PCIE_D_TX- | Ο   | SERDES / PCI-e |

| GBE             | I/O | GBE0_MDI0+     | P30 | S31 | GBE1_LINK_ACT#               | Ο   | GBE            |

|                 |     | N.C.           | P31 | S32 | SERDES_0_RX+ /<br>PCIE_D_RX+ | I   | SERDES / PCI-e |

|                 |     | GND            | P32 | S33 | SERDES_0_RX- /<br>PCIE_D_RX- | I   | SERDES / PCI-e |

| SDIO_CARD       | I   | SDIO_WP        | P33 | S34 | GND                          |     |                |

| SDIO_CARD       | I/O | SDIO_CMD       | P34 | S35 | USB4+                        | I/O | USB            |

| SDIO_CARD       | I   | SDIO_CD#       | P35 | S36 | USB4-                        | I/O | USB            |

| SDIO_CARD       | Ο   | SDIO_CK        | P36 | S37 | N.C.                         |     |                |

| SDIO_CARD       | Ο   | SDIO_PWR_EN    | P37 | S38 | AUDIO_MCK                    | 0   | AUDIO          |

|                 |     | GND            | P38 | S39 | I2SO_LRCK                    | I/O | AUDIO          |

| SDIO_CARD       | I/O | SDIO_D0        | P39 | S40 | I2S0_SDOUT                   | Ο   | AUDIO          |

| SDIO_CARD       | I/O | SDIO_D1        | P40 | S41 | I2SO_SDIN                    | Ī   | AUDIO          |

| SDIO_CARD       | I/O | SDIO_D2        | P41 | S42 | 12S0_CK                      | I/O | AUDIO          |

| SDIO_CARD       | I/O | SDIO_D3        | P42 | S43 | ESPI_ALERTO#                 | 1   | ESPI INTERFACE |

| SPI 0 INTERFACE | Ο   | SPI0_CS0#      | P43 | S44 | ESPI_ALERT1#                 |     | ESPI INTERFACE |

| SPI 0 INTERFACE        | 0   | SPIO_CK              | P44 | S45 | MDIO_CLK    | 0   | SERDES         |

|------------------------|-----|----------------------|-----|-----|-------------|-----|----------------|

| SPI 0 INTERFACE        |     | SPIO_DIN             | P45 | S46 | MDIO_DAT    | I/O | SERDES         |

| SPI 0 INTERFACE        | 0   | SPIO_DO              | P46 | S47 | GND         |     |                |

|                        |     | GND                  | P47 | S48 | I2C_GP_CK   | I/O | I2C            |

| SATA                   | 0   | SATA_TX+             | P48 | S49 | I2C_GP_DAT  | I/O | I2C            |

| SATA                   | 0   | SATA_TX-             | P49 | S50 | HDA_SYNC    | I/O | HD AUDIO       |

|                        |     | GND                  | P50 | S51 | HDA_SDO     | 0   | HD AUDIO       |

| SATA                   |     | SATA_RX+             | P51 | S52 | HDA_SDI     |     | HD AUDIO       |

| SATA                   |     | SATA_RX-             | P52 | S53 | HDA_CK      | 0   | HD AUDIO       |

|                        |     | GND                  | P53 | S54 | SATA_ACT#   | Ο   | SATA           |

| SPI 1 / eSPI INTERFACE | 0   | SPI1_CS0#/ESPI_CS0#  | P54 | S55 | USB5_EN_OC# | I/O | USB            |

| SPI 1 / eSPI INTERFACE |     | SPI1_CS1#/ESPI_CS1#  | P55 | S56 | ESPI_IO_2   | I/O | eSPI INTERFACE |

| SPI 1 / eSPI INTERFACE | 0   | SPI1_CK / ESPI_CK    | P56 | S57 | ESPI_IO_3   | I/O | eSPI INTERFACE |

| SPI 1 / eSPI INTERFACE | I/O | SPI1_DIN / ESPI_IO_1 | P57 | S58 | ESPI_RESET# | Ο   | eSPI INTERFACE |

| SPI 1 / eSPI INTERFACE | I/O | SPI1_DO / ESPI_IO_0  | P58 | S59 | USB5+       | I/O | USB            |

|                        |     | GND                  | P59 | S60 | USB5-       | I/O | USB            |

| USB                    | I/O | USB0+                | P60 | S61 | GND         |     |                |

| USB                    | I/O | USB0-                | P61 | S62 | USB3_SSTX+  | Ο   | USB            |

| USB                    | I/O | USB0_EN_OC#          | P62 | S63 | USB3_SSTX-  | 0   | USB            |

|                        |     | N.C.                 | P63 | S64 | GND         |     |                |

|                        |     | N.C.                 | P64 | S65 | USB3_SSRX+  |     | USB            |

| USB                    | I/O | USB1+                | P65 | S66 | USB3_SSRX-  |     | USB            |

| USB                    | I/O | USB1-                | P66 | S67 | GND         |     |                |

| USB                    | I/O | USB1_EN_OC#          | P67 | S68 | USB3+       | I/O | USB            |

|                        |     | GND                  | P68 | S69 | USB3-       | I/O | USB            |

| USB                    | I/O | USB2+                | P69 | S70 | GND         |     |                |

| USB                    | I/O | USB2-                | P70 | S71 | USB2_SSTX+  | Ο   | USB            |

| USB                    | I/O | USB2_EN_OC#          | P71 | S72 | USB2_SSTX-  | Ο   | USB            |

| FUSA                   | I/O | SPIM_MOSI            | P72 | S73 | GND         |     |                |

| FUSA                   | I/O | THERMTRIP            | P73 | S74 | USB2_SSRX+  | 1   | USB            |

|                        |     |                      |     |     |             |     |                |

| USB               | I/O | USB3_EN_OC#    | P74  | S75  | USB2_SSRX-    |     | USB               |

|-------------------|-----|----------------|------|------|---------------|-----|-------------------|

| PCI_e             | 0   | PCIE A RST#    | P75  | S76  | PCIE_B_RST#   | 0   | PCI-e             |

| USB               | 1/0 | USB4_EN_OC#    | P76  | S77  | PCIE_C_RST#   | 0   | PCI-e             |

| PCI-e             | I   | PCIE_B_CLKREQ# | P77  | S78  | PCIE_C_RX+    | I   | PCI-e             |

| PCI-e             | I   | PCIE_A_CLKREQ# | P78  | S79  | PCIE_C_RX-    | - 1 | PCI-e             |

|                   |     | GND            | P79  | S80  | GND           |     | PCI-e             |

| PCI-e             | 0   | PCIE_C_REFCK+  | P80  | S81  | PCIE_C_TX+    | 0   | PCI-e             |

| PCI-e             | 0   | PCIE_C_REFCK-  | P81  | S82  | PCIE_C_TX-    | 0   | PCI-e             |

|                   |     | GND            | P82  | S83  | GND           |     |                   |

| PCI-e             | Ο   | PCIE_A_REFCK+  | P83  | S84  | PCIE_B_REFCK+ | 0   | PCI-e             |

| PCI-e             | 0   | PCIE_A_REFCK-  | P84  | S85  | PCIE_B_REFCK- | 0   | PCI-e             |

|                   |     | GND            | P85  | S86  | GND           |     |                   |

| PCI-e             | I   | PCIE_A_RX+     | P86  | S87  | PCIE_B_RX+    | I   | PCI-e             |

| PCI-e             | I   | PCIE_A_RX-     | P87  | S88  | PCIE_B_RX-    | I   | PCI-e             |

|                   |     | GND            | P88  | S89  | GND           |     |                   |

| PCI-e             | Ο   | PCIE_A_TX+     | P89  | S90  | PCIE_B_TX+    | 0   | PCI-e             |

| PCI-e             | Ο   | PCIE_A_TX-     | P90  | S91  | PCIE_B_TX-    | 0   | PCI-e             |

|                   |     | GND            | P91  | S92  | GND           |     |                   |

| DP++ INTERFACE #1 | 0   | DP1_LANE0+     | P92  | S93  | DPO_LANEO+    | 0   | DP++ INTERFACE #0 |

| DP++ INTERFACE #1 | Ο   | DP1_LANE0-     | P93  | S94  | DPO_LANEO-    | Ο   | DP++ INTERFACE #0 |

|                   |     | GND            | P94  | S95  | DP0_AUX_SEL   | 1   | DP++ INTERFACE #0 |

| DP++ INTERFACE #1 | 0   | DP1_LANE1+     | P95  | S96  | DPO_LANE1+    | 0   | DP++ INTERFACE #0 |

| DP++ INTERFACE #1 | 0   | DP1_LANE1-     | P96  | S97  | DPO_LANE1-    | 0   | DP++ INTERFACE #0 |

|                   |     | GND            | P97  | S98  | DPO_HPD       | 1   | DP++ INTERFACE #0 |

| DP++ INTERFACE #1 | Ο   | DP1_LANE2+     | P98  | S99  | DPO_LANE2+    | 0   | DP++ INTERFACE #0 |

| DP++ INTERFACE #1 | Ο   | DP1_LANE2-     | P99  | S100 | DPO_LANE2-    | Ο   | DP++ INTERFACE #0 |

|                   |     | GND            | P100 | S101 | GND           |     |                   |

| DP++ INTERFACE #1 | Ο   | DP1_LANE3+     | P101 | S102 | DPO_LANE3+    | 0   | DP++ INTERFACE #0 |

| DP++ INTERFACE #1 | 0   | DP1_LANE3-     | P102 | S103 | DPO_LANE3-    | 0   | DP++ INTERFACE #0 |

|                   |     | GND            | P103 | S104 | N.C.          |     |                   |

| DP++ INTERFACE #1 |     | DP1_HPD               | P104 | S105 | DPO_AUX+              | I/O | DP++ INTERFACE #0 |

|-------------------|-----|-----------------------|------|------|-----------------------|-----|-------------------|

| DP++ INTERFACE #1 | I/O | DP1_AUX+              | P105 | S106 | DPO_AUX-              | I/O | DP++ INTERFACE #0 |

| DP++ INTERFACE #1 | I/O | DP1_AUX-              | P106 | S107 | LCD1_BKLT_EN          | 0   | LCD_SUPPORT       |

| DP++ INTERFACE #1 |     | DP1_AUX_SEL           | P107 | S108 | LVDS1_CK+             | 0   | PRIMARY_DISPLAY   |

| GPIO / FUSA       | I/O | GPIO0 / OKNOKO        | P108 | S109 | LVDS1_CK-             | 0   | PRIMARY_DISPLAY   |

| GPIO / FUSA       | I/O | GPIO1 / OKNOK1        | P109 | S110 | GND                   |     |                   |

| GPIO / FUSA       | I/O | GPIO2 / ALERT#        | P110 | S111 | LVDS1_0+              | Ο   | PRIMARY_DISPLAY   |

| GPIO / FUSA       | I/O | GPIO3 / SPIS_CS#      | P111 | S112 | LVDS1_0-              | Ο   | PRIMARY_DISPLAY   |

| GPIO / FUSA       | I/O | GPIO4 / SPIS_SCLK     | P112 | S113 | N.C.                  |     |                   |

| GPIO / FUSA       | I/O | GPIO5 / SPIS_MISO     | P113 | S114 | LVDS1_1+              | Ο   | PRIMARY_DISPLAY   |

| GPIO / FUSA       | I/O | GPIO6 / SPIS_MOSI     | P114 | S115 | LVDS1_1-              | 0   | PRIMARY_DISPLAY   |

| GPIO / FUSA       | I/O | GPIO7 / CHXPMIC_EN    | P115 | S116 | LCD1_VDD_EN           | Ο   | LCD_SUPPORT       |

| GPIO / FUSA       | I/O | GPIO8 / CHX_RLYSWITCH | P116 | S117 | LVDS1_2+              | Ο   | PRIMARY_DISPLAY   |

| GPIO / FUSA       | I/O | GPIO9 / CHXOKNOX0     | P117 | S118 | LVDS1_2-              | Ο   | PRIMARY_DISPLAY   |

| GPIO / FUSA       | I/O | GPIO10 / CHXOKNOK1    | P118 | S119 | GND                   |     |                   |

| GPIO / FUSA       | I/O | GPIO11 / SPIM_CS#     | P119 | S120 | LVDS1_3+              | Ο   | PRIMARY_DISPLAY   |

|                   |     | GND                   | P120 | S121 | LVDS1_3-              | Ο   | PRIMARY_DISPLAY   |

| MANAGEMENT        | I/O | I2C_PM_CK             | P121 | S122 | LCD1_BKLT_PWM         | Ο   | LCD_SUPPORT       |

| MANAGEMENT        | I/O | I2C_PM_DAT            | P122 | S123 | GPIO13 / SPIM_MISO    | I/O | GPIO / FUSA       |

| BOOT_SEL          |     | BOOT_SEL0#            | P123 | S124 | GND                   |     |                   |

| BOOT_SEL          |     | BOOT_SEL1#            | P124 | S125 | LVDS0_0+ / eDP0_TX0+  | 0   | PRIMARY_DISPLAY   |

| BOOT_SEL          |     | BOOT_SEL2#            | P125 | S126 | LVDS0_0- / eDP0_TX0-  | Ο   | PRIMARY_DISPLAY   |

| MANAGEMENT        | 0   | RESET_OUT#            | P126 | S127 | LCD0_BKLT_EN          | 0   | LCD_SUPPORT       |

| MANAGEMENT        |     | RESET_IN#             | P127 | S128 | LVDS0_1+ / eDP0_TX1+  | Ο   | PRIMARY_DISPLAY   |

| MANAGEMENT        | Ī   | POWER_BTN#            | P128 | S129 | LVDS0_1-/eDP0_TX1+    | 0   | PRIMARY_DISPLAY   |

| ASYNC_SERIAL      | Ο   | SERO_TX               | P129 | S130 | GND                   |     |                   |

| ASYNC_SERIAL      | Ī   | SERO_RX               | P130 | S131 | LVDS0_2+ / eDP0_TX2+  | 0   | PRIMARY_DISPLAY   |

| ASYNC_SERIAL      | Ο   | SERO_RTS#             | P131 | S132 | LVDS0_2- / eDP0_TX2-  | 0   | PRIMARY_DISPLAY   |

| ASYNC_SERIAL      | Ī   | SERO_CTS#             | P132 | S133 | LCD0_VDD_EN           | 0   | LCD_SUPPORT       |

|                   |     | GND                   | P133 | S134 | LVDS0_CK+ / eDP0_AUX+ | Ο   | PRIMARY_DISPLAY   |

| ASYNC_SERIAL | Ο | SER1_TX   | P134 | S135 | LVDS0_CK-/eDP0_AUX-  | Ο   | PRIMARY_DISPLAY |

|--------------|---|-----------|------|------|----------------------|-----|-----------------|

| ASYNC_SERIAL | I | SER1_RX   | P135 | S136 | GND                  |     |                 |

| ASYNC_SERIAL | Ο | SER2_TX   | P136 | S137 | LVDS0_3+ / eDP0_TX3+ | Ο   | PRIMARY_DISPLAY |

| ASYNC_SERIAL | I | SER2_RX   | P137 | S138 | LVDS0_3- / eDP0_TX3- | Ο   | PRIMARY_DISPLAY |

| ASYNC_SERIAL | Ο | SER2_RTS# | P138 | S139 | I2C_LCD_CK           | 0   | LCD_SUPPORT     |

| ASYNC_SERIAL | I | SER2_CTS# | P139 | S140 | I2C_LCD_DAT          | I/O | LCD_SUPPORT     |

| ASYNC_SERIAL | Ο | SER3_TX   | P140 | S141 | LCD0_BKLT_PWM        | 0   | LCD_SUPPORT     |

| ASYNC_SERIAL | I | SER3_RX   | P141 | S142 | GPIO12 / SPIM_SCLK   | I/O | GPIO / FUSA     |

|              |   | GND       | P142 | S143 | GND                  |     |                 |

| CAN          | Ο | CANO_TX   | P143 | S144 | eDP0_HPD             | I   | PRIMARY_DISPLAY |

| CAN          | I | CANO_RX   | P144 | S145 | WDT_TIME_OUT#        | Ο   | WATCHDOG        |

|              |   | N.C.      | P145 | S146 | PCIE_WAKE#           | I   | PCI_e           |

|              |   | N.C.      | P146 | S147 | VDD_RTC              |     |                 |

|              |   | VDD_IN    | P147 | S148 | LID#                 | I   | MANAGEMENT      |

|              |   | VDD_IN    | P148 | S149 | SLEEP#               | I   | MANAGEMENT      |

|              |   | VDD_IN    | P149 | S150 | VIN_PWR_BAD#         | I   | MANAGEMENT      |

|              |   | VDD_IN    | P150 | S151 | CHARGING#            | 1   | MANAGEMENT      |

|              |   | VDD_IN    | P151 | S152 | CHARGER_PRSNT#       | I   | MANAGEMENT      |

|              |   | VDD_IN    | P152 | S153 | CARRIER_STBY#        | 0   | MANAGEMENT      |

|              |   | VDD_IN    | P153 | S154 | CARRIER_PWR_ON       | Ο   | MANAGEMENT      |

|              |   | VDD_IN    | P154 | S155 | FORCE_RECOV#         | 1   | BOOT_SEL        |

|              |   | VDD_IN    | P155 | S156 | BATLOW#              | I   | MANAGEMENT      |

|              |   | VDD_IN    | P156 | S157 | TEST#                | I   | MANAGEMENT      |

|              |   |           |      | S158 | GND                  |     |                 |

|              |   |           |      | 1    |                      |     |                 |

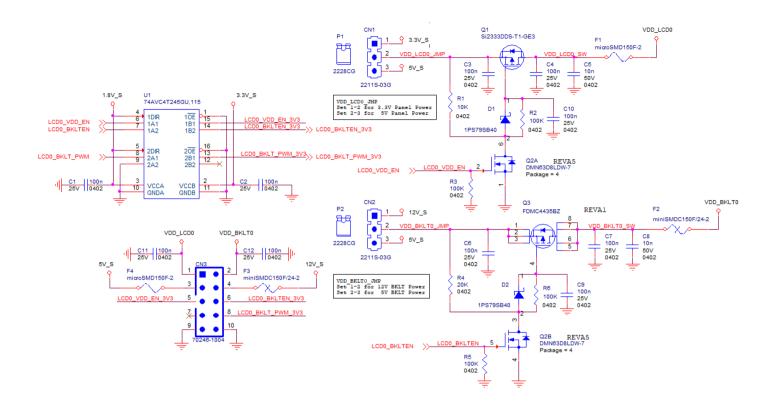

#### 3.2.1.1 LCD Display Support Signals

The Intel® family of SOCs formerly coded as Elkhart Lake offers signal for direct driving of a panel and its display's backlight: enabling signals for panel (LCD0\_VDD\_EN) and backlight (LCD0\_BKLT\_EN), Backlight Brightness Control signal (LCD0\_BKLT\_PWM). These signals have an electrical of +1.8V\_RUN, so they will be adapted/level shifted by the carrier board for external use.

There are also the signals necessary for driving I2C Data and Clock lines of LCD EDID EEPROM.

The panel control signals are:

LCDO\_VDD\_EN: Panel #0 Panel enable signal. Active high signal, +1.8V\_RUN electrical level Output.

LCD0\_BKLT\_EN: Panel #0 Panel Backlight Enable signal. It can be used to turn On/Off the backlight's lamps of a connected LVDS display. Active high signal, +1.8V\_RUN electrical level Output.

LCD0\_BKLT\_PWM: This signal can be used to adjust the Panel #0 backlight brightness in displays supporting Pulse Width Modulated (PWM) regulations. +1.8V RUN electrical level Output.

I2C\_LCD\_DAT: LCD I2C Data. This signal is used to read the LCD display EDID EEPROM.  $+1.8V_RUN$  electrical level with a  $2.2k\Omega$  pull-up resistor.

$12C\_LCD\_CLK$ : LCD 12C Clock: This signal is used to read the LCD display EDID EEPROM.  $+1.8V\_RUN$  electrical level with a  $2.2k\Omega$  pull-up resistor.

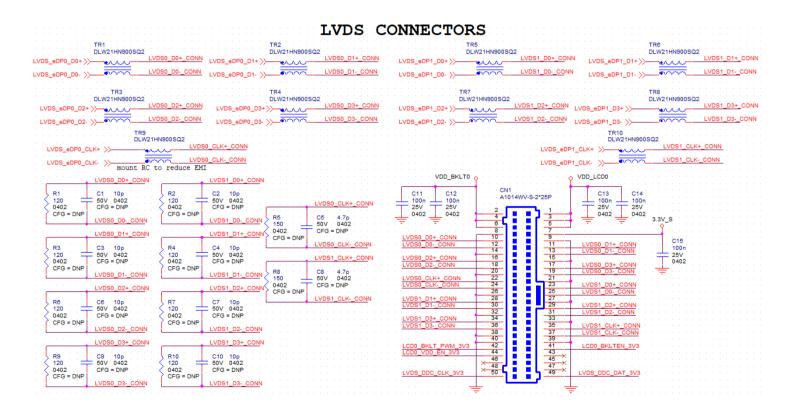

Please refer to the following schematics as an example of implementation for LCD and backlight support signals driving connection + voltage level shifters on the carrier board.

All schematics (henceforth also referred to as material) contained in this manual are provided by SECO S.p.A. for the sole purpose of supporting the customers' internal development activities.

!

The schematics are provided "AS IS". SECO makes no representation regarding the suitability of this material for any purpose or activity and disclaims all warranties and conditions with regard to said material, including but not limited to, all expressed or implied warranties and conditions of merchantability, suitability for a specific purpose, title and non-infringement of any third party intellectual property rights.

The customer acknowledges and agrees to the conditions set forth that these schematics are provided only as an example and that he will conduct an independent analysis and exercise judgment in the use of any and all material. SECO declines all and any liability for use of this or any other material in the customers' product design

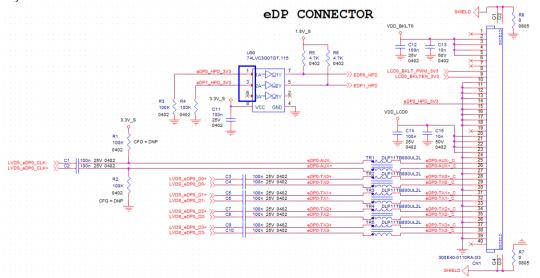

#### 3.2.1.2 eDP / Dual Channel LVDS (factory alternatives)

The Intel® family of SOCs formerly coded as Elkhart Lake offers a wide range of single and multi-purpose Digital Display Interfaces.

SM-C93 offers one embedded Display Port (eDP) interface or Dual Channel LVDS (factory alternatives), two multimode display ports (DP++) or one multimode display port (DP++) and one HDMI.

The LVDS interface, which is frequently used in many application fields, is not directly supported by the SOC. For this reason, considering that LVDS dual channel interfaces can be factory alternative on the same pins with eDP interface, on SM-C93 module can be implemented an eDP to LVDS bridge (NXP PTN3460), which allow the implementation of a Dual Channel LVDS, with a maximum supported resolution of 1920x1200 @ 60Hz (dual channel mode). Such an interface is derived from the SOCs' dedicated eDP Interface.

Ţ

Please remember that LVDS interface is not native for the Intel® family of SOCs formerly coded as Elkhart Lake, it is derived from an optional eDP-to-LVDS bridge. Depending on the factory option purchased, on the same pins it is possible to have available LVDS or eDP interface. Please take care of specifying if it is necessary LVDS interface or eDP, before placing an order of SM-C93 module.

ONLY ONE set of signals from the following two sets are present, dependent on the factory board configuration.

EITHER the signals for Channel #0 are LVDS:

LVDS0\_0+/LVDS0\_0-: LVDS Channel #0 differential data pair #0.

LVDS0 1+/LVDS0 1-: LVDS Channel #0 differential data pair #1.

LVDS0\_2+/LVDS0\_2-: LVDS Channel #0 differential data pair #2.

LVDS0\_3+/LVDS0\_3-: LVDS Channel #0 differential data pair #3.

LVDS0\_CK+/LVDS0\_CK-: LVDS Channel #0 differential Clock.

OR the signals for Channel #0 are eDP:

eDP0\_TX0+/ eDP0\_TX0-: eDP Channel #0 differential data pair #0.

eDP0\_TX1+/ eDP0\_TX1-: eDP Channel #0 differential data pair #1.

eDP0\_TX2+/ eDP0\_TX2-: eDP Channel #0 differential data pair #2.

eDP0\_TX3+/ eDP0\_TX3-: eDP Channel #0 differential data pair #3.

eDP0\_AUX+/ eDP0\_AUX-: eDP Channel #0 differential Clock.

eDP0\_HPD: Hot Plug Detect, Active high Input signal of +1.8V\_RUN electrical level from carrier board. 1MΩ pull-down resistor is placed on module for this signal.

Please refer to the following schematics as an example of connection of eDP interface on the carrier board. Hot Plug Detect signal must be buffered to prevent back feeding of power from the display to the module as well as level translation.

The signals for Channel #1 are LVDS, when this interface is selected in factory board configuration, otherwise these pins will be not connected.

LVDS1\_1+ / LVDS1\_0- : LVDS Channel #1 differential data pair #0

LVDS1\_1+/ LVDS1\_1-: LVDS Channel #1 differential data pair #1

LVDS1\_2+/LVDS1\_2-: LVDS Channel #1 differential data pair #2

LVDS1\_3+/ LVDS1\_3-: LVDS Channel #1 differential data pair #3

LVDS1\_CK+/ LVDS1\_CK-: LVDS Channel #1 differential Clock

Please refer to the following schematics as an example of connection of dual channel LVDS interface on the carrier board, with EMI filtering section included.

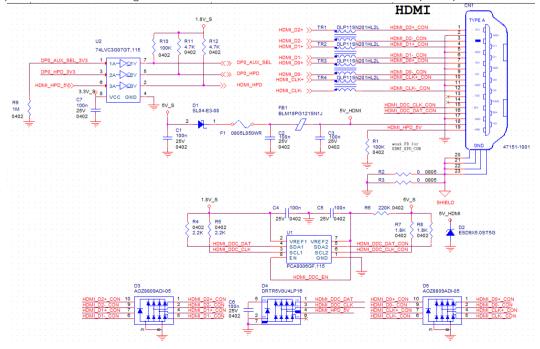

#### 3.2.1.3 HDMI / DP++ (factory alternatives) interface signals

As described in the previous paragraph, the Intel® family of SOCs formerly coded as Elkhart Lake offers, as secondary display interface, a native multimode Digital Display Interface, configurable as a factory alternative to work as a multimode Display Port (DP++) with a resolution up to 4096 x 2160 @60Hz or HDMl v1.4 with a resolution up to 3840 x 2160 @30Hz.

ONLY ONE set of signals from the following two sets are present, dependent on the factory board configuration.

EITHER the signals for the Channel are HDMI:

HDMI\_D0+/HDMI\_D0-: HDMI Output Differential Pair #0 HDMI\_D1+/HDMI\_D1-: HDMI Output Differential Pair #1 HDMI\_D2+/HDMI\_D2-: HDMI Output Differential Pair #2

HDMI\_CK+/HDMI\_CK-: HDMI Differential Clock

HDMI\_HPD: Hot Plug Detect, Active high Input signal of +1.8V\_RUN electrical level from carrier board. 1MΩ pull-down resistor is placed on module for this signal.

HDMI\_CTRL\_CK: DDC Clock line for HDMI panel. Bidirectional signal,  $+1.8V_RUN$  electrical level with a  $100k\Omega$  pull-up resistor

HDMI\_CTRL\_DAT: DDC Data line for HDMI panel. Bidirectional signal, +1.8V\_RUN electrical level with a 100kΩ pull-up resistor

Please refer to the above schematics as an example of connection of HDMI interface on the carrier board, with Voltage clamping diodes highly recommended on all signal lines for ESD suppression, as well as common mode choke inductors for EMI purpose. Voltage level shifters are necessary on Control data/Clock signals, as well as for Hot Plug Detect signal.

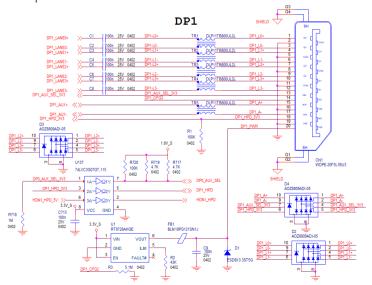

OR the signals for the Channel are DP++:

DP1\_LANEO+/ DP1\_LANEO-: DP Channel #1 Output Differential Pair #0

DP1\_LANE1+/ DP1\_LANE1-: DP Channel #1 Output Differential Pair #1

DP1\_LANE2+/ DP1\_LANE2-: DP Channel #1 Output Differential Pair #2

DP1\_LANE3+/ DP1\_LANE3-: DP Channel #1 Output Differential Pair #3

DP1\_AUX+: DDC Clock line for DP Channel #1. Bidirectional signal, +3.3V\_RUN electrical level with a 100kΩ pull-up resistor

DP1\_AUX-: DDC Data line for DP Channel #1. Bidirectional signal, +3.3V\_RUN electrical level with a 100kΩ pull-up resistor

DP1\_HPD: Hot Plug Detect, Active high Input signal of  $+1.8V_RUN$  electrical level from carrier board.  $1M\Omega$  pull-down resistor is placed on module for this signal.

DP1\_AUX\_SEL: Select input signal to switch between I2C Clock/Data for HDMI (high level) and Display Port Auxiliary Channel for DP/HDMI (low level).  $1M\Omega$  pull-down resistor is placed on module for this signal.

Please refer to the following schematics as an example of connection of DP interface on the carrier board, with Voltage clamping diodes highly recommended on all signal lines for ESD suppression. Hot Plug Detect signal must be buffered to prevent back feeding of power from the display to the module as well as level translation. Switch with settable current limit on power lines are recommended.

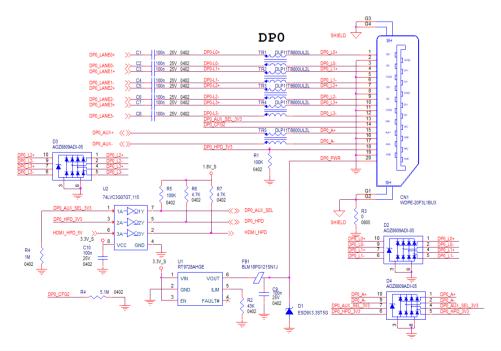

#### 3.2.1.4 DP++ interface signals

As described in the previous paragraph, the Intel® family of SOCs formerly coded as Elkhart Lake offers a native multimode Display Port (DP) interface, with a resolution up to 4096 x 2160 @60Hz

The signals related to DP++ are as follows:

DPO\_LANEO+/ DPO\_LANEO-: DP Channel #0 differential data pair #0.

DPO\_LANE1+/ DPO\_LANE1-: DP Channel #0 differential data pair #1.

DPO\_LANE2+/ DPO\_LANE2-: DP Channel #0 differential data pair #2.

DPO\_LANE3+/ DPO\_LANE3-: DP Channel #0 differential data pair #3.

DPO\_HPD: Hot Plug Detect, Active high Input signal of  $+1.8V_RUN$  electrical level from carrier board.  $1M\Omega$  pull-down resistor is placed on module for this signal.

DP0\_AUX+: DDC Clock line for DP Channel #0. Bidirectional signal, +3.3V\_RUN electrical level with a 100kΩ pull-up resistor

DPO\_AUX-: DDC Data line for DP Channel #0. Bidirectional signal, +3.3V\_RUN electrical level with a 100kΩ pull-up resistor

DPO\_AUX\_SEL: Select input signal to switch between I2C Clock/Data for HDMI (high level) and Display Port Auxiliary Channel for DP/HDMI (low level).  $1M\Omega$  pull-down resistor is placed on module for this signal.

Please refer to the following schematics as an example of connection of DP interface on the carrier board, with Voltage clamping diodes highly recommended on all

signal lines for ESD suppression. Hot Plug Detect signal must be buffered to prevent back feeding of power from the display to the module as well as level translation. Switch with settable current limit on power lines are recommended.

# 3.2.1.5 SATA interface signals

The Intel® family of SOCs formerly coded as Elkhart Lake offers one S-ATA interface.

The interface is Gen3 compliant, with support of 1.5Gbps, 3.0 Gbps and 6.0 Gbps data rates

Here following the signals related to SATA interface:

SATA\_TX+/SATA\_TX-: Serial ATA Channel #1 Transmit differential pair

SATA\_RX+/SATA\_RX-: Serial ATA Channel #1 Receive differential pair

SATA\_ACT#: Serial ATA Activity Led. Active low output signal at +3.3V\_RUN voltage

10nF AC series decoupling capacitors are placed on each line of SATA differential pairs.

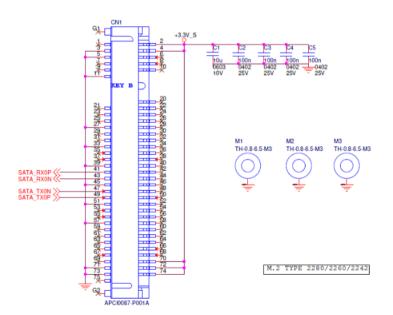

On the carrier board, these signals can be carried out directly to a SATA M 7p connector or switched for an M.2 SSD Slot, which allow plugging M.2 Socket 2 Key B Solid State Drives. Please refer to the following schematics as an example of connection of SATA interface on the carrier board to selected connector.

# 3.2.1.6 SDI/O interface signals

The Intel® family of SOCs formerly coded as Elkhart Lake offers one SD Card controller, able to support SD Card 3.0 interface.

Such an SD controller complies with SD Host Controller Standard Specification version 3.01 and only supports devices for data storage.

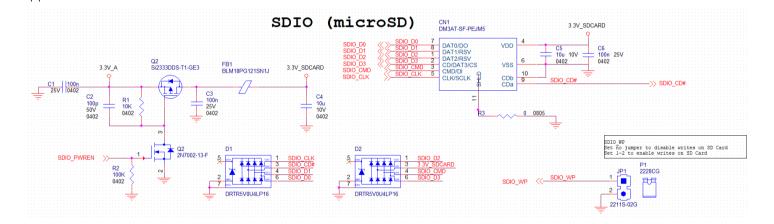

The SD port is externally accessible through the SD Card Slot connector, can work in 1-bit and 4-bit mode operation with data rate up to 104MB/s. The signals related to SDIO are as follows:

SDIO\_WP: Write Protect input, electrical level  $+3.3V_RUN$  with  $10k\Omega$  pull-up resistor. It is used to communicate the status of Write Protect switch of the external SD card. Since microSD cards don't manage this signal, it is important that, when designing carrier boards with microSD slots, this signal must be tied to GND, otherwise the OS will always consider the card as protected from writing.

SDIO\_CMD: Command/Response line. Bidirectional signal, electrical level +3.3V\_RUN, used to send command from Host (Intel processor) to the connected card, and to send the response from the card to the Host.

SDIO\_CD#: Card Detect Input. Active Low Signal, electrical level  $+3.3V_RUN$  with  $10k\Omega$  pull-up resistor. This signal must be externally pulled low to signal that a SDIO/MMC Card is present.

SDIO\_CK: Clock Line (output), 50 MHz maximum frequency for SD/SDIO High Speed Mode.

SDIO\_PWR\_EN: SDIO Power Enable output, active high signal, electrical level +3.3V\_RUN. It is used to enable the power line supplying SD/SDIO/MMC devices. SDIO\_[D0÷D3]: SD Card data bus. SDIO\_D0 signal is used for all communication modes. SDIO\_[D1÷D3] signals are required for 4-bit communication mode. Please refer to the following schematics as an example of connection of SDIO interface on the carrier board, with Voltage clamping diodes highly recommended on

all signal lines for ESD suppression.

# 3.2.1.7 SPI interface signals

The Intel® family of SOCs formerly coded as Elkhart Lake offers also one dedicated Serial Peripheral Interface (SPI0) for boot device purpose and one general purpose Serial Peripheral Interface (SPI1) or eSPI (factory alternatives).

The signals related to SPIO are as follows:

SPIO\_CSO#: SPI channel #0 primary Chip select, active low output signal. Electrical level +1.8V\_ALW

On the same bus there is a second SPI slave device (BIOS flash boot device), mounted on the module, connected to a dedicated chip select signal

SPIO\_CK: SPI channel #0 Clock Output to carrier board's SPI embedded devices. Electrical level +1.8V\_ALW

SPIO\_DIN: SPI channel #0 Master Data Input, electrical level +1.8V\_ALW

SPIO\_DO: SPI channel #0 Master Data Output, electrical level +1.8V\_ALW

ONLY ONE set of signals from the following two sets are present, dependent on the factory board configuration.

EITHER the signals for the SPI1 are general-purpose SPI bus:

SPI1\_CSO#: SPI channel #1 primary Chip select, active low output signal. Electrical level +1.8V\_ALW

SPI1\_CS1#: SPI channel #1 secondary Chip select, active low output signal. Electrical level +1.8V\_ALW

SPI1\_CK: SPI channel #1 Clock Output to carrier board's SPI embedded devices. Electrical level +1.8V\_ALW

SPI1\_DIN: SPI0 channel #1 Master Data Input, electrical level +1.8V\_ALW

SPI1 DO: SPI0 channel #1 Master Data Output, electrical level +1.8V ALW

OR the signals for the SPI1 are Enhanced Serial Peripheral Interface (eSPI) bus:

ESPI\_CK: ESPI Master Clock Output. Electrical level +1.8V\_ALW. The reference timing signal for all the serial input and output operations

ESPI\_CSO#: ESPI Master Chip Select Output #0. Electrical level +1.8V\_ALW. Driven low by the processor to select the ESPI slave device on the carrier board.

ESPI\_CS1#: ESPI Master Chip Select Output #1. Electrical level +1.8V\_ALW. This signal must be used only in case there are two ESPI devices on the carrier board, and the first chip select signal (ESPI\_CS0#) has already been used. It must not be used in case there is only one ESPI device

ESPI\_IO\_[0:3]: ESPI Master Data Bidirectional. Electrical level +1.8V\_ALW. Data transfer between the master and slaves. In Single I/O mode, ESPI\_IO\_0 is the eSPI master output/eSPI slave input (MOSI) whereas ESPI\_IO\_1 is the eSPI master input/eSPI slave output (MISO).

ESPI\_RESET#: ESPI Reset. Output. Electrical level +1.8V\_ALW with 75k\O pull-down resistor. Reset the ESPI interface for both master and slaves.

ESPI\_ALERTO#: Alert signal driven by the slave ESPI slave device #0. Input. Electrical level +1.8V\_ALW

ESPI\_ALERT1#: Alert signal driven by the slave ESPI slave device #1. Input. Electrical level +1.8V\_ALW

# 3.2.1.8 Audio interface signals

The Intel® family of SOCs formerly coded as Elkhart Lake supports I2S and HD audio format, thanks to native support offered by the processor to this audio codec standard.

Here are following the signals related to I2S Audio interface:

AUDIO\_MCK: Master clock output to Audio codec. Output from the module to the Carrier board, electrical level +1.8V\_RUN

I2SO\_LRCK: Left& Right audio interface #0 synchronization clock. Bi-Directional between the module to the Carrier board, electrical level +1.8V\_RUN

I2SO\_SDOUT: Digital audio interface #0 Output. Output from the module to the Carrier board, electrical level +1.8V\_RUN

12SO\_SDIN: Digital audio interface #0 Input. Input from the module to the Carrier board, electrical level +1.8V\_RUN

12SO\_CK: Digital audio interface #0 clock. Bi-Directional between the module to the Carrier board, electrical level +1.8V\_RUN

All these signals can be connected, on the Carrier Board, to an I2S Audio Codec. Please refer to the chosen Codec's Reference Design Guide for correct implementation of audio section on the carrier board.

Here are following the signals related to HD Audio interface:

HDA\_SYNC: Synchronization clock. Bi-Directional between the module to the Carrier board, electrical level +1.8V\_RUN

HDA\_SDO: Digital audio Output. Output from the module to the Carrier board, electrical level +1.8V\_RUN

HDA\_SDI: Digital audio Input. Input from the module to the Carrier board, electrical level +1.8V\_RUN

HDA\_CK: Digital audio clock. Bi-Directional between the module to the Carrier board, electrical level +1.8V\_RUN

HDA\_RST#: Digital Audio Reset. This signal is multiplexed with GPIO4. This pin has to be defined via BIOS so that GPIO4/HDA\_RST# is in HDA\_RST# modality.

All these signals have to be connected, on the Carrier Board, to an HD Audio Codec. Please refer to the chosen Codec's Reference Design Guide for correct implementation of audio section on the carrier board.

### 3.2.1.9 I2C / SM bus Interface

The Intel® family of SOCs formerly coded as Elkhart Lake supports one general purpose I2C interface and one power management SM bus.

Here are following the signals related to general purpose I2C interface:

12C\_GP\_CK: 12C General Purpose clock signal. Bi-Directional between the module to the Carrier board, electrical level +1.8V\_RUN with 2.2kΩ pull-up resistor

I2C\_GP\_DAT: I2C General Purpose data signal. Bi-Directional between the module to the Carrier board, electrical level +1.8V\_RUN with 2.2kΩ pull-up resistor Here are following the signals related to power management SM bus:

I2C\_PM\_CK:SMB Power management clock signal. Bi-Directional between the module to the Carrier board, electrical level +1.8V\_ALW with 2.2kΩ pull-up resistor. This signal is managed by the Embedded controller MEC1705 from Microchip.

I2C\_PM\_DAT: SMB Power management data signal. Bi-Directional between the module to the Carrier board, electrical level +1.8V\_ALW with 2.2kΩ pull-up resistor This signal is managed by the Embedded controller MEC1705 from Microchip.

# 3.2.1.10 Asynchronous Serial Ports (UART) interface signals

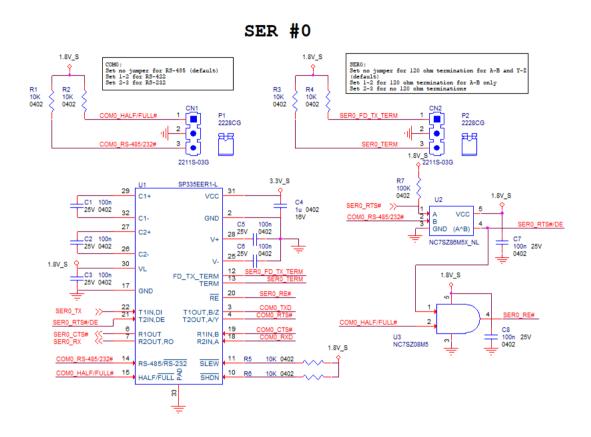

The Intel® family of SOCs formerly coded as Elkhart Lake offers in its Low Power Sub System (LPSS) two high speed UART, with a maximum speed of 115,200 kb/s or 3.6864Mb/s depending on Industry standards.

In addition, two additional UART are offered and managed by the Embedded controller MEC1705 from Microchip

SERO\_TX: UART #0 Interface, Serial data Transmit (output) line, 1.8V\_RUN electrical level. It is managed by Microchip MEC1705 controller.

SERO\_RX: UART #0 Interface, Serial data Receive (input) line, 1.8V\_RUN electrical level. It is managed by Microchip MEC1705 controller.

SERO\_RTS#: UART #0 Interface, Handshake signal, Request to Send (output) line, 1.8V\_ RUN electrical level

SERO\_CTS#: UART #0 Interface, Handshake signal, Clear to Send (Input) line, 1.8V\_ RUN electrical level

SER1\_TX: HS-UART #0 Interface, Serial data Transmit (output) line, 1.8V\_ RUN electrical level. It is directly managed by Intel processor.

SER1\_RX: HS-UART #0 Interface, Serial data Receive (input) line, 1.8V\_ RUN electrical level. It is directly managed by Intel processor.

SER2\_TX: UART #1 Interface, Serial data Transmit (output) line, 1.8V\_ RUN electrical level. It is managed by Microchip MEC1705 controller.

SER2\_RX: UART #1 Interface, Serial data Receive (input) line, 1.8V\_ RUN electrical level. It is managed by Microchip MEC1705 controller.

SER2\_RTS#: UART #1 Interface, Handshake signal, Request to Send (output) line, 1.8V\_ RUN electrical level.

SER2\_CTS#: UART #1 Interface, Handshake signal, Clear to Send (Input) line, 1.8V\_ RUN electrical level.

SER3\_RX: HS-UART #1 Interface, Serial data Receive (input) line, +1.8V\_RUN electrical level. It is directly managed by Intel processor.

SER3\_TX: HS-UART #1 Interface, Serial data Transmit (output) line, +1.8V\_RUN electrical level. It is directly managed by Intel processor.