# PRIMERGY BX920 S3

# System configurator and order-information guide

January 2014

# **Contents**

Instructions

Configuration diagram

Configurator

0 System software

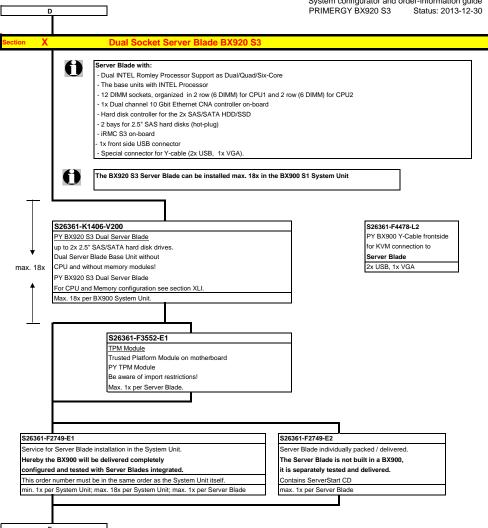

X BX920 S3 Dual Socket

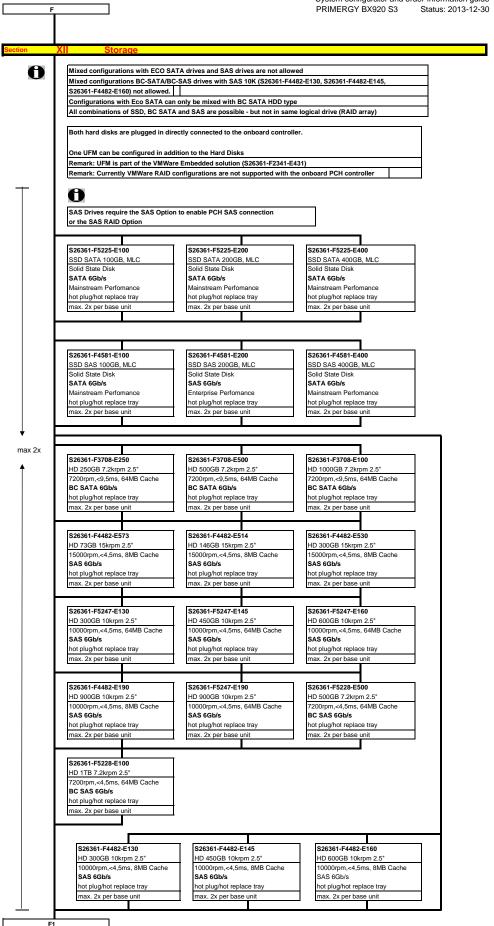

XI Processor XII Memory XIII Storage

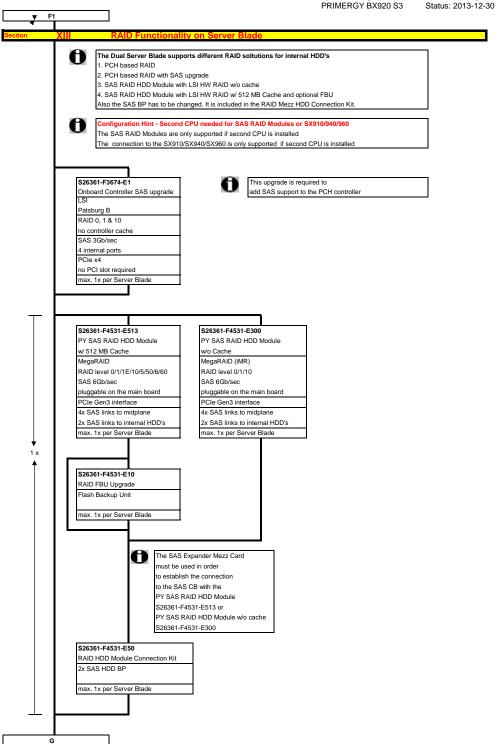

XIV RAID Functionality

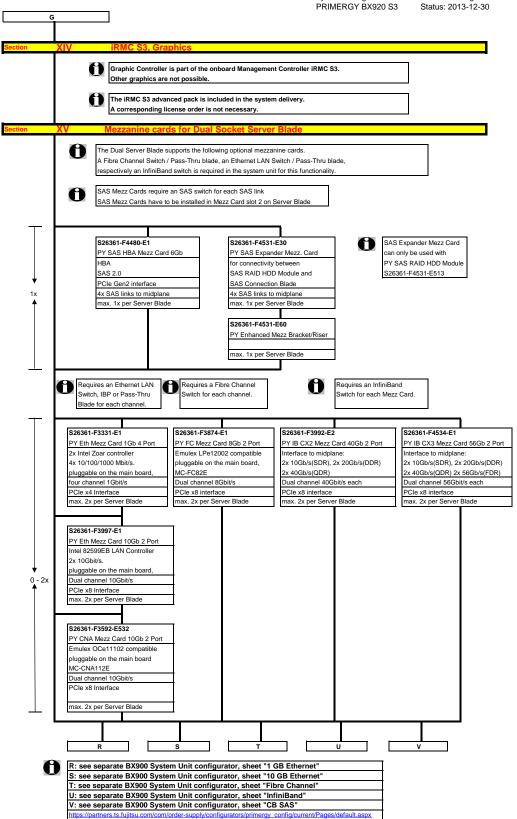

XV iRMC S3, Graphics

XVI Mezzanine Cards

Change report

**PRIMERGY Server**

# Instructions

This document contains basic product and configuration information that will enable you to configure your system via System-Architect.

Only the tool "System-Arcitect" will ensure a fast and proper configuration of your PRIMERGY server or your complete PRIMERGY Rack system.

Please pay attention to the naming conventions:

BX900 S1

System unit 1nd generation

BX920 S2 Dual Server Blade S2

You can configure your individual PRIMERGY server in order to adjust your specific requirements.

The System configurator is divided into several chapters that are identical to the current price list and PC-/ System-Architect.

Please follow the lines. If there is a junction, you can choose which way or component you would like to take. Go through the configurator by following the lines from the top to the bottom.

In one chapter you can only select as many components (here 3x) as the arrow indicates.

Please note that there are information symbols which indicate necessary information.

# For further information see:

http://ts.fujitsu.com/products/standard\_servers/index.html (internet)

https://partners.ts.fujitsu.com/com/order-supply/configurators/primergy\_config/Pages/Currentconfigurators.aspx

(extranet)

Prices and availability see price list and PC-/ System-Architect Subject to change and errors excepted

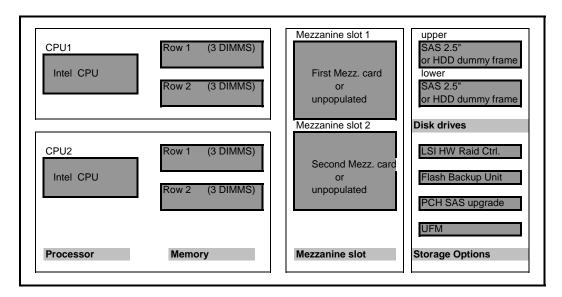

# Configuration diagram Dual Server Blade BX920 S3

Key:

Included in basic unit Option

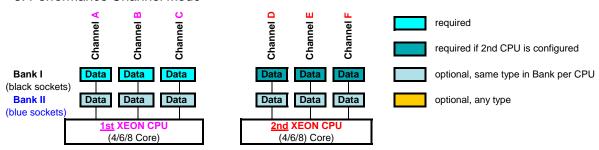

The population order for the CPU is: CPU1 first, then CPU2

The population order for the DIMMs: for each CPU, the DIMM row 1 (DIMMS 1A 1B 1C) (DIMMS 1D 1E 1F) first, then row 2 (DIMMs 2A, 2B, 2C) (DIMMs 2D, 2E, 2F)

G

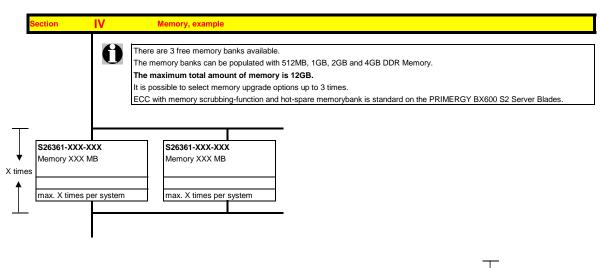

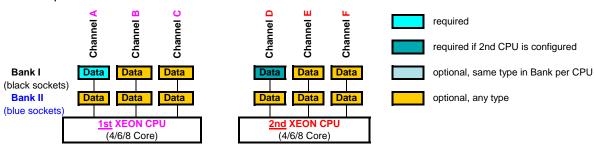

Section III Memory

#### - There are 6 memory slots per CPU for max.

192GB LRDIMM (6x 32GB 4R) 96GB RDIMM (6x 16GB 2R) 24GB UDIMM (6x 4GB)

#### => max. 384GB for two CPU's ( 192GB per CPU ), using LRDIMM

- The memory area is divided into 3 channels per CPU with 2 slots per channel

- Slot 1 of each channel belongs to memory bank 1, the slot 2 belongs to memory bank 2, slot 3 belongs to memory bank 3  $\,$

#### Registered, LR DIMMs and unbuffered memory modules can be selected

#### No mix of registered, load reduced and unbuffered modules allowed.

Memory can be operated at 1.5V or 1.35V, even if the modules are of low voltage type.

Memory operating voltage can be set within BIOS (1.5V is default setting for max. speed).

In a 2 DIMMs per channel configuration, following frequencies are supported:

- 1.5V - 1600MHz max (depending on CPU, special memory modules)

- 1.35V - 1333MHz max (depending on CPU)

SDDC (Chipkill) is supported for registered / load reduced x4 organized memory modules only

### 1.) In the "Independent Channel Mode" is following configuration possible

Channels can be populated in any order in Independent Channel Mode. All four channels may be populated in any order and have no matching requirements. All channels must run at the same interface frequency but individual channels may run at different DIMM timings (RAS latency, CAS latency, and so forth)

No mix of registered, load reduced and unbuffered modules allowed.

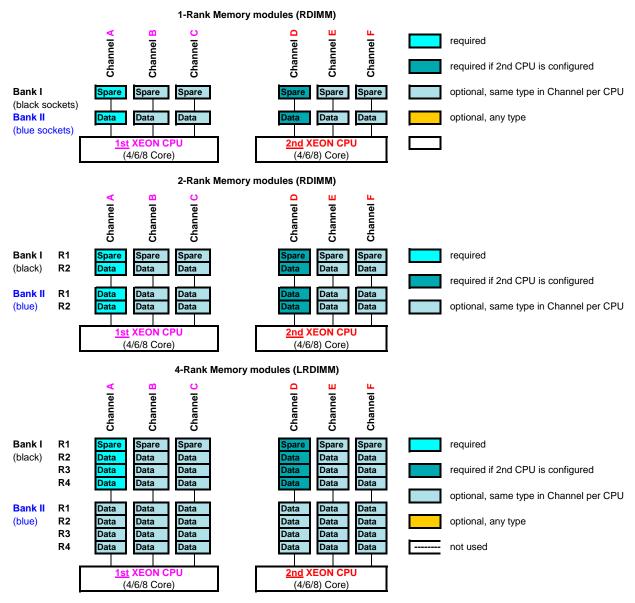

#### 2.) "Rank Sparing Mode" configuration

- Within a memory channel, one rank is a spare of the other ranks.

The Spare Rank is held in reserve and is not available as system memory

For the effective memory capacity, please refer to the spreadsheet below.

The BIOS is set to the rank sparing setting.

Minimum configuration is: 2x 1R, 2x 2R or 1x4R DDR3 module per channel

This mode is not supported by x8 organized memory modules

#### 3.) "Performance Mode" configuration

- In this configuration, the memory module population ex factory is spread across all channels.

The BIOS is set to the max. performance for memory.

Minimum configuration is: 3x identical modules

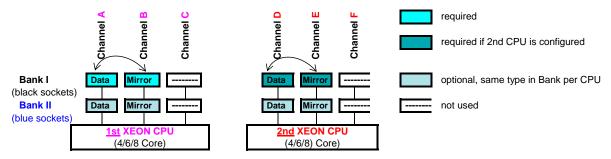

# 4.) In the "Mirrored Channel Mode" is following configuration possible

- Each memory bank can optionally be equipped with 4x registered or load reduced

In each memory bank channel A and B / C and D of CPU 1 or channel E and F / G and H of CPU 2 have to be

equipped with identical modules for mirrored channel mode. In channel B is always the mirrored memory of channel A of CPU 1

In channel E is always the mirrored memory of channel D of CPU 2

Minimum configuration is: 2x identical modules

This mode is not supported by x8 organized memory modules

G1

G1

S26361-F3695-E10 Independent Mode

Independent Channel Mode allows all channels to be populated in any order. No specific Memory RAS features are defined

#### Requires min 1 memory Module per CPU

S26361-F3695-E1 Rank Sparing Mode Installation

BIOS Setup factory preinstalled to this mode. One Rank is spare of other ranks on the same channel. Spare Rank is not shown in System Memory. For effective capacity within a channel, please have a look below.

Supported for RDIMM / LRDIMM only.

1x per CPU Req

#### Requires min 2x 1R/2R or 1x 4R modules per CPU

S26361-F3695-E2 Performance Mode Installation

BIOS Setup factory preinstalled for max. Performance, LV memory might be set to 1.5V operation. Four identical memory modules

will be equipped in one memory bank to achieve highest memory performance. All four modules are active and full capacity can be used.

#### Multiple of 3 identical modules to be configured per CPU

S26361-F3695-E3 Mirrored Channel Mode Installation

BIOS Setup factory preinstalled to this mode. Four identical memory modules are always equipped in one memory bank to use the

S26361-F3695-E614

Mirrored channel Mode. Only two modules contain active data, the remain two modules contain mirrored data

Supported for RDIMM / LRDIMM only.

Multiple of 2 identical modules to be configured per CPU

| Effective Memory capacity / Rank Sparing Mode, 1 Channel populated |       |    |     |    |     |     |      |        |      |    | oulated |         |  |

|--------------------------------------------------------------------|-------|----|-----|----|-----|-----|------|--------|------|----|---------|---------|--|

|                                                                    | UDIMM |    |     |    |     |     | RDIN | LRDIMM |      |    |         |         |  |

|                                                                    | 2GB   | 1R | 2GB | 2R | 4GB | 1R  | 8GB  | 2R     | 16GB | 2R | 16GB 4F | 32GB 4R |  |

| 1DPC                                                               | na    |    | na  |    | na  |     | na   |        | na   |    | 12GB    | 24GB    |  |

| 2DPC                                                               | na    |    | na  |    | 4GE | 4GB |      | 12GB   |      | В  | 28GB    | 56GB    |  |

|                                                                    |       |    |     |    |     |     |      |        |      |    |         |         |  |

#### Minimum one memory module or order code per CPU = first memory

Unbuffered Memory (UDIMM) no SDDC (chipkill) support

one DDR3 unbuffered ECC mem. Module, 1.35V

Choose up to 6 order codes per CPU

Choose up to 6 order codes per CPC

| 2GB (1x2GB) 1Rx8 L DDR3-1600 U ECC | S26361-F3694-E613 |

|------------------------------------|-------------------|

| 4GB (1x4GB) 2Rx8 L DDR3-1600 U ECC | S26361-F3694-E614 |

|                                    |                   |

# Registered Memory (RDIMM) no SDDC (chipkill) support

one DDR3 registered ECC mem. Module, 1.35V

No mix with any other types of memory modules possible

#### Choose up to 6x for 2R per CPU

For performance reasons, we do not recommend to configure more than 8 DIMMs per CPU

6x per CPU, max. 2/3 modules per channel

Registered Memory (RDIMM) with SDDC (chipkill) support one DDR3 registered ECC mem. Module, 1.35V

IGB (1x4GB) 2Rx8 L DDR3-1600 R ECC

1333MHz supported with up to 2DPC (6 modules/CPU)

Choose up to 6 order codes per CPU

2 modules per channel Registered Memory (RDIMM) with SDDC (chipkill) support

one DDR3 registered ECC mem. Module, 1.35V

1600MHz supported with up to 2DPC (8 modules/CPU)

at 1.5V

Choose up to 6 order codes per CPU

| 4GB (1x4GB) 1Rx4 L DDR3-1600 R ECC   | S26361-F3697-E614 |

|--------------------------------------|-------------------|

| 8GB (1x8GB) 2Rx4 L DDR3-1600 R ECC   | S26361-F3697-E615 |

| 16GB (1x16GB) 2Rx4 L DDR3-1600 R ECC | S26361-F3697-E616 |

|                                      |                   |

#### Load Reduced Memory (LRDIMM) with SDDC (chipkill) support

one DDR3 load reduced ECC mem. Module, 1.35V

Choose up to 6 order codes per CPU

16GB (1x16GB) 4Rx4 L DDR3-1333 LR ECC S26361-F3698-E616 32GB (1x32GB) 4Rx4 L DDR3-1333 LR ECC S26361-F3698-E617 Note 1.)

Max. DDR3 memory speed depends on the memory configuration (No of mem modules per channe) as well as on the CPU type. The memory channel with the lowest speed defines the speed of all CPU channels in the system, also for the channels of the second CPU if configured.

For real memory speed (depending on memory type / population),

please check the spreadsheet "Memory speed" below

new due to supply new due to supply

Mix of memory modules is only possible within the same group

# **Memory Configuration PRIMERGY BX920 S3**

Each CPU offers 6 Slots for DDR3 Memory Modules organised in 2 Banks and 3 Channels.

If you need more than 6 Slots you have to configure the 2nd CPU.

Depending on the amount of memory configured you can decide between 4 basic modes of operation (see explanation below).

There are 3 different kinds of DDR3 Memory Modules available: UDIMM / RDIMM and LRDIMM UDIMM / RDIMM / LRDIMM offer different functionality. Mix of UDIMM / RDIMM / LRDIMM is not alloved.

If 1.5V and 1.35V DIMMs are mixed, the DIMMs will run at 1.5V

| Mode                        | Configuration              | UDIMM | RDIMM  | RDIMM  | Application                                                                         |  |  |  |  |

|-----------------------------|----------------------------|-------|--------|--------|-------------------------------------------------------------------------------------|--|--|--|--|

|                             | ODIMINI RE                 |       | KDIMIM | LRDIMM |                                                                                     |  |  |  |  |

|                             |                            | х8    | х8     | x4     |                                                                                     |  |  |  |  |

| SDDC (chipkill) support     | any                        | no    | no     | yes    | detect multi-bit errors                                                             |  |  |  |  |

| Independant Channel<br>Mode | 1, 2 or 3 Modules per Bank | yes   | yes    | yes    | offers max. flexibility, upgradeability, capacity use UDIMM modules for lowest cost |  |  |  |  |

| Mirrored Channel Mode *)    | 2 identical Modules / Bank | no    | no     | yes    | offers maximum security                                                             |  |  |  |  |

| Performance Mode            | 3 identical Modules / Bank | yes   | yes    | yes    | offers maximum performance and capacity                                             |  |  |  |  |

| Rank Sparing Mode *)        | min. 2 Ranks / Channel     | no    | no     | yes    | balances security and capacity                                                      |  |  |  |  |

<sup>\*)</sup> For the delivery ex works the system will be prepared with dedicated BIOS setting.

| Capacity               | Configuration         | UDIMM | RDIMM  | LRDIMM  | Notes                       |

|------------------------|-----------------------|-------|--------|---------|-----------------------------|

| Min. Memory per CPU    | 1 Module / CPU        | 1x2GB | 1x4GB  | 1x 16GB | with one CPU                |

| Max. Memory per CPU    | 4/6 Modules / CPU     | 6x4GB | 6x16GB | 6x 32GB | with one CPU                |

| Max. Memory per System | 8/12 Modules / System | 48GB  | 96GB   | 384GB   | if second CPU is configured |

#### Memory-Speed:

Max. DDR3 memory speed depends on the memory configuration on one memory channel and the speed of the CPU The memory channel with the lowest speed defines the speed of all CPU channels in the system

| Mem. Speed provided by CPU                             |              | Real maximum memory-bus speed depending on CPU type, memory configuration (DPC) and voltage setting (BIOS) |          |              |              |          |              |                |          |              |              |          |              |                |          |              |          |          |

|--------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------|----------|--------------|--------------|----------|--------------|----------------|----------|--------------|--------------|----------|--------------|----------------|----------|--------------|----------|----------|

|                                                        |              | UDI                                                                                                        | MM 1     | 600N         | ИHz          |          |              | RD             | MM 1     | 16001        | ИHz          |          |              | LR             | DIMM     | 133          | 3MHz     |          |

| Voltage setting (BIOS)                                 |              | / [defa                                                                                                    | ault]    |              | 1.35\        | /        | 1.5\         | 1.5V [default] |          |              | 1.35V        |          |              | 1.5V [default] |          |              | 1.35V    |          |

|                                                        | 1<br>DPC     | 2<br>DPC                                                                                                   | 3<br>DPC | 1<br>DPC     | 2<br>DPC     | 3<br>DPC | 1<br>DPC     | 2<br>DPC       | 3<br>DPC | 1<br>DPC     | 2<br>DPC     | 3<br>DPC | 1<br>DPC     | 2<br>DPC       | 3<br>DPC | 1<br>DPC     | 2<br>DPC | 3<br>DPC |

| CPU with 1600MHz DDR3 Bus                              | 1333         | 1333                                                                                                       | -        | 1066         | 1066         | -        | 1600         | 1600           | -        | 1333         | 1333         | -        | 1333         | 1333           | -        | 1066         | 1066     | -        |

| CPU with 1333MHz DDR3 Bus<br>CPU with 1066MHz DDR3 Bus | 1333<br>1066 | 1333                                                                                                       | - /      | 1066<br>1066 | 1066<br>1066 | -        | 1333<br>1066 | 1333<br>1066   | -        | 1333<br>1066 | 1333<br>1066 | -        | 1333<br>1066 | 1333<br>1066   | -        | 1066<br>1066 |          | -        |

1R - Single Rank

2R - Dual Rank

4R - Quad Rank

1DPC = 1 DIMM per Channel 2DPC = 2 DIMM per Channel 3DPC = 3 DIMM per Channel

#### Configuration hints:

- The memory sockets on the systemboard offer a color coding:

Bank II black sockets

Bank III blue sockets

Bank III green sockets

- A so called Bank consits of 1 memory module on every Channel available on one CPU (examples see below)

Bank I on CPU 1/2 up to 3 memory modules connected to Channel A - F on the 1st/2nd CPU

Bank II on CPU 1/2 up to 3 memory modules connected to Channel A - F on the 1st/2nd CPU

- See below and next page for a detailed descriptions of the memory configuration supported.

# 1. Independent Channel Mode

Independent Channel Mode allows all channels to be populated in any order Can run with differently rated DIMMs and use the settings of the slowest DIMM installed in the system

#### 2. Mirrored Channel Mode

Mirrored Channel Mode requires identical modules on channel A / B (1st CPU) or channel D / E (2nd CPU) 50% of the capacity is used for the mirror => the available memory for applications is only half of the installed memory If this mode is used, a multiple of 2 identical modules has to be ordered.

### 3. Performance Channel Mode

Performance Channel Mode requires identical modules on all channels of each Bank per CPU. If this mode is used, a multiple of 3 identical modules has to be ordered.

# 4. Rank Sparing Mode

Rank Sparing Mode requires identical modules (same capacity and technology) within the same channel. The available memory for applications will vary depending on configuration. Please refer to the spreadsheet above "Effective Memory capacity with active Rank Sparing Mode". Population rule for Rank sparing mode is to achieve max. available memory.

# **Change Report**

| Date       | Order number       | Changes                                                                          |

|------------|--------------------|----------------------------------------------------------------------------------|

| 2013-10-18 | optional USB Comps | no longer available                                                              |

| 2013-07-18 |                    | Added comment about PCH Vmware limitation                                        |

| 2013-01-15 | S26361-F3674-E1    | Onboard Controller SAS upgrade - Speed corrected from 6GB/s to 3GB/s             |

| 2013-01-08 | S26361-F5228-E***  | New order number for 2.5" BC SAS 7.2K                                            |

| 2013-01-08 | S26361-F5247-E130  | New order number for SAS 10K (mix with BC-SATA supported, successor for *F5227*) |

| 2012-10-16 | hint               | SX910/910/960 only with 2nd CPU modified                                         |

| 2012-10-09 | hint               | SX910/910/960 only with 2nd CPU                                                  |

| 2012-10-02 |                    | changed USB info                                                                 |

| 2012-09-04 | S26361-F3592-E532  | as soon as available removed                                                     |

| 2012-07-23 | S26361-F5227-E1*   | New order for 2.5" 10K SAS HDD supporting mix with 2.5" BC-SATA HDD              |

| 2012-06-28 |                    | corrected text for 2 end Y-Cable                                                 |

| 2012-06-12 | S26361-F5225-E*00  | New order for SATA SSD's                                                         |

| 2012-05-29 |                    | Added 1333 RDIMM                                                                 |

| 2012-05-01 |                    | First Release                                                                    |

|            |                    |                                                                                  |

|            |                    |                                                                                  |

|            |                    |                                                                                  |

|            |                    |                                                                                  |

|            |                    |                                                                                  |

|            |                    |                                                                                  |

|            |                    |                                                                                  |

|            |                    |                                                                                  |

|            |                    |                                                                                  |

|            |                    |                                                                                  |

|            |                    |                                                                                  |

|            |                    |                                                                                  |

|            |                    |                                                                                  |