# i.MX 93 Hardware Design Guide

Rev. 1 — 13 April 2023

User guide

#### **Document Information**

| Information | Content                                                                                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | IMX93HDG, i.MX 93 series of processors, i.MX93 EVK, i.MX93 QSB, design checklist, layout recommendations, power connectivity, routing, thermal considerations, stack-up information |

| Abstract    | This document describes guidelines to design and test the i.MX 93 series of processors. It also includes board layout examples and design checklists.                               |

# 1 Overview

This document aims to help hardware engineers design and test the i.MX 93 series processors. It provides examples on board layout and design checklists to ensure first-pass success, and solutions to avoid board bring-up problems.

Prerequisites include familiarity of board layouts and board hardware terminology.

This guide is released with relevant device-specific hardware documentation, such as datasheets, reference manuals, and application notes. Some of these documents are available on <a href="www.nxp.com/imx93evk">www.nxp.com/imx93evk</a>.

## 1.1 Device supported

This document supports the i.MX 93 device. The tests described in this document are for i.MX93 EVK and i.MX93 QSB boards.

#### 1.2 Essential references

This guide is supplementary to the i.MX 93 series chip reference manuals and data sheets. For reflow profile and thermal limits during soldering, see General Soldering Temperature Process Guidelines (document AN3300).

#### 1.3 Supplementary references

#### 1.3.1 General information

The following documents introduce the Arm processor architecture:

- For information about the Arm Cortex-A55 processor, see <a href="https://www.arm.com/products/silicon-ip-cpu/cortex-a/cortex-a55">https://www.arm.com/products/silicon-ip-cpu/cortex-a/cortex-a55</a>

- For information about the Arm Cortex-M33 processor, see <a href="https://www.arm.com/products/processors/cortex-m/cortex-m33-processor.php">https://www.arm.com/products/processors/cortex-m33-processor.php</a>

For details of computer architecture refer to the following documents:

- Computer Architecture A Quantitative Approach (Fourth Edition) John L. Hennessy and David A. Patterson

- Computer Organization and Design The Hardware/Software Interface (Second Edition) David A. Patterson and John L. Hennessy

The following documents introduce the topic of high-speed board design:

- Right the First Time- A Practical Handbook on High Speed PCB and System Design Volumes I & II Lee W.

Ritchey (Speeding Edge) ISBN 0-9741936- 0-72

- Signal and Power Integrity Simplified (2nd Edition) Eric Bogatin (Prentice Hall)- ISBN 0-13-703502-0

- High Speed Digital Design- A Handbook of Black Magic Howard W. Johnson & Martin Graham (Prentice Hall) ISBN 0-13-395724-1

- High Speed Signal Propagation Advanced Black Magic Howard W. Johnson & Martin Graham (Prentice Hall) - ISBN 0-13-084408-X

- High Speed Digital System Design- A handbook of Interconnect Theory and Practice Hall, Hall and McCall (Wiley Interscience 2000) ISBN 0-36090-2

- Signal Integrity Issues and Printed Circuit Design Doug Brooks (Prentice Hall) ISBN 0-13-141884-X

- PCB Design for Real-World EMI Control Bruce R. Archambeault (Kluwer Academic Publishers Group) -ISBN 1-4020-7130-2

- Digital Design for Interference Specifications A Practical Handbook for EMI Suppression David L. Terrell & R. Kenneth Keenan (Newnes Publishing) - ISBN 0-7506-7282-X

IMX93HDG

All information provided in this document is subject to legal disclaimers.

- Electromagnetic Compatibility Engineering Henry Ott (1st Edition John Wiley and Sons) ISBN 0-471-85068-3

- Introduction to Electromagnetic Compatibility Clayton R. Paul (John Wiley and Sons) ISBN 978-0-470-18930-6

- Grounding & Shielding Techniques Ralph Morrison (5th Edition John Wiley & Sons) ISBN 0-471-24518-6

- EMC for Product Engineers Tim Williams (Newnes Publishing) ISBN 0-7506- 2466-3

#### 1.4 Related documentation

For the list of current documents, refer to i.MX93/Documentation.

Additional literature would be published as and when new NXP products become available.

- For thermal management guidelines, refer to AN4579.

- Refer to the 'CCM' chapter in the i.MX 93 Chip Reference Manual for details of clocks.

- For more information about general high-speed routing considerations, see *High-Frequency Design Considerations* (document AN12298).

#### 1.5 Conventions

Table 1 lists the notational conventions used in this document.

In this document, notation for all logical, bit-wise, arithmetic, comparison, and assignment operations follow C Language conventions.

Table 1. Conventions used in the document

| Conventions | Description                                                                                                                                                                                              |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Courier     | Used to indicate commands, command parameters, code examples, and file and directory names.                                                                                                              |

| Italics     | Used to indicate command or function parameters.                                                                                                                                                         |

| Bold        | Function names are written in bold.                                                                                                                                                                      |

| cleared/set | When a bit takes the value zero, it means to be cleared; when it takes a value of one, it means to be set.                                                                                               |

| mnemonics   | Instruction mnemonics are shown in lowercase bold. Book titles in text are set in italics.                                                                                                               |

| sig_name    | Internal signals are written in all lowercase.                                                                                                                                                           |

| nnnn nnnnh  | Denotes hexadecimal number                                                                                                                                                                               |

| 0b          | Denotes binary number                                                                                                                                                                                    |

| rA, rB      | Instruction syntax used to identify a source GPR                                                                                                                                                         |

| rD          | Instruction syntax used to identify a destination GPR                                                                                                                                                    |

| REG[FIELD]  | Abbreviations for registers are shown in uppercase. Specific bits, fields, or ranges appear in brackets. For example, MSR[LE] refers to the little-endian mode enable bit in the machine state register. |

| х           | An italicized x indicates an alphanumeric variable.                                                                                                                                                      |

| n, m        | An italicized n indicates a numeric variable.                                                                                                                                                            |

# 1.6 Acronyms and abbreviations

The table below defines the acronyms and abbreviations used in this document.

IMX93HDG

All information provided in this document is subject to legal disclaimers.

Table 2. Definitions and acronyms

| Acronym | Definition                                    |

|---------|-----------------------------------------------|

| Arm     | Advanced RISC Machines processor architecture |

| BGA     | Ball Grid Array package                       |

| ВОМ     | Bill of Materials                             |

| BSDL    | Boundary Scan Description Language            |

| BSP     | Board Support Package                         |

| CAN     | Flexible Controller Area Network peripheral   |

| ССМ     | Clock Controller Module                       |

| CSI     | MIPI Camera Serial Interface                  |

| DDR     | Dual Data Rate DRAM                           |

| DDR4    | DDR4 DRAM                                     |

| DDRC    | DDR Controller                                |

| DFP     | Downstream Facing Port (USB-Type C)           |

| DRP     | Dual Role Port (USB-Type C)                   |

| ECSPI   | Enhanced Configurable SPI peripheral          |

| EIM     | External Interface Module                     |

| EMI     | Electromagnetic interference                  |

| ENET    | 10/100/1000 Mbit/s Ethernet MAC peripheral    |

| EPIT    | Enhanced Periodic Interrupt Timer peripheral  |

| ESR     | Equivalent Series Resistance                  |

| GA      | General Availability                          |

| GND     | Ground                                        |

| GPC     | General Power Controller                      |

| GPIO    | General Purpose Input/Output                  |

| I2C     | Inter-Integrated Circuit interface            |

| IBIS    | Input output Buffer Information Specification |

| IOMUX   | i.MX 93 chip-level I/O multiplexing           |

| JTAG    | Joint Test Action Group                       |

| KPP     | Keypad Port Peripheral                        |

| LDB     | LVDS Display Bridge                           |

| LDO     | Low Drop-Out regulator                        |

| LPCG    | Low-Power Clock Gating                        |

| LPDDR4  | Low-Power DDR4 DRAM                           |

| LVDS    | Low-Voltage Differential Signaling            |

| ODT     | On-Die Termination                            |

| ОТР     | One-Time Programmable                         |

| РСВ     | Printed-circuit board                         |

Table 2. Definitions and acronyms...continued

| Acronym | Definition                                               |

|---------|----------------------------------------------------------|

| PCIe    | PCI Express                                              |

| PCISig  | Peripheral Component Interconnect Special Interest Group |

| PDN     | Power Distribution Network                               |

| PMIC    | Power Management Integrated Circuit                      |

| POR     | Power-on Reset                                           |

| PTH     | Plated Through Hole PCB (that is, no microvias)          |

| QSB     | Quick Start Board                                        |

| RGMII   | Reduced Gigabit Media Independent Interface (Ethernet)   |

| RMII    | Reduced Media Independent Interface (Ethernet)           |

| ROM     | Read-only Memory                                         |

| TDP     | Thermal Design Power                                     |

| TIM     | Thermal Interface Materials                              |

#### 1.7 Disclaimers

Nothing in this document relieves the design engineer/customer from ultimate responsibility in producing a proper functioning DRAM subsystem that meets JEDEC specifications. For compliance details, refer Section 3.7.

It is expected that the design engineer already has a strong understanding of PCB design using high-speed components. This is not an all-encompassing training document that can be used by beginning designers to produce reliable PCB designs using modern processors.

Design engineers should use all available design guidelines provided by the manufacturers of other high-speed components used in the system. Should a conflict arise between this document and the guidelines from other manufactures, contact NXP for resolution (<u>community.nxp.com</u>).

NXP strongly recommends that one of the example layouts provided for the i.MX9 designs be copied exactly for the placement of the processor, DRAM device, decoupling capacitors underneath the processor, and the interconnecting traces/vias between these parts. This includes the board stack-up design and PCB dielectric materials chosen. These designs have been tested and validated at NXP and they are proven reliable. While NXP does not expect every customer to copy our designs, customers must expect that the amount of support that can be provided for assisting a new design cannot be as great as the support provided for designs already known to NXP.

NXP provides the processor IBIS models and timing models necessary for performing complete DRAM simulations of a design. NXP strongly recommends that the end users perform simulations of any new designs before the release of a PCB layout design for manufacturing.

Processor Reference Manuals and User's Guides are continuously reviewed and revised to contain the most up-to-date information regarding the processor. In addition, Errata and Engineering bulletins may be issued to document unintended processor behavior. The design engineers should consult the official NXP website for the latest versions of these documents as a part of the final checks of a PCB design before releasing the board to manufacturing.

When a fully assembled board is returned to the design engineer, it is the engineer's responsibility to perform a complete check of the board design to ensure that all subsystems are functioning correctly. See Section 6 for recommended board bring-up guidelines.

# 2 i.MX 93 design checklist

This document provides a design checklist for the i.MX 93 processor. The design checklist tables recommend optimal design and provide explanations to help users understand better. All supplemental tables referenced by the checklist appear in sections following the design checklist tables.

# 2.1 Design checklist tables

Table 3. LPDDR4/4X recommendations

| S.No | Recommendations                                                                                                           | Explanation/Supplemental recommendations                                                                      | Checkbox |

|------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------|

| 1    | Connect the DRAM_ZQ ball on the processor to a 120 $\Omega$ , 1% resistor to GND.                                         | This is a reference used during DRAM output buffer driver calibration.                                        |          |

| 2    | The ZQ0 ball on the LPDDR4/4X device should be connected through a 240 $\Omega$ , 1% resistor to the LPDDR4/4X VDDQ rail. | _                                                                                                             |          |

| 3    | Place a 10 k $\Omega$ , 5% resistor to ground on the DRAM reset signal.                                                   | This ensures adherence to the JEDEC specification until the control is configured and starts driving the DDR. |          |

| 4    | The ODT_CA balls on the LPDDR4/4X device should be connected directly to the LPDDR4/4X VDD2 rail.                         | LPDDR4/4X ODT on the i.MX 93 is command-based, making processor ODT_CA output balls unnecessary.              |          |

| 5    | The architecture for each chip inside the DRAM package must be x16.                                                       | The processor does not support byte mode specified in JESD209-4B.                                             |          |

| 6    | The processor ball DRAM_MTEST1 should be left unconnected.                                                                | These are observability ports for manufacturing and are not used otherwise.                                   |          |

| 7    | Ensure that VDDQ_DDR/VDD2_DDR power up ramp rate is less than 24 V/ms.                                                    | Too fast ramp rate on VDDQ_DDR/VDD2_DDR might trigger the ESD protection circuit.                             |          |

Table 4. I2C recommendations

| S.No | Recommendations                                                                                                                                        | Explanation/Supplemental recommendations                                                                                                                                                                  | Checkbox |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1    | Verify the target I2C interface clock rates.                                                                                                           | The I2C bus can only be operated as fast as the slowest peripheral on the bus. If faster operation is required, move the slow devices to another I2C port.                                                |          |

| 2    | Verify that there are no I2C address conflicts on any of the I2C buses utilized.                                                                       | There are multiple I2C ports available on chip, so if a conflict exists, move one of the conflicting devices to a different I2C bus. If it is impossible, use a I2C bus switch (NXP part number PCA9646). |          |

| 3    | Do not place more than one set of pullup resistors on the I2C lines.                                                                                   | This could result in excessive loading and potential incorrect operation. Choose the pullup value commensurate with the bus speed being used.                                                             |          |

| 4    | Ensure that the VCC rail powering the i.MX 93 I2C interface balls matches the supply voltage used for the pull-up resistors and the slave I2C devices. |                                                                                                                                                                                                           |          |

#### Table 5. JTAG recommendations

| S.No | Recommendations                                                                                    | Explanation/Supplemental recommendations                                                                        | Checkbox |

|------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------|

| 1    | Do not use external pull-up or pull-down resistors on JTAG_TDO.                                    | JTAG_TDO is configured with an on-<br>chip keeper circuit and the floating<br>condition is actively eliminated. |          |

| 2    | Follow the recommendations for external pull-up and pull-down resistors given in <u>Table 12</u> . | _                                                                                                               |          |

#### Table 6. Reset and ON/OFF recommendations

| S.No | Recommendations                                                                                                                                                                                                              | Explanation/Supplemental recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Checkbox |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

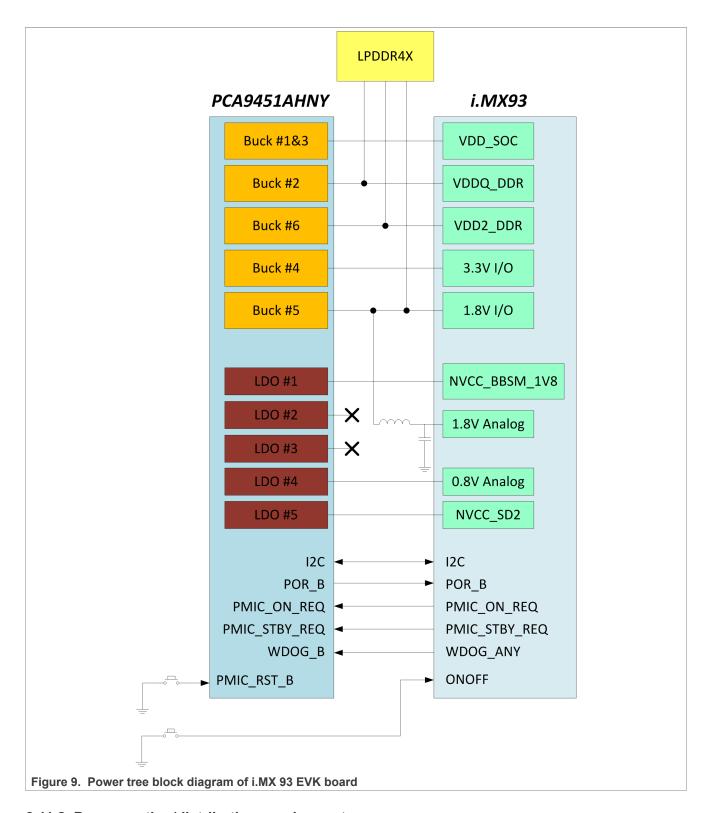

| 1    | The POR_B input must be asserted at power up and remain asserted until the last power rail for devices required for system boot is at its working voltage. The PMIC (PCA9451AHNY) on i.MX93 EVK controls this functionality. | The PMIC drives POR_B. If a reset button is used, connect it to the PMIC_RST_B pin of the PMIC instead of directly connecting it to POR_B pin of the CPU. This connection ensures that all the peripheral devices are reset along with i.MX93.  *Note: When POR_B on the i.MX 93 is asserted (low), then, the output PMIC_ON_REQ remains asserted (high). Therefore only toggling POR_B does not reset the peripheral devices. Only toggling POR_B might cause the system to fail to reboot after resetting. |          |

| 2    | For portable applications, the ONOFF pin may be connected to an ON/OFF SPST push-button switch to ground. An external pull-up resistor is required on this pin.                                                              | A brief connection to GND in OFF mode causes the internal power management state machine to change state to ON. In ON mode, a brief connection to GND generates an interrupt (intended to initiate a software-controllable power- down). The connection to GND for approximate 5 seconds or more causes a forced OFF.                                                                                                                                                                                        |          |

| 3    | In order to repower the system (except SNVS), users must connect WDOG_ANY ball to external PMIC or reset IC.                                                                                                                 | In Idle mode, internal reset source cannot reset i.MX93. In such a case, the processor should be repowered. Some peripherals such as SD3.0 and QSPI should also be repowered during system reset.                                                                                                                                                                                                                                                                                                            |          |

| 4    | WDOG_ANY ball is used as Cold Reset. If a PMIC other than PCA9451 is used, an external pull-up resistor (100 K $\Omega$ ) is required to support boundary-scan mode.                                                         | In Boundary-scan mode, WDOG_ANY is left floating. Without the external 100 K $\Omega$ pull-up, WDOG_ANY might repeatedly reset the system when entering Boundary-scan mode. The PCA9451 disables WDOG_ANY reset by default, so it is not impacted.                                                                                                                                                                                                                                                           |          |

| 5    | While using a low power design, the wake up source should be on the I/Os within the NVCC_AON domain.                                                                                                                         | The I/Os within the NVCC_AON domain are associated with M33 core, which is supposed to be used in low power design.                                                                                                                                                                                                                                                                                                                                                                                          |          |

# Table 7. USB recommendations

| Checkbo | Recommendations                                                              | Explanation/Supplemental recommendations | Checkbox |

|---------|------------------------------------------------------------------------------|------------------------------------------|----------|

|         | Connect a 200 $\Omega$ , 1% resistor to the ground on the USBx_TXRTUNE ball. | _                                        |          |

|         | Route all USB differential signals with 90 $\Omega$ differential impedance.  |                                          |          |

IMX93HDG

All information provided in this document is subject to legal disclaimers.

Table 7. USB recommendations...continued

| Checkbo | Recommendations                                                                                                                                                                                | Explanation/Supplemental recommendations                      | Checkbox |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------|

| 3       | ESD protection should be implemented at the connector pins. Choose a low capacitance device recommended for high-speed interfaces.                                                             | This prevents potential damages to board components from ESD. |          |

| 4       | If USB connectors MicroAB or MicroB are used, USBx_VBUS must not connect directly to the 5 V VBUS voltage of connector. Instead, this pin must be isolated using an external 30 K 1% resistor. |                                                               |          |

# Table 8. Oscillator/Crystal recommendations

| S.No | Recommendations                                                                                                                                                                                           | Explanation/Supplemental recommendations                                                                                                                                                                                                                                                                                                                                                                         | Checkbox |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1    | Connect a 24 MHz crystal between XTALI _24M and XTALO_24M balls.                                                                                                                                          | <ul> <li>This crystal should have ESR not greater than 60 Ω, and be rated for a drive level of at least 100 μW.</li> <li>Follow the manufacturer's recommendation for loading capacitance.</li> <li>Use short traces between the crystal and the processor, with a ground plane under the crystal, load capacitors, and associated traces.</li> </ul>                                                            |          |

| 2    | Connect a 32.768 kHz between RTC_XTALI and RTC_XTALO balls. Alternatively, an external 32.768 kHz clock can be fed into RTC_XTALI to provide the RTC clock for the i.MX 93. See item #3.                  | <ul> <li>This crystal should have ESR not greater than 70 kΩ, and be rated for a drive level of at least 0.5 μW.</li> <li>Follow the manufacturer's recommendation for loading capacitance.</li> <li>Use short traces between the crystal and the processor, with a ground plane under the crystal, load capacitors, and associated traces.</li> </ul>                                                           |          |

| 3    | If using external 32.768 kHz clock rather than a crystal to provide the RTC clock, it should be connected to RTC_XTALI pin. The RTC_XTALO pin must remain unconnected or driven by a complementary signal | The voltage level of this driving clock should not exceed the voltage of the NVCC_BBSM_1P8 rail, or damage/malfunction might occur. The RTC signal should not be driven if the NVCC_BBSM_1P8 supply is OFF. For RTC V <sub>IL</sub> and V <sub>IH</sub> voltage levels, see the latest i.MX 93 data sheet available at <a href="https://www.nxp.com/i.MX93/Documentation">www.nxp.com/i.MX93/Documentation</a> . |          |

# Table 9. i.MX 93 power/decoupling recommendations

| S.No | Recommendations                                                                                                             | Explanation/Supplemental recommendations                                                                                                                                                                      | Checkbox |

|------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1    | Comply with the power-up sequence guidelines as described in the data sheet to guarantee reliable operations of the device. | Any deviation from these sequences may result in the following situations:  Excessive current during power-up phase  Prevention of the device from booting  Irreversible damage to the processor (worst case) |          |

| 2    | Maximum ripple voltage requirements                                                                                         | Common requirement for ripple noise peak-to-<br>peak value should be less than 5% of the supply<br>voltage nominal value.                                                                                     |          |

| 3    | If PCA9451AHNY PMIC is used to provide power, ensure that the output L/C components                                         | Leaving any regulator output open will lead to malfunction of the whole PMIC.                                                                                                                                 |          |

IMX93HDG

All information provided in this document is subject to legal disclaimers.

Table 9. i.MX 93 power/decoupling recommendations...continued

| S.No | Recommendations                                           | Explanation/Supplemental recommendations                                                                                                                                                                                       | Checkbox |

|------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | of all regulators are properly connected, even if unused. |                                                                                                                                                                                                                                |          |

| 4    | switcher inductor current ratings are sufficient          | When using a non-NXP PMIC, or scaling down a power rail, ensure that the PMIC and inductor meet the maximum current demands of the system.  Note: Currents will be higher at hotter SoC temperatures than at room temperature. |          |

Table 10. Decoupling capacitors recommendations

| S.No | Supply                                                                                                         | 0.22 μF | 1 μF | 10 μF | Notes                                                                                                                                                   | Checkbox |

|------|----------------------------------------------------------------------------------------------------------------|---------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1    | VDD_SOC                                                                                                        | _       | 6    | 2     |                                                                                                                                                         |          |

| 2    | VDD2_DDR                                                                                                       | _       | 6    | 1     | _                                                                                                                                                       |          |

| 3    | VDDQ_DDR                                                                                                       | _       | 2    | 1     | _                                                                                                                                                       |          |

| 4    | VDD_BBSM_0P8_CAP                                                                                               | 1       | _    | _     | _                                                                                                                                                       |          |

| 5    | NVCC_BBSM_1P8                                                                                                  | _       | 1    | _     | _                                                                                                                                                       |          |

| 6    | VDD_ANA0_1P8, VDD_ANA1_1 P8, VDD_ANADET_1P8, VDD_ LVDS_1P8, VDD_MIPI_1P8, VDD_USB_1P8                          | _       | 6    | _     | These 6 power rails are combined on EVK, and are then combined with NVCC_WAKEUP through a filter consisting of a ferrite bead and 2 x 22 µF capacitors. |          |

| 7    | VDD_USB_0P8, VDD_<br>MIPI_0P8, VDD_ANA_0P8                                                                     | _       | 5    | _     | These 3 power rails are combined on EVK.                                                                                                                |          |

| 8    | NVCC_WAKEUP                                                                                                    | _       | 2    | _     | _                                                                                                                                                       |          |

| 9    | NVCC_AON                                                                                                       | _       | 1    | _     | _                                                                                                                                                       |          |

| 10   | NVCC_GPIO                                                                                                      | _       | 1    | _     | _                                                                                                                                                       |          |

| 11   | NVCC_SD2                                                                                                       | _       | 1    | _     | _                                                                                                                                                       |          |

| 12   | VDD_USB_3P3                                                                                                    | _       | 1    | _     | _                                                                                                                                                       |          |

|      | Capacitor part number used on EVK:  • 0.22 μF LMK063BJ224MP-F  • 1 μF CL03A105KP3NSNC  • 10 μF CL05A106MQ5NUNC |         |      |       |                                                                                                                                                         |          |

Table 11. PCB design recommendations

| S.No | Recommendations                                                                               | Explanation/Supplemental recommendations                                                                                                                                               | Checkbox |

|------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1    | High-speed signal traces have reference plane in adjacent layer and are impedance-controlled. | Controlled impedance is the key factor to have good signal integrity. Note that the reference plane can only be GND or the signal's own I/O power. Do not use other nets as reference. |          |

| 2    | High-speed signal traces never cross gap or slot in reference plane.                          | Crossing gap in reference plane will cause reflection and increase crosstalk.                                                                                                          |          |

IMX93HDG

All information provided in this document is subject to legal disclaimers.

Table 11. PCB design recommendations...continued

| S.No | Recommendations                                                                                                                                                                                                                               | Explanation/Supplemental recommendations                                                                                                                                                                                  | Checkbox |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3    | Place at least one GND stitching via within 50 mils of signal via when switching reference planes.                                                                                                                                            | GND stitching via can help keep impedance continuous and reduce via crosstalk.                                                                                                                                            |          |

| 4    | Appropriate delay matching is done for parallel bus.                                                                                                                                                                                          | Signals within a bus should have delay time matched to maintain timing margin.                                                                                                                                            |          |

| 5    | The true and complementary signal of a differential pair must have delay matched to within 1 ps.                                                                                                                                              | The true and complementary signal within a differential pair should have delay time tightly matched.                                                                                                                      |          |

| 6    | DDR interface passed Si simulation. Alternatively, directly copy the EVK DDR layout design.                                                                                                                                                   | Generally, Si simulation should be performed for DDR interface that runs at 3733 MT/s to ensure stable working. If this is not feasible, just copy the EVK DDR layout design as well as the board stack-up and materials. |          |

| 7    | Place test point on key signals to ease debugging. While placing test points on high-speed signal traces, ensure that the diameter of the test point is no more than 20 mil. Test points should be directly placed on the trace with no stub. | and should be carefully handled on high-speed signal traces.                                                                                                                                                              |          |

| 8    | Decoupling capacitors are placed as close to IC power pins as possible.                                                                                                                                                                       | This strategy reduces the inductance from decoupling capacitor to IC power pin. Therefore such placement improves decoupling effectiveness.                                                                               |          |

# 2.2 JTAG signal termination

Below is a JTAG termination chart showing the terminations that should be placed on PCB designs.

Table 12. Recommended JTAG board terminations

| JTAG signal | I/O type       | External termination | Comments                                                           |

|-------------|----------------|----------------------|--------------------------------------------------------------------|

| JTAG_TCK    | Input          | None                 | Internal pull down, no external termination required.              |

| JTAG_TMS    | Input          | None                 | Internal pull up to NVCC_WAKEUP, no external termination required. |

| JTAG_TDI    | Input          | None                 | Internal pull up to NVCC_WAKEUP, no external termination required. |

| JTAG_TDO    | 3-state output | None                 | _                                                                  |

#### 2.3 General recommendations

More than one software operating environment can run on the i.MX 93 platforms concurrently. Peripherals on these SoCs are accessible to all software operating environments. A conflict can occur when more than one software operating environment reads or writes the state of the same peripheral.

Therefore, software operating environments must be isolated from each other when accessing shared resources. For instance, if two operating environments read and write the same region of DRAM without coordinating their access, results are unpredictable. The same behavior is applicable for peripheral registers, especially for the IP modules which offer multiple logical channels. For example, GPIO, I2C, SPI, SAI, and DMA.

Therefore, any sharing of an IP module between Cortex-M and Cortex-A domains must be coordinated with the system software architecture because software operating environments must be isolated from each other when accessing shared resources in order to avoid safety/reliability issues.

Consider an example. Individual GPIO pins are aggregated into groups, each group is controlled by a single GPIO module. Each GPIO module is a distinct peripheral that must be protected from conflicting access by different software operating environments. For example, GPIO1 module is assigned as a shared peripheral for Linux on the Arm Cortex-A and RTOS on the Cortex-M. Cortex-A and Cortex-M should obtain a semaphore lock before access to any pin of GPIO1 module is allowed. If Cortex-A and Cortex-M attempt to access to GPIO1 module at the same time, it can result in lack of isolation leading to safety/reliability issues.

#### Note:

Resource allocation should assure that peripherals have external signals pinned out and their IO resources can be synchronously controlled either by Cortex-A or Cortex-M in the corresponding software operating environment.

Not allocating correctly can result in lack of isolation leading to safety/reliability issues that can only be overcome using complex software such as virtual drivers. Use of such software can indirectly affect the hardware isolation of software domains and the peripheral performance. In this case, customer needs to implement customized software solutions such as RPMSG Client/server-style cooperative device drivers or Peripheral Exclusive Access using a Mutex solution implemented using SEMA42. Implementation on the i.MX 93 is up to the Software Architecture chosen by customer.

Under those circumstances, the Peripheral Modules should be allocated to Software Systems per module basis and not a per signal basis from board design phase.

# 3 i.MX 93 layout/routing recommendations

#### 3.1 Introduction

This chapter describes how to assist design engineers with the layout of an i.MX 93-based system.

# 3.2 Basic design recommendations

When using the Allegro design tool, the schematic symbol and PCB footprint created by NXP is recommended. When not using the Allegro tool, use the Allegro footprint export feature (supported by many tools). If the export is not possible, create the footprint per the package dimensions outlined in the product data sheet.

**Note:** Native Allegro layout and gerber files would be made available on <a href="https://www.nxp.com/imx93evk/DesignTools">www.nxp.com/imx93evk/DesignTools</a> & Files.

# 3.3 Placing decoupling capacitors

Place small decoupling and larger bulk capacitors on the bottom side of the PCB.

The 0201 or 0402 decoupling and 0603 or larger bulk capacitors should be mounted as close as possible to the power vias. The distance should be less than 50 mils. Additional bulk capacitors can be placed near the edge of the BGA via array. Placing the decoupling capacitors close to the power balls is critical to minimize inductance and ensure high-speed transient current required by the processor. See the i.MX 93 EVK layouts for the recommended decoupling capacitor placement.

The following list describes how to choose correct decoupling scheme:

- Place the largest capacitance in the smallest package that budget and manufacturing can support.

- For high-speed bypassing, select the required capacitance with the smallest package (for example, 1.0  $\mu$ F, or even 2.2  $\mu$ F in a 0201 package size).

- Minimize trace length (inductance) to small caps.

- · Series inductance cancels out capacitance.

- · Tie caps to GND plane directly with a via.

- Place capacitors close to the power ball of the associated package from the schematic.

- A preferred BGA power decoupling design is available on the EVK board design available on <a href="www.nxp.com/">www.nxp.com/</a>

imx93evk. Customers should use the NXP design strategy for power and decoupling.

# 3.4 Stack-up and manufacturing recommendations

#### 3.4.1 Stack-up recommendation

Due to the number of balls on the i.MX 93 processor in the package, a minimum 6-layer PCB stack-up is recommended. For the smaller 9 mm x 9 mm package, a minimum 4-layer PCB stack-up can be achieved. For either the 6-layer or 4-layer stack-up, at least one layer should be dedicated to power on routing to meet the IR drop target of 2% for the i.MX 93 CPU power rails.

The constraints for the trace width depend on such factors as the board stack-up, the associated dielectric and copper thickness, required impedance, and required current (for power traces). The stack-up also determines the constraints for routing and spacing. Consider the following requirements when designing the stack-up and selecting board material:

- Board stack-up is critical for high-speed signal quality.

- · Pre-planning impedance of critical traces is required.

- · High-speed signals must have reference planes on adjacent layers.

IMX93HD0

All information provided in this document is subject to legal disclaimers.

• PCB material: the material used on EVK is 185HR.

#### 3.4.2 Manufacturing recommendation

Since the i.MX 93 processor uses 0.5 mm-pitch BGA package, the PCB technology must meet below requirement to fully fanout all the signals of the processor using PTH (plated through holes).

- Minimum trace width: 3.2 mil

- · Minimum trace to trace/pad spacing: 3.2 mil

- · Minimum via size: 8 mil diameter hole, 16 mil diameter pad

- Minimum via pad-to-pad spacing: 4 mil

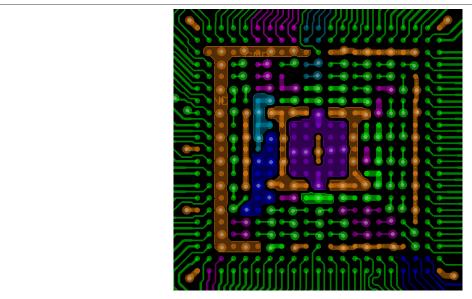

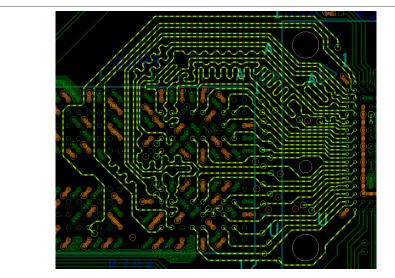

The figure below shows the reference routing of the i.MX 93, PTH is OK for the fanout, HDI is not needed.

Figure 1. i.MX 93 fanout routing on EVK

# 3.5 PCB stack-up examples

The following sections show examples for stack-up of the i.MX93 EVK and i.MX93 QSB boards.

#### 3.5.1 EVK PCB stack-up

The tables below show stack-up of the MCIMX93 EVK. The CPU board uses 6-layer stack-up and the BB board uses 8-layer stack-up.

Table 13. MCIMX93-SOM Board stack up information

| Layer | Description | Copper (Oz.) | Generic       | Er   | Dielectric<br>thickness (mil) |

|-------|-------------|--------------|---------------|------|-------------------------------|

| 1     | Signal      | 0.5+Plating  |               |      |                               |

|       | Dielectric  |              | PP1080        | 3.67 | 2.8 mil                       |

| 2     | GND         | 1            |               |      |                               |

|       | Dielectric  |              | Core 0.076 mm | 3.86 | 3 mil                         |

| 3     | Signal      | 1            |               |      |                               |

IMX93HDG

All information provided in this document is subject to legal disclaimers

Table 13. MCIMX93-SOM Board stack up information...continued

| Layer     | Description | Copper (Oz.)        | Generic                               | Er   | Dielectric thickness (mil) |

|-----------|-------------|---------------------|---------------------------------------|------|----------------------------|

|           | Dielectric  |                     | PP 1080*2<br>Core 0.8 mm<br>PP 1080*2 | 3.67 | 41.082 mil                 |

| 4         | Power       | 1                   |                                       |      |                            |

|           | Dielectric  |                     | Core 0.076 mm                         | 3.86 | 3 mil                      |

| 5         | GND         | 1                   |                                       |      |                            |

|           | Dielectric  |                     | PP 1080                               | 3.67 | 2.8 mil                    |

| 6         | Signal      | 0.5+Plating         |                                       |      |                            |

| Finished: | 62          | 2.992(6.299/-6.299) | mil 1.6(+0.16/-0.16) mm               |      | /-0.16) mm                 |

| Designed: |             | 58.268 mil          |                                       | 1.48 | 3 mm                       |

| Material: | 185HR       |                     |                                       |      |                            |

Table 14. MCIMX93-BB Board stack up information

| Layer     | Description         | Copper (Oz.)            | Generic        | Er   | Dielectric<br>thickness (mil) |  |

|-----------|---------------------|-------------------------|----------------|------|-------------------------------|--|

| 1         | Signal              | 0.5+Plating             |                |      |                               |  |

|           | Dielectric          |                         | 1080           | 3.85 | 2.646 mil                     |  |

| 2         | GND                 | 1                       |                |      |                               |  |

|           | Dielectric          |                         | Core 0.13 mm   | 4.2  | 5.12 mil                      |  |

| 3         | Signal              | 1                       |                |      |                               |  |

|           | Dielectric          |                         | 1080*2<br>2116 | 3.95 | 9.674 mil                     |  |

| 4         | Power               | 1                       |                |      |                               |  |

|           | Dielectric          |                         | Core 0.8 mm    | 4.47 | 31.5 mil                      |  |

| 5         | Power               | 1                       |                |      |                               |  |

|           | Dielectric          |                         | 1080*2<br>2116 | 3.95 | 9.638 mil                     |  |

| 6         | Signal              | 1                       |                |      |                               |  |

|           | Dielectric          |                         | Core 0.13 mm   | 4.2  | 5.12 mil                      |  |

| 7         | GND                 | 1                       |                |      |                               |  |

|           | Dielectric          |                         | 1080           | 3.85 | 2.646 mil                     |  |

| 8         | Signal              | 0.5+Plating             |                |      |                               |  |

| Finished: | 78.74(7.874/-7.874) | 78.74(7.874/-7.874) mil |                |      | 2(+0.2/-0.2) mm               |  |

| Designed: | 75.236 mil          | 75.236 mil              |                |      | 911 mm                        |  |

| Material: | TU768               |                         | I              |      |                               |  |

#### 3.5.2 QSB PCB stack-up

The tables below shows stack-up of the Quick Start Board (QSB). It is based on i.MX93 9x9 package and a 4-layer stack-up is used.

Table 15. MCIMX93-QSB Board stack up information

| Layer     | Description      | Copper (Oz.)              | Generic    | Er   | Dielectric thickness (mil) |  |

|-----------|------------------|---------------------------|------------|------|----------------------------|--|

| 1         | Signal           | 0.5+Plating               |            |      |                            |  |

|           | Dielectric       |                           | 106H       | 3.52 | 2.072                      |  |

| 2         | GND              | 1                         |            |      |                            |  |

|           | Dielectric       |                           | Core 1.4MM | 3.76 | 55.12                      |  |

| 3         | Power            | 1                         |            |      |                            |  |

|           | Dielectric       |                           | 106H       | 3.52 | 2.072                      |  |

| 4         | Signal           | 0.5+Plating               |            |      |                            |  |

| Finished: | 62.992 (6.299/-6 | 62.992 (6.299/-6.299) mil |            |      | 1.6 (+0.16/-0.16) MM       |  |

| Designed: | 63 mil           | 63 mil                    |            |      |                            |  |

| Material: | 185HR            | 85HR                      |            |      |                            |  |

# 3.6 DDR design recommendations

#### 3.6.1 LPDDR4/4X-3733 design recommendations

The following list provides some generic guidelines that should be adhered to when implementing an i.MX 93 design using LPDDR4/4X.

- 1. It is expected that the layout engineer and design team already has experience and training with DDR designs at speeds of 1.867 GHz / 3733 MT/s.

- 2. Use solid GND planes as reference planes for all the high-speed signal traces. The only exception that is allowed is CKE and DQS signal, for which power plane can be used as reference plane in the case of a 4-layer board design of i.MX93 9X9 package.

- **Note:** Users must ensure that there is no discontinuity or slot on the reference plane underneath the traces.

- 3. Keep edge to edge spacing of high-speed signal traces no less than 2 times the trace width to minimize trace crosstalk. Widen edge-to-edge spacing to 3x-4x where space is available in order to further minimize crosstalk.

- 4. At a speed of 3733 MT/s, signal vias can be a significant source of crosstalk. Improper design of signal vias can introduce crosstalk larger than that from the trace. To minimize via crosstalk follow the below:

- a. Make sure that the total number of vias is no more than two on each point-to-point single-ended/differential trace.

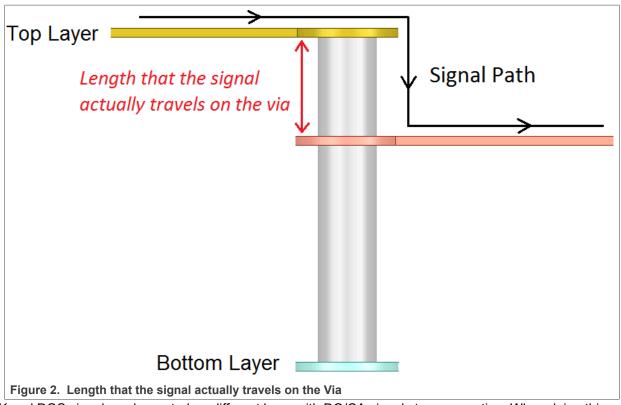

- b. Place at least one ground stitching via within 50 mils of signal via when switching reference planes to provide continuous return path and reduce crosstalk. If it is not possible to place enough ground stitching vias due to space limitation, try to make the length that the signal actually travels on the via as short as possible, as illustrated in <a href="Figure 2">Figure 2</a>. The i.MX 93 is optimized to use layer 1 and layer 3 for all single-ended traces. The differential traces, CLK, DQS0,1 are often routed on the bottom layer. These require the stitching GND vias. The EVK reference design demonstrates this method.

- 5. CLK and DQS signal can be routed on different layer with DQ/CA signals to ease routing. When doing this, keep no less than 5 times trace width spacing from other signals.

- 6. Use time delay instead of length when performing the delay matching. The delay matching includes the PCB trace delay and the IC package delay. Incorporate the package pin delay into the CAD tool's constraint manager.

- 7. Include the delay of vias when performing delay matching. This can be realized in Allegro tool by enabling the Z Axis Delay in "Setup -> Constraints -> Modes".

- 8. Bit swapping within each slice/byte lane is OK. Byte swapping is NOT allowed.

- 9. Bit swapping of Command/Address (CA[5:0]) pins is NOT allowed.

- 10. i.MX 93 does not drive *ODT\_CA* signals. The *ODT\_CA* balls on the LPDDR4/4X devices should be connected directly or through a resistor to the VDD2 supply.

- 11. In general, the 200-ball LPDDR4/4X package should be placed ~200 mils from the i.MX 93.

- 12. Make sure to enable the DBI (data bus inversion) feature. This reduces power consumption and noise.

#### 3.6.2 i.MX 93 LPDDR4/4X-3733 routing recommendations

LPDDR4/4X-3733 needs to be routed with signal fly times matched shown in <u>Table 16</u>. The delay of the via transitions needs to be included in the overall calculation. This can be realized in Allegro tool by enabling the Z Axis Delay in "Setup - Constraints - Modes".

An example of the delay match calculation has been shown for the i.MX 93 EVK board design in <u>Table 17</u> and <u>Table 18</u>. This analysis was done for the LPDDR4/4X-3733 implementation using the i.MX 93. In <u>Table 17</u> and <u>Table 18</u>, the PCB Delay column is obtained directly from the Allegro PCB file. The Pkg Delay column is the package delay obtained from <u>Section 3.6.6</u>.

NXP strongly recommends that users simulate their LPDDR4/4X implementation before fabricating PCBs.

Table 16. i.MX 93 LPDDR4/4X-3733 routing recommendations

| LPDDR4/4X-3733          |                  |                   |              |                                                |

|-------------------------|------------------|-------------------|--------------|------------------------------------------------|

| LPDDR4/4X signal        | Group            | PCB+ package pro  | p delay      |                                                |

|                         |                  | Min               | Max          | Considerations                                 |

| CK_T/CK_C               | Clock            | Short as possible | 200 ps       | Match the true/complement signals within 1 ps. |

| CS1, CS0                |                  | CK_t - 1 ps       | CK_t+ 1 ps   | -                                              |

| CA5, CA4, CA3, CA2      | Address/Command/ | CK_t - 50 ps      | CK_t + 50 ps | Match CA5, CA4, CA3, CA2 within 2 ps           |

| CA1, CA0, CKE1,<br>CKE0 |                  |                   |              | Match CA1, CA0, CKE1,<br>CKE0 within 2 ps      |

| DQS0_T/DQS0_C           | Byte0 - DQS      | CK_t- 125 ps      | CK_t+ 75 ps  |                                                |

| DMI0                    | Pyto0 Data       | DOS0 + 50 pg      | DOS0 ++50 po |                                                |

| DQ[7:0]                 | - Byte0 - Data   | DQS0_t-50 ps      | DQS0_t+50 ps | Match the true/complement                      |

| DQS1_T/DQS1_C           | Byte1 - DQS      | CK_t- 125 ps      | CK_t+ 75 ps  | signals of DQS within 1 ps.                    |

| DMI1                    | Pyto1 Data       | DOS1 + 50 pc      | DOS1 t+50 pc |                                                |

| DQ[15:8]                | Byte1 - Data     | DQS1_t-50 ps      | DQS1_t+50 ps |                                                |

Table 17. LPDDR4/4X delay matching example (CA/CTL signals)

| Net Name    | PCB Delay (ps) | Pkg Delay (ps) | Total Net Delay = (PCB + Pkg) Delay | Comments             |

|-------------|----------------|----------------|-------------------------------------|----------------------|

| DRAM_CK_T_A | 163.9          | 40             | 203.9                               | Vias are L1-> L6->L1 |

| DRAM_CK_C_A | 164.3          | 40.2           | 204.5                               | Vias are L1-> L6->L1 |

| DRAM_CA0_A  | 125            | 36.4           | 161.4                               | Vias are L1-> L3->L1 |

| DRAM_CA1_A  | 118.2          | 42.7           | 160.9                               | Vias are L1-> L3->L1 |

| DRAM_CA2_A  | 201.4          | 35.8           | 237.2                               | Vias are L1-> L3->L1 |

| DRAM_CA3_A  | 193.9          | 43.5           | 237.4                               | Vias are L1-> L3->L1 |

| DRAM_CA4_A  | 197.8          | 39             | 236.8                               | Vias are L1-> L3->L1 |

| DRAM_CA5_A  | 190.6          | 45.8           | 236.4                               | Vias are L1-> L3->L1 |

| DRAM_nCS0_A | 164.3          | 39             | 203.3                               | Vias are L1-> L3->L1 |

| DRAM_nCS1_A | 166            | 37.8           | 203.8                               | Vias are L1-> L3->L1 |

| DRAM_CKE0_A | 124            | 37.2           | 161.2                               | Vias are L1-> L3->L1 |

| DRAM_CKE1_A | 129.1          | 33             | 162.1                               | Vias are L1-> L3->L1 |

Table 18. LPDDR4/4X delay matching example (byte lane 1 signals)

| Table for all partir for a | olay illatolillig ox | ampio (b) to lane | · oigilalo/                            |                             |

|----------------------------|----------------------|-------------------|----------------------------------------|-----------------------------|

| Net Name                   | PCB Delay (ps)       | Pkg Delay (ps)    | Total Net Delay =<br>(PCB + Pkg) Delay | Comments                    |

| DRAM_SDQS1_T_A             | 90.2                 | 20.9              | 111.1                                  | Vias are L1-> L6->L1        |

| DRAM_SDQS1_C_A             | 90.8                 | 20.7              | 111.5                                  | Vias are L1-> L6->L1        |

| DRAM_DMI1_A                | 47.7                 | 29.2              | 76.9                                   | Routed on top layer, no via |

| DRAM_DQ8_A                 | 60                   | 35.9              | 95.9                                   | Routed on top layer, no via |

| Net Name    | PCB Delay (ps) | Pkg Delay (ps) | Total Net Delay = | Comments                    |

|-------------|----------------|----------------|-------------------|-----------------------------|

|             | , ,            | 3 - 7 (1-7)    | (PCB + Pkg) Delay |                             |

| DRAM_DQ9_A  | 70.1           | 33.9           | 104               | Routed on top layer, no via |

| DRAM_DQ10_A | 54.5           | 30.9           | 85.4              | Routed on top layer, no via |

| DRAM_DQ11_A | 41.8           | 33.7           | 75.5              | Routed on top layer, no via |

| DRAM_DQ12_A | 42.3           | 32             | 74.3              | Routed on top layer, no via |

| DRAM_DQ13_A | 43.7           | 29.4           | 73.1              | Routed on top layer, no via |

| DRAM_DQ14_A | 59.3           | 27.4           | 86.7              | Routed on top layer, no via |

| DRAM_DQ15_A | 60.1           | 33.6           | 93.7              | Routed on top layer, no via |

Table 18. LPDDR4/4X delay matching example (byte lane 1 signals)...continued

# 3.6.3 LPDDR4/4X-3733 routing example (11x11 and 14x14 package)

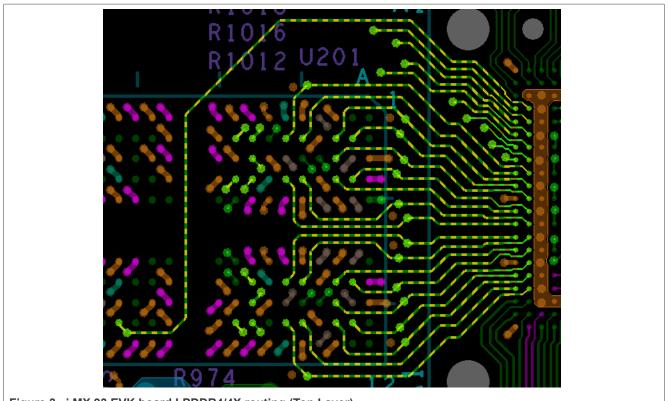

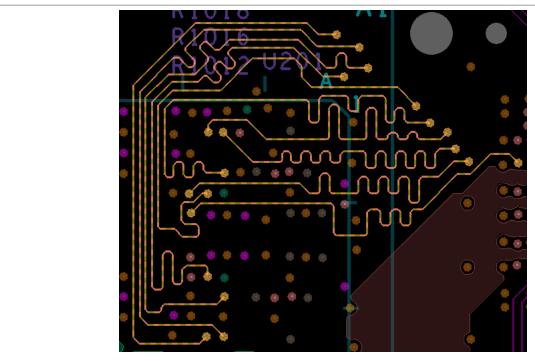

The figure 3, Figure 4, and Figure 5 below show the placement and routing of the LPDDR4/4X signals on the i.MX 93 EVK board (MCIMX93-EVK board), based on 11x11 package. The 14x14 package uses the same ball assignment as 11x11 package, so the routing is very similar to that shown here.

The CLK and DQS signals are routed on bottom layer to save routing space on top layer and layer 3. DQ and DMI signals are routed on top layer, and CA/CTL signals are routed on layer 3. This is to minimize the distance the signal actually travels on the via to minimize via crosstalk.

Figure 3. i.MX 93 EVK board LPDDR4/4X routing (Top Layer)

Figure 4. i.MX 93 EVK board LPDDR4/4X routing (Layer 3)

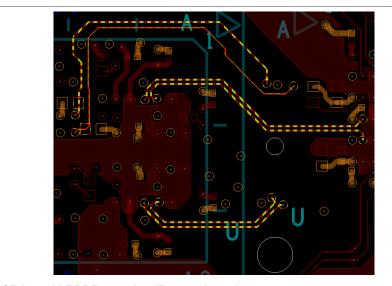

# 3.6.4 LPDDR4-3733 routing example (9x9 package)

The figures 6 and Figure 7 below show the placement and routing of the LPDDR4 signals on the i.MX 93 Quick Start Board (MCIMX93-QSB) which is based on 9x9 package. Taking advantage of the less number of I/Os on the 9x9 package, a 4-layer board design is realized. For a 4-layer board, only the signals routed on top layer will have a solid GND reference plane, so almost all the signals are routed on top layer except CKE whose toggle-

rate is very low and differential signals DQS which are not as sensitive to non-ideal reference plane as singleended signals. The CKE and DQS signals are routed on bottom layer with power plane as reference plane. Note that there shall not be any discontinuity/slot on the reference plane underneath the traces.

Figure 6. i.MX 93 QSB board LPDDR4 routing (Top Layer)

Figure 7. i.MX 93 QSB board LPDDR4 routing (Bottom Layer)

# 3.6.5 i.MX 93 DDR SI simulation guide

The simulation architecture includes the DDR controller (that is, the i.MX 93 processor), the PCB and the DRAM device. The IBIS model for the i.MX 93 processor is available from NXP. The DRAM device IBIS model must be obtained from the memory vendor.

This section describes how to check SI performance of the layout for a DDR design using the i.MX 93.

- Firstly, perform S-parameter extraction:

- It requires a 2.5D full-wave extraction tool, such as PowerSI from Cadence.

- Set the extraction bandwidth to 20 GHz.

IMX93HDG

All information provided in this document is subject to legal disclaimers.

- Port reference impedance: 50  $\Omega$  for signal ports, and 0.1  $\Omega$  for power ports.

- Coupled mode: Set the rise time to 20 ps and coupling coefficient to 1%.

- Secondly, perform time domain simulation:

- Stimulus pattern: 500-bit random code and different pattern for each signal within the same byte.

- · Ideal power.

- Probe at the die.

- Simulation at slow corner (worst case).

- Eye waveform triggered by aligning with the timing reference (DQS/CLK).

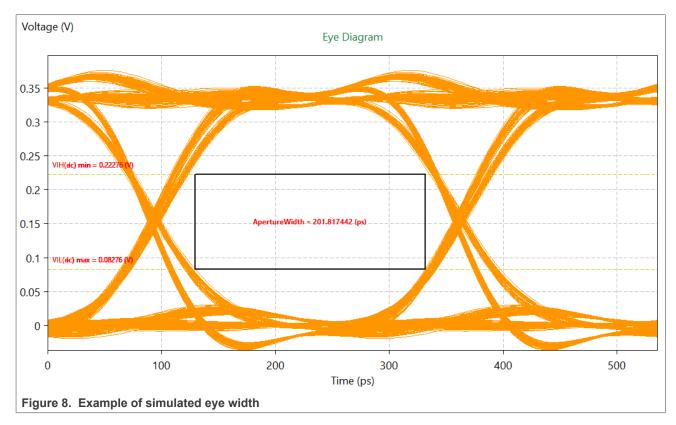

When the simulation is done, find the simulated worst eye width and compare with following requirements to see if it can pass:

#### For LPDDR4/4X-3733

- DQ Write: Eye width @VREF ±70 mV should be over 187 ps.

- DQ Read: Eye width @VREF ±70 mV should be over 175 ps.

- Cmd/Addr/Ctrl: Eye width @VREF ±77.5 mV should be over 361 ps.

The figure below shows an example of simulated eye width of LPDDR4/4X-3733 DQ write.

#### 3.6.6 i.MX 93 DDR package delays

While performing the required delay matching for LPDDR4/4X routing, the substrate routing within the i.MX 93 package needs to be accounted for and included in the match calculation. The table below lists the propagation/fly time from the die I/O to the package ball.

Table 19. i.MX 93 DDR package trace delays (11x11 package)

| Ball Name   | Delay (ps) | Ball Name     | Delay (ps) |

|-------------|------------|---------------|------------|

| DRAM_CA0_A  | 36.4       | DRAM_DQ03_A   | 30.3       |

| DRAM_CA1_A  | 42.7       | DRAM_DQ04_A   | 35.9       |

| DRAM_CA2_A  | 35.8       | DRAM_DQ05_A   | 33.5       |

| DRAM_CA3_A  | 43.5       | DRAM_DQ06_A   | 37.2       |

| DRAM_CA4_A  | 39.0       | DRAM_DQ07_A   | 37.0       |

| DRAM_CA5_A  | 45.8       | DRAM_DQ08_A   | 35.9       |

| DRAM_CKE0_A | 37.2       | DRAM_DQ09_A   | 33.9       |

| DRAM_CKE1_A | 33.0       | DRAM_DQ10_A   | 30.9       |

| DRAM_CK_C_A | 40.2       | DRAM_DQ11_A   | 33.7       |

| DRAM_CK_T_A | 40.0       | DRAM_DQ12_A   | 32.0       |

| DRAM_CS0_A  | 39.0       | DRAM_DQ13_A   | 29.4       |

| DRAM_CS1_A  | 37.8       | DRAM_DQ14_A   | 27.4       |

| DRAM_DMI0_A | 30.7       | DRAM_DQ15_A   | 33.6       |

| DRAM_DMI1_A | 29.2       | DRAM_DQS0_C_A | 33.3       |

| DRAM_DQ00_A | 31.1       | DRAM_DQS0_T_A | 33.7       |

| DRAM_DQ01_A | 31.6       | DRAM_DQS1_C_A | 20.7       |

| DRAM_DQ02_A | 33.7       | DRAM_DQS1_T_A | 20.9       |

Table 20. i.MX 93 DDR package trace delays (14x14 package)

| Ball Name   | Delay (ps) |

|-------------|------------|

| DRAM_CA0_A  | 45.7       |

| DRAM_CA1_A  | 53.4       |

| DRAM_CA2_A  | 49.7       |

| DRAM_CA3_A  | 56.1       |

| DRAM_CA4_A  | 53.2       |

| DRAM_CA5_A  | 60.6       |

| DRAM_CKE0_A | 50.7       |

| DRAM_CKE1_A | 42.8       |

| DRAM_CK_C_A | 48.8       |

| DRAM_CK_T_A | 48.4       |

| DRAM_CS0_A  | 53.6       |

| DRAM_CS1_A  | 47.9       |

| DRAM_DMI0_A | 40.7       |

| DRAM_DMI1_A | 43.5       |

| DRAM_DQ00_A | 44.0       |

| DRAM_DQ01_A | 40.9       |

| DRAM_DQ02_A | 46.8       |

Table 20. i.MX 93 DDR package trace delays (14x14 package)...continued

| Ball Name     | Delay (ps) |

|---------------|------------|

| DRAM_DQ03_A   | 40.3       |

| DRAM_DQ04_A   | 47.5       |

| DRAM_DQ05_A   | 43.0       |

| DRAM_DQ06_A   | 49.8       |

| DRAM_DQ07_A   | 46.0       |

| DRAM_DQ08_A   | 52.6       |

| DRAM_DQ09_A   | 48.7       |

| DRAM_DQ10_A   | 45.9       |

| DRAM_DQ11_A   | 49.6       |

| DRAM_DQ12_A   | 45.7       |

| DRAM_DQ13_A   | 42.1       |

| DRAM_DQ14_A   | 40.4       |

| DRAM_DQ15_A   | 47.5       |

| DRAM_DQS0_C_A | 32.6       |

| DRAM_DQS0_T_A | 32.8       |

| DRAM_DQS1_C_A | 31.7       |

| DRAM_DQS1_T_A | 31.9       |

Table 21. i.MX 93 DDR package trace delays (9x9 package)

| Ball Name   | Delay (ps) |

|-------------|------------|

| DRAM_CA0_A  | 32.7       |

| DRAM_CA1_A  | 45.2       |

| DRAM_CA2_A  | 35.9       |

| DRAM_CA3_A  | 43.2       |

| DRAM_CA4_A  | 42.3       |

| DRAM_CA5_A  | 50.6       |

| DRAM_CKE0_A | 37.0       |

| DRAM_CKE1_A | 34.5       |

| DRAM_CK_C_A | 48.1       |

| DRAM_CK_T_A | 47.2       |

| DRAM_CS0_A  | 40.9       |

| DRAM_CS1_A  | 36.3       |

| DRAM_DMI0_A | 24.5       |

| DRAM_DMI1_A | 30.9       |

| DRAM_DQ00_A | 19.1       |

| DRAM_DQ01_A | 24.7       |

| DRAM_DQ02_A | 24.4       |

Table 21. i.MX 93 DDR package trace delays (9x9 package)...continued

| Ball Name     | Delay (ps) |

|---------------|------------|

| DRAM_DQ03_A   | 25.1       |

| DRAM_DQ04_A   | 26.6       |

| DRAM_DQ05_A   | 30.1       |

| DRAM_DQ06_A   | 39.7       |

| DRAM_DQ07_A   | 33.4       |

| DRAM_DQ08_A   | 27.4       |

| DRAM_DQ09_A   | 31.9       |

| DRAM_DQ10_A   | 32.1       |

| DRAM_DQ11_A   | 25.3       |

| DRAM_DQ12_A   | 25.3       |

| DRAM_DQ13_A   | 21.2       |

| DRAM_DQ14_A   | 18.9       |

| DRAM_DQ15_A   | 25.4       |

| DRAM_DQS0_C_A | 17.0       |

| DRAM_DQS0_T_A | 18.8       |

| DRAM_DQS1_C_A | 25.4       |

| DRAM_DQS1_T_A | 26.4       |

# 3.7 JEDEC specification compliance

The i.MX 93 processors are designed and tested to work with the JEDEC JESD209-4A–compliant LPDDR4/4X memories. Timing diagrams and tolerances required to work with these memories are specified in the respective documents and are not reprinted here.

Meeting the necessary timing requirements for a DDR memory system is highly dependent on the components chosen and the design layout of the system as a whole. In this document, NXP cannot cover all the requirements needed to achieve a design that meets full system performance over temperature, voltage, and part variations. The PCB trace routing, PCB dielectric material, number of routing layers used, placement of bulk/decoupling capacitors on critical power rails, via placement, ground and supply planes layout, and DDR controller/PHY register settings - all are factors affecting the performance of the memory system.

Nevertheless, this hardware user's guide contains a large amount of valuable design information that NXP believes aid the design engineers in developing a DRAM memory system compliant with the JEDEC standards. NXP has validated design layouts for information on how to properly design a PCB for best DDR performance. NXP strongly recommends duplicating an NXP validated design as much as possible in the design of critical power rails, placement of bulk/decoupling capacitors, and DDR trace routing between the processor and the selected DDR memory.

Processors that demonstrate full DDR performance on NXP validated designs, but do not function on customer designs, are not considered marginal parts. A report detailing how the returned part behaved on an NXP validated system will be provided to the customer as a closure to a customer-reported DDR issue. Customers are responsible for properly designing the printed circuit board and correctly simulating and modeling the designed DDR system. They should validate the system under all expected operating conditions (temperatures and voltages) before releasing their product to the market.

# 3.8 High-speed routing recommendations

For more information about general high-speed routing considerations, see High-Frequency Design Considerations (document <u>AN12298</u>)

# 3.9 Reset architecture/routing

A reset button may be connected to **PMIC\_RST\_B** pin of the PMIC (PCA9451AHNY) for development purposes. This allows all voltages to be put to their initial default power-on state when depressing the reset button.