## Pentium<sup>®</sup> Pro Processor BIOS Writer's Guide

Version 2.0 January, 1996

## int<sub>e</sub>l

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\* Other brands and names are the property of their respective owners.

Copyright © 1996, Intel Corporation, All Rights Reserved.

This revision accompanies the source code modules that have been tested on an Intel validation platform.

The document has been updated to reflect the latest Pentium Pro processor silicon.

| Revision | Description                                 | Date  |

|----------|---------------------------------------------|-------|

| 0.9      | Pre-silicon draft for limited distribution. | 10/94 |

| 2.0      | Current release.                            | 01/96 |

### **Table of Contents**

| 1 | Intro  | duction   | 1                                                         |      |

|---|--------|-----------|-----------------------------------------------------------|------|

|   | 1.1    | Purpos    | se                                                        | 1-1  |

|   | 1.2    | Target    | Audience                                                  | 1-1  |

|   | 1.3    | Relate    | d Documents and Products                                  | 1-1  |

|   | 1.4    | Genera    | al Concerns of Modularity                                 | 1-2  |

|   | 1.5    | Conter    | nts of the Source Files                                   | 1-3  |

| 2 | Initia | alization | of the 82450 PCIset                                       |      |

|   | 2.1    | An Ove    | erview of the Target Platform                             | 2-1  |

|   | 2.2    | Genera    | al Issues of a PCI BIOS                                   | 2-2  |

|   | 2.3    | PCI Co    | onfiguration Mechanism #1 Access Macros                   | 2-2  |

|   | 2.4    | Initializ | ation of 82454 PCI Bridges                                | 2-3  |

|   |        | 2.4.1     | Early POST Initialization of 82454 PCI Bridges            | 2-4  |

|   |        | 2.4.2     | PCI Resource Allocation on 82454 PCI Bridges              | 2-4  |

|   |        | 2.4.3     | Advanced 82450 PCIset Feature Initialization              | 2-5  |

|   | 2.5    | 82452     | Memory Controllers                                        | 2-5  |

|   |        | 2.5.1     | Early POST Initialization of the 82452 Memory Controller  | 2-6  |

|   |        | 2.5.2     | AutoScan Module Initialization for the Memory Controller. | 2-6  |

|   |        | 2.5.3     | AutoScan Algorithm                                        | 2-6  |

|   | 2.6    | System    | n BIOS (F-Segment) Shadowing Issues                       | 2-10 |

| 3 | Pent   | tium® P   | ro Single Processor Initialization                        |      |

|   | 3.1    | Cache     | Management and Memory Type Range Registers                | 3-1  |

|   | 3.2    | MTRR      | Management                                                | 3-1  |

|   | 3.3    | Variab    | le MTRR Initialization Algorithm                          | 3-3  |

|   | 3.4    | Local A   | APIC Initialization                                       | 3-4  |

|   | 3.5    | Pentiu    | m Pro Machine Check Architecture                          | 3-5  |

|   | 3.6    | Pentiu    | m Pro Processor Common Setup Information                  | 3-5  |

| 4 | Pent   | tium Pro  | Multiprocessor Initialization                             |      |

|   | 4.1    | Multipr   | ocessor Initialization in BIOS                            | 4-1  |

|   | 4.2    | MP Init   | tialization Algorithm                                     | 4-1  |

|   |        | 4.2.1     | Algorithm for Bootstrap Processor                         | 4-2  |

|   |       | 4.2.2    | Algorithm for Auxiliary Processor Initialization | 4-3  |

|---|-------|----------|--------------------------------------------------|------|

| 5 | Penti | um Pro   | Processor System Management Mode Initialization  | on   |

|   | 5.1   |          | Pentium Pro Processor SMM                        |      |

|   | 5.2   | Pentiur  | m Pro Multiprocessor SMM Initialization          | 5-2  |

|   | 5.3   | Pentiur  | m Pro Multiprocessor SMM Handler                 | 5-3  |

|   |       | 5.3.1    | Only the BSP Executes SMM                        | 5-3  |

|   |       | 5.3.2    | Any Processor Can Execute SMM                    | 5-4  |

| 6 | Large | e Memo   | ory Support                                      |      |

|   | 6.1   | Descrip  | otion of the Interface                           | 6-1  |

|   | 6.2   | Implem   | nentation Issues                                 | 6-1  |

| 7 | Regis | ster Edi | itor Program                                     |      |

| 8 | Penti | um Pro   | Processor BIOS Update Feature                    |      |

|   | 8.1   |          | Jpdate                                           |      |

|   | 8.2   | Update   | e Loader                                         |      |

|   |       | 8.2.1    | Update Loading Procedure                         |      |

|   |       | 8.2.2    | Update Loader Enhancements                       |      |

|   | 8.3   | •        | e Signature and Verification                     |      |

|   |       | 8.3.1    | Determining the Signature                        |      |

|   |       | 8.3.2    | Authenticating the Update                        |      |

|   | 8.4   |          | m Pro Processor BIOS Update Specifications       |      |

|   |       | 8.4.1    | Responsibilities of the BIOS                     |      |

|   |       | 8.4.2    | Responsibilities of the Calling Program          |      |

|   |       | 8.4.3    | BIOS Update Functions                            |      |

|   |       | 8.4.4    | INT 15h-based Interface                          |      |

|   |       | 8.4.5    | Protected Mode Interface                         | 8-18 |

| 9 |       | -        | Processors                                       |      |

|   | 9.1   |          | verDrive Processors and the CPU Signature        |      |

|   | 9.2   |          | rive Processor CPUID                             |      |

|   | 9.3   | Comm     | on Causes of Upgradability Problems Due to BIOS  | 9-1  |

| Α |       |          | em Address Map                                   |      |

|   | A.1   |          | h, E820h - Query System Address Map              |      |

|   | A.2   | Assum    | ptions and Limitations                           | A-3  |

## int<sub>e</sub>l.

| Α.     | Example Address Map                                            | A-3  |

|--------|----------------------------------------------------------------|------|

| Α.     | Sample Operating System Usage                                  | A-4  |

| Figure |                                                                |      |

| 2-     | Target Platform for Reference BIOS Implementation              | .2-1 |

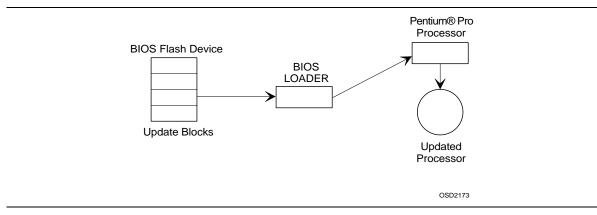

| 8-     | Integrating Processor Specific Updates                         |      |

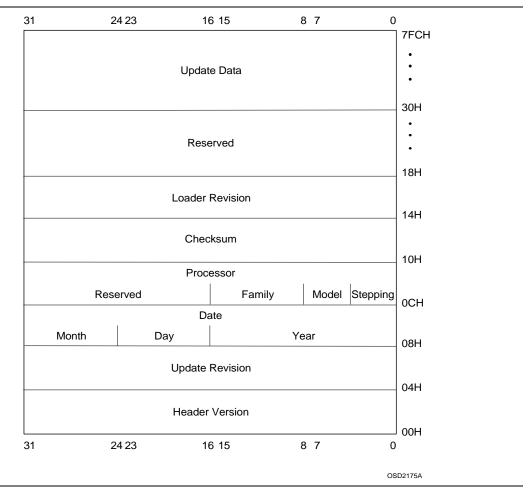

| 8-2    | BIOS Update Data Block                                         | .8-2 |

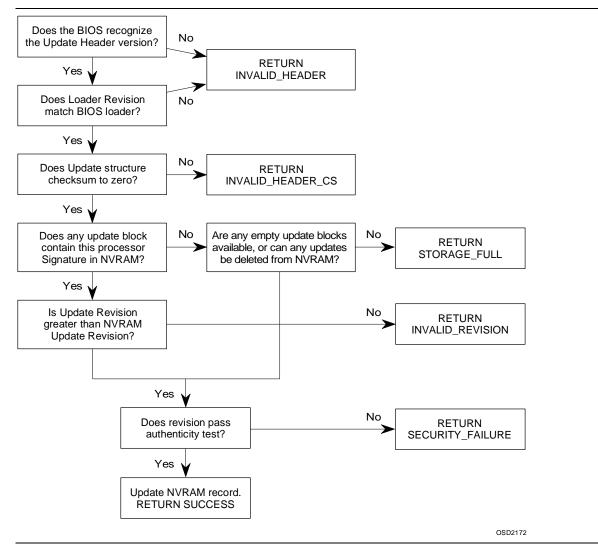

| 8-3    | Write OperationFlow Chart                                      | 3-15 |

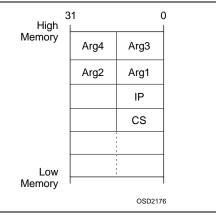

| 8-4    | 16-bit Stack Frame on a 32-bit Stack                           | 3-20 |

| Tables |                                                                |      |

| 2-     | Interleave Bit Settings in 82452 Command Register (Offset 4Ch) | .2-7 |

| 2-2    | DRAM Rowlimit Settings                                         | .2-8 |

| 2-3    | DRAM Rowlimit Settings                                         | .2-8 |

| 2-     | Setting Rowlimits with a Blank Row (Ex: Row 1 is a blank row)  | .2-9 |

| 2-     | Setting Rowlimits When Row 1 is a Blank Row                    | .2-9 |

| 3-     | Default Memory Ranges for Memory Types                         | .3-2 |

| 8-     | BIOS Update Header Data                                        | .8-3 |

| 8-2    | BIOS Update Functions                                          | 3-11 |

| 8-3    | Parameters for the Presence Test                               | 3-12 |

| 8-4    | Parameters for the Write Update Data Function                  | 3-13 |

| 8-     | Parameters for the Control Update Subfunction                  | 3-16 |

| 8-0    | Mnemonic Values                                                | 3-16 |

| 8-     | Parameters for Read BIOS Update Data Function                  | 3-17 |

| 8-8    | Return Code Definitions                                        | 3-18 |

| 8-9    | BIOS Upgrade Extensions Data Fields                            | 3-19 |

| 8-     | Return Codes                                                   | 3-26 |

| 9-     | OverDrive Processor CPUID                                      | .9-1 |

| A-     | Input                                                          | A-1  |

| A-     | Output                                                         | A-2  |

| A-     | Address Range Descriptor Structure                             | A-2  |

| A-     | Address Ranges in the Type Field                               | A-2  |

| A-     | Sample Memory Map                                              | A-4  |

# int<sub>e</sub>l.

### 1 Introduction

This document explains BIOS programming for systems based on the Pentium<sup>®</sup> Pro processor. The document may accompany Intel Pentium Pro processor Basic Input Output System (BIOS) source code example files, which serve as the Pentium Pro processor and 82450 PCIset reference BIOS implementation. This implementation targets a typical system based on the Pentium Pro processor-82450 PCIset. See the Related Documents and Products section for ordering information, if you need the source code files.

#### 1.1 Purpose

The *Pentium Pro Processor BIOS Writer's Guide* describes the issues that surfaced during the design and development of Intel's Pentium Pro processor reference BIOS system code. Its purpose is to provide OEMs and BIOS developers with the example source code and documentation needed to address these issues while developing a system based upon the Pentium Pro processor. This document is a supplement to other manuals for the Pentium Pro processor and 82450 PCIset.

#### 1.2 Target Audience

This document is intended for Pentium Pro processor BIOS architects, code developers and others interested in the software issues of a Pentium Pro processor-82450 PCIset based system.

#### **1.3 Related Documents and Products**

This document refers to the following publications and products:

- Pentium Pro Operating System Writer's Guide, order number 2422692-001, Intel Corporation.

- MultiProcessor Specification, v1.4, order number 242016-004, Intel Corporation.

- PCI BIOS Specification, Revision 21, August 26, 1994, Intel Corporation.

- Pentium Pro Processor BIOS Reference Kit, Reference Source Code V2.0, available late February, 1996. Order using the following telephone numbers: U.S.A./Canada 1-800-253-3696 Option 1 International 1-503-264-2203 Option 1

#### 1.4 General Concerns of Modularity

The source files that accompany this document manage Pentium Pro processor components, the 82450 PCIset and some of the platform resources. These CPU and chipset initialization files might differ in architecture when compared to similar initialization files in a particular core BIOS.

The source file architecture is based on following key design decisions:

- The code is structured so that it can be easily hooked into any standard BIOS.

- Chipset and other register information is easily extracted from the source files. The implementation contains no complicated, implicit data structures for register values, but uses simple read/write/alter macros, so that one can easily determine values loaded into the chipset register and utilize the information in any form that is desirable for a particular BIOS.

The following implementation strategies achieve these two design goals:

- A single Register Initialization Hook contains all the pre-initialization for the chipset and all the system and platform components that are supported. This code block must be hooked into a typical core BIOS in a very early Power On Self Test (POST) stage, before memory-sizing and AutoScan. The code in this module is written such that it does not use any system memory, so that one can safely execute the code prior to memory configuration.

- System and Video shadow routines have been isolated as separate hooks to allow incorporation of these routines into different BIOS systems in a flexible manner.

- All the advanced initialization of the chipset is grouped into a separate group of routines. This code can and should be hooked at a much later stage in POST, when memory is available.

- The AutoScan module for the 82450 PCIset, including code for switching the machine to protected mode, is isolated in a separate macro that can be called as an independent module.

- Simple register read/write/alter macros are used so that the reader can easily extract the information about the register data. For example, a register of the 82450 PCIset set might be manipulated as:

```

WriteOPB_C_8BitRegister OPBMemoryATTR0,Data

or

AlterOMC8BitRegister OMCMemoryATTR0,Data1,Data2

```

Where:

Data1 specifies the AND pattern of bits for the register under consideration, and

Data2 specifies OR pattern of bits.

So, if a particular Pentium Pro processor BIOS must conform to a specific register table architecture, the register information can easily be extracted to build the table.

#### 1.5 Contents of the Source Files

The following list provides a brief description of the contents of the Reference BIOS source files.

#### Files Contained in REFBIOS Directory

| orion.inc    | initialization code for 82450 PCIset.                                                    |

|--------------|------------------------------------------------------------------------------------------|

| orion.asm    | procedures that support the macros located in the initialization code.                   |

| reset.inc    | procedures that are executed every time a CPU reset occurs.                              |

| p6access.mac | macros that support access to Pentium Pro processor registers.                           |

| p6_equ.inc   | equates for Pentium Pro processor registers.                                             |

| p6ftsfar.asm | code that initializes the Pentium Pro processor.                                         |

| orion.mac    | macros that access the 82450 PCIset components.                                          |

| orionequ.inc | equates for the 82450 PCIset.                                                            |

| system.mac   | PC-AT* macros for supporting various PC-AT functions.                                    |

| sys_equ.inc  | equates that support the system.mac file.                                                |

| ptform.mac   | macros that support the necessary hooks of the Pentium Pro processor platform.           |

| pci.mac      | PCI-Config 1 type access macros.                                                         |

| ptform.inc   | equates needed to manage the Pentium Pro processor platform.                             |

| cntrl.inc    | option flags that control the Pentium Pro processor BIOS build.                          |

| biosgd.doc   | a copy of this document in Microsoft* Word* 6.0 format.                                  |

| p6mp.asm     | Pentium Pro processor MP initialization code.                                            |

| p6mpfar.asm  | Pentium Pro processor MP Support code.                                                   |

| mem64meg.asm | Code to support the call interface that manages memory systems larger than 64 megabytes. |

| P6int15.asm  | Code to support INT 15 API for BIOS Update feature.                                      |

| update.asm   | Code that loads BIOS Update Data.                                                        |

| flshrdwt.asm | Code to support read/write into Intel Flash device.                                      |

#### Files Contained in REGEDIT Directory

p6h.zip a package that contains executables and support files for the Pentium Pro processor and 82450 PCIset set register editor Program.

# int<sub>e</sub>l.

This chapter explains the initialization mechanisms used in the reference BIOS implementation. The 82450 PCIset is used in the sample implementation. The same general principles can be applied to other chipsets.

#### 2.1 An Overview of the Target Platform

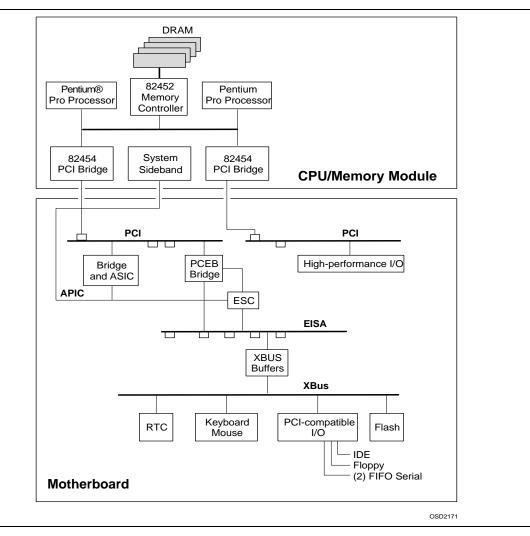

The assumed target platform has two or four Pentium Pro processor CPUs with dual PCI bridges that provide a twin PCI bus architecture. The two PCI channels are peer channels at the host level. Figure 2-1 provides the block diagram of the target system.

Figure 2-1. Target Platform for Reference BIOS Implementation

PCI and PC compatibility is derived from the PCI bridge chipset and the motherboard. The two 82454 PCI bridges in the CPU/Memory module are connected into the two PCI buses of the motherboard. The first bridge that connects to the PCI bridge chipset and branches to EISA/ISA bus systems is called the compatibility bridge, because all PC compatibility devices, such as DMA and the Key Board Controller, are located on this channel. The second bridge produces a second PCI bus to which high performance I/O components can be attached. These I/O components on the second PCI bus provide another high bandwidth I/O channel that can meet the high-performance requirements of the Pentium Pro processor.

The PCI bridge chip is mainly used to extend basic interrupt support and to give full interrupt steering ability to the PCI channels. In addition, the motherboard must supply at least one I/O APIC so that multiple Pentium Pro processor CPUs can function in a way that complies with the *MultiProcessor Specification*. The 82452 Memory Controller is located on the CPU/Memory module and supports the DRAM modules. The compatibility channel also accommodates PC-compatible hardware that supports a parallel port, IDE hard disks, two serial ports, and a floppy controller.

#### 2.2 General Issues of a PCI BIOS

The PCI specification presents two distinct methods of accessing the registers contained in the PCI components. These methods are called PCI Configuration Mechanism #1 and PCI Configuration Mechanism #2. Most PCIsets that Intel has designed and produced for i486<sup>™</sup> and Pentium processors support access using Configuration Mechanism #2, although a few support access by Configuration Mechanism #1. Configuration Mechanism #2 is not a preferred mechanism, although at first glance it appears easier to implement and requires less code space.

The 82450 PCIset supports only Configuration Mechanism #1 due to the following reasons:

- Configuration Mechanism #2 uses a separate bridge-forward register to address the PCI components. This consumes the entire CXXX I/O space.

- The hardware designer cannot use the same PCI components at the same PCI bus level. In other words, two 82454 PCI bridges can not be directly connected to the Pentium Pro processor bus. This precludes providing multiple PCI buses and memory controllers at the same PCI bus level, which is required to effectively utilize the full performance potential of the Pentium Pro processor.

#### 2.3 PCI Configuration Mechanism #1 Access Macros

This section describes the design issues confronted when implementing the Configuration Mechanism #1 PCI access method. In Configuration Mechanism #1, data is read and written as 32-bit chunks. The access mechanism is initiated by writing the address of the device with proper bus, device, and register numbers into OCF8h as a 32-bit quantity. The format of this 32 bit quantity includes six bits (bit 2 through bit 7) that describe the register number. The data can be read back from the OCFCh address as a 32, 16 or 8 bit quantity. In Intel architecture, data that is read as 32 bits from an I/O port spans four I/O addresses to preserve byte addressability, which is very important for compatibility.

## int<sub>e</sub>l

Given these architectural attributes, following are two typical ways that Configuration Mechanism #1 access routines can be implemented:

- Compute the address of the data register by taking into account the offset of the given PCI register from the nearest low 4-byte boundary. For example, to read/write the PCI register at 50h as an 8-bit quantity, choose the data register 0CFCh. For the register at 51h, choose the data address 0CFDh, for 52h choose 0CFEh, and for 53h choose 0CFFh.

- Design the Configuration Mechanism #1 PCI access macro code to locate and shift data bits properly, depending on the address boundary of the particular PCI register being read. If address 10h is read as a 32-bit I/O read operation, the 8 data bits of I/O port 10h are placed in positions D0 through D7, the 8 data bits of I/O port 11h are placed in positions D8 through D15, and so forth. Thus, Configuration Mechanism #1 PCI access macro code must be able to locate and shift data bits properly, depending on the address boundary of the particular PCI register being read. The reference BIOS implementation uses this method.

For either approach, the 4-address span makes Configuration Mechanism #1 access macros longer than Configuration Mechanism #2 access macros.

Follow these steps to minimize the impact of code space when using the Configuration Mechanism #1 PCI access code in the Reference BIOS:

- Always access the PCI register manipulation code as a call from POST modules wherever some memory is available.

- In cases where no memory is available, execute the PCI register manipulation code by transferring the control to it through a jump instruction and passing a return address pointer in one of the registers. For an example, see the Register Initialization Hook code in the orion.inc file. The disadvantage of this method is that working registers become unavailable because they are used to pass both the parameters and the return address information.

Once you have chosen to use PCI Configuration Mechanism #1, all access to the devices on the platform must be performed using the same mechanism, including all PCI devices that are embedded on the motherboard and any PCI devices that occupy PCI slots. Partial use of access Configuration Mechanism #1 in a given platform is illegal according to the *PCI Specification*.

#### 2.4 Initialization of 82454 PCI Bridges

In the Pentium Pro processor-based host platform, two PCI busses are generated by two 82454 PCI bridges that are connected to the Pentium Pro processor system bus. These two 82454 PCI bridges are peers at the host level. Initialization of 82454 PCI bridges occurs at three stages:

- Early POST initialization

- PCI resource allocation

- Advanced 82450 PCI chipset feature initialization

#### 2.4.1 Early POST Initialization of 82454 PCI Bridges

Early POST code through the OrionRegInitHook macro initializes a few fundamental registers. This code also detects and identifies 82454 PCI bridges before attempting to initialize them.

A configuration cycle that has a bus number equal to 0 enables access to the internal registers of both bridges. The bus number of the second bridge, also called the non-compatibility bridge, is initialized to an arbitrary selection of 80h during this initialization process. PCI slots under the second bridge have the same device numbers as those in the slots under the compatibility bridge and are only distinguished by their different bus number. The distinction between identically device-numbered slots under both bridges is achieved by programming a different PCI bus number for the second bridge. Then, the PCI devices under the second bridge can be accessed with this new bus number, 80h in the Reference BIOS.

**NOTE.** Even after a new bus number is programmed for the second 82454 *PCI* bridge, the internal registers of the second bridge can still be accessed with bus number 0 and the appropriate second bridge device number.

The 82454 PCI bridge has been designed with multiple PCI channels in mind. The second bridge "knows" that it is a non-compatibility channel chip and initializes itself with different power-on default values compared to the compatibility bridge. This distinction is made at the time of power on reset by sampling the hardware state of certain 82454 PCI bridge pins, simplifying the actual early POST initialization modules. If the bridge did not have this feature, a number of second bridge registers would have to be initialized to avoid potential resource conflict. For example, video memory ranges, ISA bus I/O ranges, BIOS address ranges, and so forth, must be configured on the second bridge as disabled, so that the second bridge does not respond and corrupt the valid data that the compatibility bridge brings onto the Pentium Pro processor bus in these ranges.

#### 2.4.2 PCI Resource Allocation on 82454 PCI Bridges

PCI resource allocators call some of the initialization modules for 82454 PCI bridges in order to initialize both compatibility and non-compatibility bus resources. This hook is built into PCI bus scan code so that it works in a twin PCI bus architecture. Source code modules in the reference BIOS implementation contain procedures to program the PCI resources into 82454 PCI bridge registers, but the core PCI base BIOS must provide a hook to call the chipset-dependent routines, as explained in greater detail below.

The PCI bus initialization code modules search for PCI devices on both compatibility and secondary PCI bus structures. Consider a situation in which these routines have found a PCI device residing on the second bridge's PCI bus and that device requires an I/O range and a memory range. In this situation, the BIOS must be able to take these resource requests and program them into both 82454 PCI bridges. In fact, the compatibility bridge must be programmed in such a way that it does not respond to these ranges, but the secondary bridge must be programmed so that it does respond to these ranges. Otherwise, data on the Pentium Pro processor bus is corrupted whenever this PCI device is accessed. I/O ranges can be programmed using OPBIO\_Range registers and memory ranges can be enabled and disabled using Memory\_Gap registers. For example, if PCI resource allocators want to channel I/O addresses 8000h-8200h

## int<sub>e</sub>l

down to the second PCI bus, then program the same start (8000h) and end (8200h) addresses to both first and second 82454 bridge I/O gap range registers (Offset 98h), set the enable bit (bit 31 of the gap range register) in the second bridge, and reset the same bit in the first bridge. This tells the first bridge not to respond to this I/O range (8000h-8200h in this example) and tells the second bridge to respond to the same I/O range. Note that a compatibility 82454 PCI bridge responds to all addresses by default and must be told only about the range of addresses that it must not respond to. The same explanation holds for memory gap range registers at offset 88h that are used to allocate PCI memory address ranges.

#### 2.4.3 Advanced 82450 PCIset Feature Initialization

This initialization is usually done at an advanced POST stage. In the sample code, the NewFeaturesHook module is called during late POST. Memory and stack space are available at this stage, so requirements on the initialization code are less stringent at this time. This code module consults CMOS-based setup to determine features that should be enabled. The 82450 PCIset offers a rich set of features that customers can use depending on the platform support. Some of these new features, listed below, need special processing while programming. For a complete list of the features, refer to the code module called NewFeaturesHook in the reference code packet.

82452 Memory Controller System Error Reporting

Enabling single bit error correcting of Pentium Pro processor data must be done before clearing out memory during a memory scan. This feature is enabled by setting bit 9 of the 82452 memory controller system error reporting command early in the chipset initialization.

#### 82452 Memory Controller Address Bit Permuting

Enabling this feature changes the way the memory pages are addressed, therefore it must be enabled before the BIOS starts using memory. Also, the BIOS must ensure the number of memory rows is a power of two, all rows are the same size, and all populated rows are adjacent and start at row 0. If any one of these conditions is not satisfied, this feature must not be enabled. In the Pentium Pro processor BIOS reference code, this feature is enabled by the AutoScan module.

#### 2.5 82452 Memory Controllers

The 82452 controller is a versatile multi-interleave memory controller that supports very large DRAM systems. Its register organization enables the chaining of multiple 82452 memory controllers if needed in very large systems. The second controller can be programmed to start refreshing DRAMs from the top of the memory of the first controller. Use of Configuration Mechanism #1 PCI access enables use of multiple memory controllers on the same Pentium Pro processor bus. Although some of Intel's internal evaluation systems support such a second 82452 memory controller, the Reference BIOS makes no attempt to do so.

Initialization of the 82452 memory controller falls into 2 stages:

- Early POST initialization: During this stage the memory mappings need to be returned to disabled if the reset is not due to a hardware reset.

- AutoScan module initialization : An AutoScan module determines the size of the onboard memory and adjusts the memory size registers to support them. After running the AutoScan module and setting up memory, advanced features of the 82452 memory controller can be enabled based on the user driven Setup menu.

#### 2.5.1 Early POST Initialization of the 82452 Memory Controller

Not much initialization needs to be done to the 82452 memory controller in early POST because the default values are sufficient to begin AutoScan. The controller memory timings must be adjusted to the slowest values to make sure that the AutoScan module runs properly, then the memory must be adjusted to run at whatever speed it is designed to operate. If the system contains a second controller, you must disable it so the AutoScan routine can deal with the first controller before any others.

#### 2.5.2 AutoScan Module Initialization for the Memory Controller

The AutoScan module must find the size and shape of the memory and adjust the 82452 memory controller registers accordingly. The AutoScan algorithm also finds the best possible interleave for the installed memory subsystem. Before starting the actual algorithm that sizes the memory, initialization code must perform the following actions:

- Pentium Pro processor caching must be turned off. In the sample code, caching is disabled by running an early POST RegisterInitHook routine. The Pentium Pro processor cache can be turned off using the conventional CD bit that is present in the CRO register. Consult the system.mac file in the Reference BIOS for more details.

- The AutoScan algorithm needs all types of paging mechanisms and memory-mapping schemes to be disabled, including any SM memory mappings, gap registers, and any other such features.

- The BIOS must switch the processor to protected mode with A20 of the processor enabled so that it can access all the physical memory located on the bus. AutoScan software does not have to support asymmetric memory types since the 82452 memory controller hardware supports them automatically.

#### 2.5.3 AutoScan Algorithm

This algorithm supports the common Column Address Strobe (COMCAS) feature of the 82450 PCIset, a feature that is needed to support double-sided byte parity SIMMs.

The algorithm follows this 8-step sequence to determine the memory interleave that is supported by the motherboard's memory system:

The first four steps determine whether to set the COMCAS bit.

- 1. Set up the 82452 memory controller command register to 1-to-1 interleave, with the COMCAS enable bit (Bit 9 of the 82452 memory controller Command register) turned off.

- 2. Set the DRAMRowLimit0 register to 0001h and other row registers (DRAMRowLimit1 through DRAMRowLimit7) to a maximum, 07ffh.

- 3. Write 32 bytes of known pattern of data from address 0h onwards.

- 4. Read back the 32 bytes starting from address 0h and analyze the results, as indicated in this example of a 32-byte pattern that is visualized as eight 4-byte chunks of data:

- If matching chunks with the original data pattern written to address Oh are organized as adjacent pairs of 4-byte chunks, leave the COMCAS enable bit in default setting and go to Step 5 to determine interleave of the system.

- If one 4-byte chunk matches the original data that was written but its adjacent 4-byte chunk does not match, turn on the COMCAS bit then repeat steps 3 and 4. If a match is found between adjacent 4-byte chunks this time, leave the COMCAS bit set and proceed to Step 5 to determine the interleave of the system. If no match is found for any combination of COMCAS bit settings, then the memory system is faulty and/or does not contain memory in row 0. This is a terminal error and in this case the system must be halted.

The next three steps determine the interleave bits.

- 5. Set up the 82452 memory controller command register to reflect 4:1 interleave. In some systems burst delay may have to be set to 0 for 4:1 interleave configuration.

- 6. Write 32 bytes of data with a known pattern from address 0h onwards.

- 7. Read back the 32 bytes of this know-pattern of data from address 0h and analyze the results. In this example a 32-byte pattern is visualized as four 8-byte chunks of data:

- If all four 8-byte chunks, the full 32 bytes of data, are intact, then the memory subsystem has 4-to-1 interleave. Set the 82452 memory controller command register to reflect 4:1 interleave.

- If any two 8-byte chunks are intact, then those two groups could have 2-to-1 interleave.

Set interleave bits 11 to 14 (in 82452 Command Register at offset 4ch), as shown in Table 2-1, and set bits 3 and 4 to indicate 2-to-1 interleave.

**NOTE.** *At least 2 bits in this table must be set for 2:1 interleave to operate.*

— If no two blocks of 8-byte chunks are intact, only 1-to-1 interleave is possible in this memory system. Set the interleave bits to indicate the active interleave as shown in Table 2-1.

| Bit number | is set to indicate data is OK in the |

|------------|--------------------------------------|

| 11         | first 8-byte chunk                   |

| 12         | second 8-byte chunk                  |

| 13         | third 8-byte chunk                   |

| 14         | fourth 8 byte chunk                  |

Table 2-1. Interleave Bit Settings in 82452 Command Register (Offset 4Ch)

If a single 8-byte chunk is not intact, ROW 0 contains no valid memory. Indicate a memory failure and halt the system. The last step determines the memory size.

8. Set the DRAM row limit registers successively to reflect the memory sizes in Table 2-2:

| Rowlimit Registers         | Interleave Size |  |

|----------------------------|-----------------|--|

| 8M, 16M, 32M, 64M, 128M    | 1:1 memory      |  |

| 16M, 32M, 64M, 128M, 256M  | 2:1 memory      |  |

| 32M, 64M, 128M, 256M, 512M | 4:1 memory      |  |

Table 2-2. DRAM Rowlimit Settings

For each of the row limits above, write data to each 4 megabyte boundary (e.g. 4 megabyte, 8 megabyte, etc.) and check for an alias to address 0. The actual size of the installed row is the previous 4 megabyte boundary size that was successfully tried (i.e., no alias to address zero was found).

#### 2.5.3.1 Sizing Algorithm Implementation Details

There are several ways to implement the sizing (step 8) algorithm. The implementation in the reference BIOS is described in the steps below.

Starting with DRAM row 0, sequence the row limit using the values in Table 2-2, while testing for memory aliasing. To test for aliasing, write data patterns to addresses in 4 megabyte increments starting at the 4 megabyte address. Check for an alias to address 0 each time. Once aliasing occurs, the size of row 0 equals the last successful row setting. For example, if the row limit was set to 64 megabytes when aliasing occurred, then the size of row 0 is 32 megabytes.

For a PC hardware compatible design, Row 0 must contain some memory.

2. Assuming that row 0 has been sized to X megabytes and the interleave of the memory subsystem is equal to IL (where IL is equal to 1 for a 1:1 memory subsystem, 2 for a 2:1 memory subsystem, and 4 for a 4:1 memory subsystem), program the row limit registers as shown in Table 2-3.

| Table 2-3. | DRAM | Rowlimit | Settings |

|------------|------|----------|----------|

|------------|------|----------|----------|

| Rowlimit Registers      | Size of Memory            |

|-------------------------|---------------------------|

| DramRowLimit0           | = (X/4)                   |

| DramRowLimit1 through 7 | $= (X/4) + (IL)^{*}(8/4)$ |

#### 2.5.3.1 Blank Row Management

To verify that memory is installed in row 1, write to address X+4 megabytes and check if there is any memory present. If there is no memory at this address, row 1 is a blank row. Copy the contents of DRAM row 0 memory size register to row 1 and continue on to size the next row. In this case, if there is no memory in row 1, the registers are set as in Table 2-4.

| Rowlimit Registers      | Size of Memory            |

|-------------------------|---------------------------|

| DramRowLimit0           | = (X/4)                   |

| DramRowLimit1           | = (X/4)                   |

| DramRowLimit2 through 7 | $= (X/4) + (IL)^{*}(8/4)$ |

Once blank row management is complete, continue writing at addresses of 4 megabyte increments, starting from X megabytes, while checking for aliases to the X megabyte address. If aliasing does not occur until (X+(IL)\*8/4), set the row limits as shown in Table 2-5 and repeat the procedure until an alias is detected.

Table 2-5. Setting Rowlimits When Row 1 is a Blank Row

| Rowlimit Registers      | Size of Memory             |

|-------------------------|----------------------------|

| DramRowLimit0           | = (X/4)                    |

| DramRowLimit1           | = (X/4)                    |

| DramRowLimit2 through 7 | $= (X/4) + (IL)^{*}(16/4)$ |

Upon alias detection, the size of the row equals the last successful row size setting.

#### 2.5.3.2 General Description of Sizing the "Nth" Row

This section provides a general description of how to size a row.

If the Nth row is to be sized and the sum of all previously sized rows is Y megabytes, then:

- DramRowLimit(0) through DramRowLimit(n-1) are set to their proper sizes, taking into consideration any blank rows.

- DramRowLimit(n) through 7 [Where  $N \le 7$ ] = (Y/4) + (IL)\*(8/4)

- Perform blank row management, as described earlier, by checking for memory at (Y+4) megabytes.

After blank row management, start at Y megabytes and continue writing at address increments of 4 megabytes. Check for aliases at address Y megabytes. If aliasing does not occur until (Y/4)+(IL)\*(8/4), increase the row limits to the next setting and repeat the procedure until an alias is detected. The size of the Nth row equals the last successful row size setting.

#### 2.5.3.3 Programming Issues of the AutoScan Algorithm

The AutoScan algorithm implementation contains the following traditional programming complexities:

• As the algorithm is coded, more and more registers are used. Eventually, there are few registers left to call the register access code. Memory is still not available, so calling the register access code is more difficult. In the sample source file, direct embedded macros are avoided since they blossom into full assembled code during compilation. Every working register and its upper half (bits 16 through 31) is used. The data is brought into the lower sixteen bits by judicious use of rotate instructions whenever it is needed for further processing.

• Due to this register shortage, the sample implementation uses even BP in the AutoScan code implementation. Depending upon the core BIOS, it might be unacceptable to use the BP register or some other register that is used in this sample. In such an implementation, changes might be needed in the AutoScan code.

#### 2.6 System BIOS (F-Segment) Shadowing Issues

System BIOS segment shadowing is almost always necessary to yield acceptable performance, because most systems use 8-bit BIOS chips and access to ROMs are traditionally slower than access to the DRAM subsystem. The partition of PCI bridge and memory controller into separate physical entities makes the shadowing algorithm in the 82450 PCIset more complex.

The following sequence of steps makes up the shadow algorithm in the reference BIOS implementation:

- Configure the memory attribute register (MemoryAttrReg0) of the 82452 memory controller to enable memory writes to F-Segment. At this stage of programming, memory reads to the F-Segment go down to a buffered ISA bus, called the X bus, through the compatibility 82454 PCI bridge, and memory writes to F-Segment go to shadow DRAM at F-Segment.

- 2. Copy the data of F-Segment ROM into shadow RAM at F-Segment by executing a string copy. At this point, the BIOS must enable shadowing by turning off ROM accesses and enabling memory read accesses to shadow RAM at F-Segment. This task is difficult because the DRAM controller is a different physical entity with its own set of registers. By enabling DRAM accesses before turning off ROM accesses, ROM data coming through the compatibility bridge and shadow RAM data coming from the 82452 memory controller both drive the Pentium Pro processor bus for a brief period. This condition is not stable and can result in a system crash. So, instead of executing the shadow enabling portion of the code out of ROM, proceed along the following steps and execute this code out of DRAM.

- 3. Copy the code that turns off ROM Read accesses and enables shadow RAM into DRAM at 4000:0h. The BIOS has control of the DRAM resources at this point and the operating system is not loaded so this action is likely to be safe. However, problems with using the explicit address 4000:0h for this purpose could occur in some core BIOS architectures because of compression and such things. In these cases, any convenient DRAM address can be chosen so long as about 200h bytes are available for storage. This temporary storage is needed only until shadow is enabled.

- 4. Call this code in DRAM through a FAR call.

- 5. Control goes to a DRAM routine that turns of the ROM accesses and enables the ROM shadow. Then, control returns to ROM through a FAR return. In the DRAM routine, use fully embedded macros for accessing the 82450 PCIset registers because the other access code is in F-segment and does not support an inter-segment call.

- 6. The last step is to write protect the F-Segment DRAM.

# 3 Pentium<sup>®</sup> Pro Single Processor Initialization

This chapter describes initialization for systems with a single Pentium Pro processor as the CPU.

#### 3.1 Cache Management and Memory Type Range Registers

The Pentium Pro processor has an internal L2 cache. The BIOS programmer must program the CPU's internal registers to set various memory attributes. Pentium Pro processor architecture also introduces two more newer memory attributes in addition to the usual Write Through (WT) and Write Back (WB) types. The new memory attributes that are added are Write Combining (WC) and Write Protected (WP). The WC type is used on frame buffers and the WP type is used for ROM shadow regions. Refer to the *Pentium Pro Processor Operating System Writer's Guide* for a full description of Memory Type Range Registers (MTRRs).

#### 3.2 MTRR Management

Memory Type Range Registers are written and read in the same way as the conventional Machine Specific Registers (MSRs) of a typical Pentium processor by using RDMSR and WRMSR instructions. MTRRs are 64-bit registers and are divided into fixed and variable MTRRs. The MTRR capability register is examined to find out whether or not fixed MTRRs are implemented. Fixed MTRRs deal with memory between 0 and 1 megabyte, driven by the Setup menu, and they have been packaged in such a way as to implement PC-compatible address ranges easily. Variable MTRRs deal with memory above 1 megabyte.

In the reference implementation, a CMOS database that is Setup menu driven programs the memory types into fixed MTRRs. The code can also be used to configure 0- to 640-kilobyte base memory as WC type memory, for use in debugging the hardware efficiently. In a production BIOS, using WC is only an option for video RAM.

The reference BIOS uses variable MTRRs to cache memory above 1 megabyte. These registers can be used to specify a base address and a mask.

Although the user can change the memory type for a given address range of the memory by using the Setup menu, the reference BIOS implementation uses the default settings in Table 3-1.

## intəl

| Memory Range                | Use                                      |

|-----------------------------|------------------------------------------|

| 0-640 kilobytes             | configured as Write Back                 |

| B Segment (0B0000h-0BFFFFh) | WC                                       |

| C,D Segments                | WP if we do ROM shadow for these regions |

| E and F segments            | WP                                       |

| 1 megabyte to top of memory | Write back                               |

| APIC address range          | Uncached                                 |

| Table 3-1. | Default Memory | Ranges for Memory Types |

|------------|----------------|-------------------------|

|------------|----------------|-------------------------|

The BIOS programmer must be careful while writing to MSRs because writing to undefined MTRRs, which are MSRs, generates an exception. For this reason, it is important to check whether variable and fixed MTRRs are implemented in a particular Pentium Pro processor machine and to check how many of these are implemented. All this information can be obtained by reading the MTRRcap register. Keep the following guidelines in mind when designing this code module:

- MTRR initialization is not lost upon assertion of INIT pin or on INIT IPI messages sent using the local APIC bus. MTRR registers go to their default values only upon assertion of a hard reset or at power-on.

- In a hardware environment, any other silicon that needs to be aware of the caching environment must be homogeneous with the MTRR based information. This uniformity of caching information becomes more important if a chipset other than the 82450 PCIset is used with the Pentium Pro processor CPU.

- The Pentium Pro processor local APIC address range must be set up as Uncached. The local APIC register access uses memory-mapped I/O which requires the range to be Uncached.

- Mask register calculation of a variable MTRR is complex. In the reference BIOS and implementation, the memory size is determined by reading the 82450 PCIset registers and then processing the value to get the physical mask that must be used. Refer to the sample code for more details.

- The Pentium Pro processor variable MTRR registers provide for specifying discontinuous memory ranges depending upon the mask provided. In general, the BIOS should ensure that discontinuous MTRRs are not enabled accidentally due to specifying an improper mask value for MTRRs. A shrink-wrapped operating system may refuse to boot or enable specific advanced features, such as mapping a linear frame buffer using the write-combining memory type (WC) on a platform that utilizes discontinuous MTRRs. This feature should only be used in special circumstances, such as for a 4KB uncacheable memory hole that occurs every 16MB throughout the entire 0-4GB address range. This type of memory hole does not normally occur on PC architecture platforms.

- It is acceptable to start from address 0 for a variable MTRR, even if any fixed MTRRs are already defined for this range, because the fixed MTRRs always override the variable ones.

## intط

Follow these guidelines while initializing the MTRRs of the Pentium Pro processor:

- A global enable bit, the FE bit in the MTRRdefType register, is used to enable all of the fixed range MTRRs. Each variable MTRR register pair (base and mask) is enabled by setting the V bit (bit 11) in the particular mask register. The enable bits (FE bit and the V bit) of MTRRs have default values indicating that they are disabled upon power-on reset; but the values of other bits in any MTRR are undefined. So, the BIOS code must initialize all the MTRRs to a known state by clearing all the fixed and variable MTRRs to zero before starting the initialization. This conservative method of initialization ensures that no MTRR is left in an undefined power-on state.

- BIOS code must clear the mask bits and base address bits of all variable MTRRs before using a specific variable MTRR. In addition, while changing a particular variable MTRR, the BIOS must be certain that its mask is disabled before attempting to change its base.

- The BIOS must reserve at least two variable MTRR register pairs (physbase and physmask) for operating system use. These must be the last two variable MTRRs. For example, if there are 8 variable MTRRS, 0-7, then MTRR pairs 6 and 7 are reserved for operating system use. If the BIOS does not reserve these, the operating system may not boot. But, initialization of these operating system reserved MTRRs to zero must be done by the BIOS as a safety measure.

- The BIOS should set MTRRdefType to UC. It is dangerous to set MTRRdefType as any other memory type due to the possibility of programming errors and speculative execution by the processor in areas where memory does not exist. The ability to set the default memory type to WB was designed for large memory systems with some holes. However, this function is now better served by the overlapping UC memory type capability.

#### 3.3 Variable MTRR Initialization Algorithm

Fixed MTRRs control caching of memory below 1 megabyte and are set up according to Table 3-6. Variable MTRRs control the caching attributes of memory above 1 megabyte.

The basic architecture of MTRR base and mask registers is explained in the *Pentium Pro Processor Programmer's Reference Manual*. There are several methods of implementing this algorithm. The steps needed for the implementation used in the reference BIOS are:

- Read MTRRCap register and get the count of variable MTRRs implemented in a particular CPU implementation. Initialize them to zero. The BIOS needs to reserve the top two variable MTRR pairs for operating system use. If all available MTRR pairs (range and mask) are consumed in implementing the BIOS algorithm itself, then some operating systems will not boot.

- 2. Find the total amount of memory by reading the memory controller registers. This assumes that the AutoScan module has been run and all memory registers that control the size of the system memory have been initialized. We can assume this since the AutoScan module runs very early in POST with caches disabled. In a Pentium Pro processor and 82450 PCIset based implementation, total installed memory can be found by reading the DramRowLimit7 register.

- 3. Set the first MTRRBaseRegister to 0 and figure the largest power of two portion of memory that can be carved out of the total memory installed. For example, if the total memory is 384 megabytes, then the largest power of two portion that can be carved out is 256 megabytes.

4. Figure out the mask for this largest power of two portion of memory. This is done in the SetVarMTRRMaskReg procedure in the reference BIOS, which sets the mask to satisfy the address match comparison rule that may be described as follows:

Address AND MTRRphysMask = (MTRRphysbase AND MTRRphysMask). The mask is set by the routine such that all addresses in this carved power of two portion of memory satisfy this equation and will be cached according to the memory type set in the lower portion of MTRRphysbase register.

- 5. Compute the remaining amount of memory and carve out another largest possible power of two portion. Repeat Step 4 to find the mask for this portion after setting the next available MTRRphysbase register to the top of the address that was cached in the previous step.

- 6. Repeat Steps 4 and 5 until all the installed cacheable memory in the system is exhausted or you run out of MTRR register pairs. Remember that in a Pentium Pro processor implementation that has eight MTRR pairs, only six of them are available for BIOS use.

Here is an example with numerical values. In a system with 96 megabytes of total memory, the MTRRPhysBase/Mask registers have the following values after executing the MTRR initialization algorithm:

- MTRRPhysBase0 = 0000\_0000\_0000\_0006h

- MTRRPhysMask0 = 0000\_000F\_FC00\_0800h This caches the first 64 megabytes of memory

- This caches the first 64 megabytes of memory as WB memory type.

- MTRRPhysBase1 = 0000\_0000\_0400\_0006h

- MTRRPhysMask1 = 0000\_000F\_FE00\_0800h This caches the next 32 megabytes of memory as WB memory type.

#### 3.4 Local APIC Initialization

The Pentium Pro processor contains an integrated local APIC device in order to support a multiprocessor environment. This local APIC receives interrupt-related messages. Intel recommends that the local APIC be initialized to virtual-wire mode, as required for compliance with the *MultiProcessor Specification*, even in a single processor environment.

Noteworthy issues in APIC initialization are:

- All local APIC registers are reset to default values upon any hard CPU reset. INIT signal assertion and INIT IPI messages reset all local APIC registers except APIC BASE and APIC ID registers. Local APIC initialization code must be hooked to core BIOS routines such that a local APIC gets initialized to virtual-wire mode every time the CPU is reset (both hard and soft resets).

- APIC address space is relocatable, unlike the APIC registers of the Pentium 100 processor. It is possible to remap Pentium Pro processor's APIC addresses to space below 1 megabyte and program the APIC in real mode. Code developed to be portable across a group of related processors should continue to program the APIC in protected mode and not relocate the APIC base address.

- Set the memory type in MTRR for the address range where APIC registers reside as the Uncached (UC) type.

#### 3.5 Pentium Pro Machine Check Architecture

The Pentium Pro processor has enable and status bits for several machine check errors that could occur during the operation of the processor. Potentially, this feature allows the processor to execute a graceful shutdown. In most cases, the machine check provides information about errors that occurred during the processor's normal operation. Generally, a machine check exception handler reads the enable and status bits of the architecture, logs the appropriate data, and provides user-based error messages. The *Pentium Pro Processor Operating System Writer's Guide* describes the use of machine check architecture in detail.

The MC0\_CTL register contains bits that can be set by the BIOS since their functions are platform dependent and the BIOS knows the platform architecture. An operating system should not set bits in the MC0\_CTL register . An operating system may reset (clear) a bit in MC0\_CTL to disable reporting of specific errors.

#### 3.6 Pentium Pro Processor Common Setup Information

Information in the Setup menu usually is specific to a particular BIOS implementation. CMOS resource allocation is done bit-wise in most modern BIOS architectures to prevent a waste of precious CMOS space and to allow more Setup items to be added.

Following is a list of new Setup menu items that support Pentium Pro processor and 82450 PCIset features.

- Number of processors as found by the MP algorithm, with an option to take some off the MP table and hence off the booting process.

- Write Protect memory types (enable/disable) for all ROM spaces.

- WC memory types (enable/disable) for frame buffers.

- Definition of cacheable/uncacheable ranges for use with physical MTRRs.

- Deturbo timer in the 82450 PCIset.

- PCI features of the 82454 PCI bridge, such as write posting for inbound and outbound PCI transactions.

- Several Error Reporting features of the 82454 PCI bridge.

- Memory Error Correction features of the 82452 memory controller.

- Memory Bandwidth enhancement features of the 82452 memory controller, like page open policy.

- SM RAM ranges.

It is not necessary to give a setup choice for every 82450 PCIset feature that is enabled. The setup feature may be nice in an evaluation BIOS but may be less desirable in a production BIOS. The reference BIOS implementation gives a setup choice for every 82450 PCIset feature, since it was designed to be a part of evaluation BIOS.

### 4 Pentium Pro Multiprocessor Initialization

These features of the BIOS multiprocessor (MP) initialization algorithm are described in this chapter:

- It does not depend on the number of processors installed in the system, but is capable of figuring out the number of processors installed in the system. The algorithm described works for a maximum of fifteen processors.

- It has the ability, through the Setup menu, of taking a requested number of processors off the system without actually unplugging them from their sockets.

- It can do limited testing on each of the processors and initializes their MTRRs.

- It makes sure that the MTRRs of all the processors in an MP system have identical values by using a common CMOS database.

- It loads processor specific BIOS update data to all the processors installed in the system. See Chapter 8 for more details on the BIOS update feature of Pentium Pro processor CPUs.

- It builds the MP table for use by the operating system, as described in the *MultiProcessor Specification*.

- This algorithm needs RAM for its operation. This limitation is not imposed by the algorithm, since RAM is required for building the MP table anyway. The RAM for building the MP table can be chosen either in the extended BIOS data area or in the F-Segment shadow RAM. The size of the RAM table depends on the system configuration.

#### 4.1 Multiprocessor Initialization in BIOS

The Pentium Pro processor is MP-ready, so proper MP initialization is an essential part of the Pentium Pro processor BIOS. The Pentium Pro processor implements an MP initialization protocol during which processors communicate with each other, elect a single processor to be a boot processor, and put the auxiliary system processors in a loop waiting for StartUp Inter Processor Interrupts (IPIs). This wait state, described in the *Pentium Pro Operating System Writer's Guide*, is a special state wherein the processor is not executing, but its local APIC is listening to StartUp IPI messages on the APIC bus. This MP Boot Protocol is executed only on a processor reset signal toggle. It is not re-executed upon receipt of Init APIC messages. In other words, the boot processor is not renegotiated on receipt of an INIT IPI message.

#### 4.2 MP Initialization Algorithm

This section describes the algorithm that is used by the reference BIOS for initializing Pentium Pro processor-based multiprocessor systems.

Upon reset, the Pentium Pro processors elect a BSP from among themselves and put the other processors into a wait state. Processors in the wait state wait for StartUp inter-processor interrupts on their local APIC bus.

#### 4.2.1 Algorithm for Bootstrap Processor

The bootstrap processor (BSP) performs these parts of the algorithm:

- 1. The elected BSP starts executing the BIOS, proceeds through POST and other BIOS components, and enters the MP algorithm code.

- 2. The BSP initializes a predefined RAM location to a value of 1. In the reference BIOS, this location is called the CPUCounter. The BSP initializes the LockSemaphore routine to Vacant = 00h for use by a module that initializes all non-BSPs.

- 3. The BSP sends a StartUp APIC message broadcast to all other processors by programming the interrupt command register with a vector that points to the FindAndInitAllCPUs module.

- 4. The BSP waits for the auxiliary processors to complete their initialization (described in detail in the next section). This wait loop can be implemented in various ways. It can be a simple software wait loop that is large enough to allow auxiliary processors to complete their initialization. It can use the BIOS timer (a hardware timer for use by the BIOS that is implemented by all Intel chipsets) to implement an exact delay time loop. The local APIC of the BSP also contains a timer that can be used for wait loop implementation. Finally, a more complex wait algorithm can be implemented as follows.

- a. The auxiliary processors increment a CPUCounter (a memory location initialized to 01h by the BSP at the start of the algorithm) as soon as they start their initialization loop, as described in the next section. The BSP examines this location using a synchronized lock read every two seconds (two second poll frequency is a suggested value and individual BIOS implementations can tune them according to their requirements). The BSP compares this CPU counter value on a particular read to the value of the same variable during the previous read. If it has not changed, all processors are finished with their initialization. This BSP wait loop algorithm assumes an auxiliary processor takes no longer than two seconds to complete initialization. The CPUCounter value at the end of the algorithm reflects the total number of CPUs in the system, including the BSP.

- b. When the BSP exits the timing loop, the CPUCounter contains the number of processors in the system, and all the processor entries in the MP table are built. Refer to the description of FindAndInitAllCPUs for details. At this stage, all auxiliary processors are initialized with an identical set of MTRRs and other CPU registers.

- c. The BSP reads the CMOS RAM initialized through setup to determine the number of processors that the user wants in this boot session. The BSP then constructs the remainder of the MP table and removes or disables the MP table entries for the non-operational processors. For example, if the user wants only two processors out of four populated ones, MP entries corresponding to two processors are removed or disabled. In our algorithm, an INIT IPI is sent to all the auxiliary processors, causing them to wait for a STARTUP IPI event. INIT IPI must be sent to auxiliary processors after System Management Mode (SMM) initialization of auxiliary processors is completed (if SMM is enabled in CMOS based setup). The SMM initialization procedure is detailed in Chapter 5. The operating system consults the MP table entries to find enabled processors and sends them a STARTUP IPI.

- d. The MP table checksum is calculated for the adjusted MP table. Other parameters, such as the number of entries and the length of the MP table, are also determined.

## int<sub>e</sub>l

#### 4.2.2 Algorithm for Auxiliary Processor Initialization

The algorithm for auxiliary processor initialization is implemented in a module called FindAndInitAllCPUs in the reference BIOS and has the following responsibilities:

- Although all CPUs enter this algorithm almost simultaneously, this module uses Synchronization Locks to let processors one-by-one into the rest of the algorithm.

- Each CPU runs CPUID instruction and initializes its MTRRs by reading the CMOS data base.

- Each CPU constructs its particular entry in the MP table. This entry includes information on the CPUID, and the address and version of the local APIC.

- Each CPU increments the CPUCounter (a memory variable initialized by BSP), so that the BSP knows the number of processors in the system.

- If System Management Mode (SMM) is enabled, it is initialized. Refer Chapter 5 for more details.

The algorithm performs these actions:

- 1. All auxiliary CPUs wake up simultaneously after listening to the StartUp IPI broadcast from the BSP and start executing this module.

- 2. The first processor that executes the TestLock procedure sets the LockSemaphore routine to NotVacant=0ffh and proceeds to Step 3. All other processors wait in the TestLock procedure until the processor that moved to Step 3 completes and unlocks the lock semaphore variable. The TestLock procedure can be coded as:

```

Mov al, NotVacant

TestLock:

Xchg Byte ptr [LockSemaphore], al

Cmp al, NotVacant

Jz TestLock

----To Step (3)

```

**NOTE.** On Intel Architecture processors, the Xchg instruction has a builtin lock feature.

- 3. The first auxiliary CPU to emerge from the TestLock procedure increments the CPUCounter variable.

- 4. The auxiliary CPU is channeled through the same routines that initialized the BSP to initialize the MTRRs from the common CMOS data base.

- 5. The auxiliary CPU runs CPUID to know its features.

- 6. The auxiliary CPU constructs its entry in the MP table based on its CPUID, Local APIC ID, and so on.

- 7. The auxiliary CPU loads any BIOS update data to the processor. See Chapter 8 for more details on the BIOS processor update feature of Pentium Pro processor CPU.

- 8. The auxiliary CPU releases the lock on the semaphore by executing the ReleaseLock routine. This action allows the next waiting CPU into the initialization loop:

ReleaseLock:

```

Mov al, Vacant

Xchg Byte ptr [LockSemaphore], al

---To Step (9)

```

9. The auxiliary CPU goes into a wait loop. If SMM of the auxiliary processor is enabled in the CMOS based setup, the CPU receives an SMI message from the BSP when the BIOS performs SMM initialization (as explained in Chapter 5). If SMM of the auxiliary processor is disabled, BSP sends an INIT IPI message to the auxiliary processor, which puts the initialized CPU into a special state wherein it halts and waits for a STARTUP IPI message from the operating system.

### Pentium Pro Processor System Management Mode Initialization

The Pentium Pro processor implements System Management Mode (SMM), which helps system developers provide very high level systems functions, such as power management or security, in a manner that is transparent not only to the application software but also to the operating systems.

This chapter describes the initialization of SMM for both single and multiprocessor systems.

#### 5.1 Single Pentium Pro Processor SMM

The Pentium Pro processor CPU can accept both synchronous and asynchronous system management interrupts (SMI) that switch the processor to SMM. A synchronous SMI usually is generated because of an I/O trap by the chipset or additional hardware. The chipset must provide a register with status bits to indicate the occurrence of a synchronous SMI. The 82450 PCIset currently does not support synchronous SMIs. SMM initialization is done at a later part of the POST.

The 82450 PCIset does not provide any processor address translation during SMM. The registers inside the 82452 memory controller need to know the SMM address range in order to protect the address range from any other processor modes.

During initialization, the operating system is not loaded and the RAM resource is owned by the BIOS. When the BSP executes the SMM initialization module, all of the chipset initialization is complete and RAM is available.

The following steps explain an algorithm for initializing the SMM of a single processor system.

- 1. The CPU starts up the InitSMM software module. This module is responsible for the SMM initialization. First, the InitSMM module copies a small section of code, the SMBaseInit module, to the Default SMI Vector at 3000h:8000h. At this point, the operating system is not booted and all the memory is owned by the BIOS, so this operation does not destroy any operating system or program data. The CPU also initializes a flag, indicating that SMM initialization is not yet finished.

- 2. In order to set up the SMM base, the CPU sends itself an SMI through its local APIC by programming the interrupt command register, and then starts waiting on a flag that indicates that the CPU SMM is not initialized. Rather than waiting on the flag eternally, use a watch dog timer that makes use of the local APIC's timer resource. If this timer times out and the flag indicates that SMM is not initialized, then SMM initialization has failed.

- 3. The APIC-based SMI reaches the BSP core, which enters SMM and starts executing at 3000h:8000h. In other words, the SMBASEInit module has been started by the BSP in SMM. The 82450 PCIset need not be programmed to enable SMI, because no support is required from the 82450 PCIset at this point.

5

- 4. The SMBASEInit module initializes the SMBASE slot in the SMM dump area, at address cs:0FEF8h, to the required SMI vector address. Ideally, this address is read from the Setup menu, to be sensitive to user's configuration needs. For this example, assume that it is 0A000h.

- 5. Copy the SMMHandler module to the SMM address range. In this example, this address is 0A000:8000h. Program the memory attribute register at the 82452 controller CSE Offset 58h to enable the memory range. This SMMHandler contains the code that handles an SMI, and it is implementation-specific, depending on the purpose for which the SMI is used in a given system.

- 6. Turn off the enable bits of the Memory Attribute register at 82452 memory controller CSE Offset 58h, since we enable it as SM RAM in the 82452 controller later on.

- 7. The SMBASEInit module updates a flag to indicate BSP SMM is initialized and then executes an RSM instruction.

- 8. Control returns to the InitSMM module, which exits the waiting loop in the InitSMMmodule because of the status of the initialization flag.

- 9. The algorithm programs the 82450 PCIset's 82452 memory controller registers to give them information about the SMM address range by programming the SMRAM Range Register at 82452 memory controller CSE Offset 0B8h. Then, enable the SMM ability by programming the 82452 memory controller register at CSE offset of 57h.

#### 5.2 Pentium Pro Multiprocessor SMM Initialization

The algorithm presented here is capable of initializing the SMM of a Pentium Pro processor-based multiprocessor system. It requires a 32-kilobyte SMM slot per processor. For example, if a system contains four Pentium Pro processors and a decision has been made to use A and B segments of the shadow memory for SMM, then the SMBASE registers of the four processors can be successively programmed to 98000h, 0A0000h, 0A8000h and 0B0000h. Note that, although the SMBASE of the first processor is initialized to 98000h, it still uses memory within A and B segments, since SMM entry points are at SMBASE+8000h (SMBASE+EIP wherein EIP=8000h on entry to SMM mode). As more processors are added, the demand for SM RAM also goes up and it may become necessary to locate SMM code just below the top of installed memory.

The SMM initialization module runs after MP initialization and has access to the MP table constructed during MP initialization. In other words, the BIOS has all the information about the number of processors and their respective APIC Ids. Note that SMI APIC messages are accepted by the auxiliary processors only when they are executing code. The MP initialization module, described in Chapter 4, puts the auxiliary processors into a wait loop (if SMM is enabled in the Setup menu) and defers sending INIT IPI messages to auxiliary CPUs until the SMM initialization is completed.

The BSP's SMM initialization is done exactly as explained in the previous section on single processor initialization. After the BSP's SMM initialization is complete, the remainder of the MP algorithm follows these steps:

- 1. Once BSP's SMM is initialized, the BSP consults the MP table that is already constructed by the MP initialization module. The BSP gets information about the number of processors to be initialized and about their APIC IDs from this consultation.

- 2. To indicate the number of the processors being initialized, the BSP sets a flag that is readable by SMMBaseInit module.

## int<sub>e</sub>l

- 3. The BSP sends an SMI APIC message to the next processor to be initialized by using its APIC ID and programming the interrupt command register and starts waiting on a flag, indicating that the next processor SMM is not initialized. Instead of waiting on the flag eternally, use a watch dog timer that makes use of the local APIC's timer resource. If this timer times out and the flag indicates that SMM is not initialized, the SMM initialization for this processor has failed.

- 4. The next processor enters SMMBaseInit module. The module consults its flags to figure out that this is incremental initialization of the next processor. The SMMBaseInit module initializes the SMBASE slot in the SMM core dump at address cs:0FEF8h to the PreviousSMBaseAddress + 32 kilobytes.

- 5. The SMMBaseInit module copies the SMM Handler code to Previous SMM HandlerAddress + 32 kilobytes.

- 6. The SMMBaseInit module updates flags for the use of the BSP and executes an RSM instruction, returning to its wait loop.

- 7. Once again, the MP table is consulted to find information about the next processor and the initialization process is repeated.

- 8. Continue this procedure until the MP table indicates that no more processors are to be initialized.

- 9. Send an INIT IPI message broadcast to all auxiliary processors.

#### 5.3 Pentium Pro Multiprocessor SMM Handler

The SMM handler is the code module that services the system management interrupt (SMI).

At least two types of implementations can be used in a typical Pentium Pro multiprocessor SMM handler:

- Only the BSP executes SMM.

- Any processor can execute SMM.

#### 5.3.1 Only the BSP Executes SMM

The following steps explain the structure of an SMM handler when only the BSP is allowed to execute the SMM handler:

- 1. When an SMI occurs in the system, all processors enter their respective SMM spaces. All processors but the BSP are held waiting on flags in their SMM data area.

- 2. The BSP continues execution of the SMM handler and carries it to completion.

- 3. The BSP resets and releases the flags on other processors.

- 4. All processors execute an Resume (RSM) instruction and return to the state that they were in before the SMI interruption.

### int<sub>e</sub>l

#### 5.3.2 Any Processor Can Execute SMM

The following steps explain the structure of an SMM handler, where any one of the processors is allowed to execute the SMM handler.

- 1. When an SMI occurs in the system, all processors enter their respective SMM spaces. They race to a TestLock procedure. This procedure is often described as "race to a flag" algorithm and is explained in Chapter 4. Only one processor gets to a TestLock procedure first and starts executing the SMM handler. We call this processor the SMM processor.

- 2. All other processors are held off in a waiting loop, waiting on a flag until the SMM processor finishes the SMM code execution and releases the lock.

- 3. The SMM processor continues execution of the SMM handler and carries the SM handler to completion.

The SMM processor resets and releases the flags (locks) on other processors. The SMM processor also sets an SMMDone flag. Other processors released from the loop examine the SMMDone flag and execute an RSM instruction. The BSP also exits SMM by executing an RSM instruction. Whatever method of implementation is chosen, all processors are brought into SMM simultaneously.

If some processors are left in normal mode and others are brought into SMM, the operating system will crash if it is not designed to lose some of its processor resources involuntarily. This is true in most of the current operating system designs.

### 6 Large Memory Support

This chapter describes the call interface for memory larger than 64 megabytes.

#### 6.1 Description of the Interface