# THIS SPEC IS OBSOLETE

Spec Number: 001-65252

Spec Title: AN1071 – Single Versus Multiple Transaction

Translator

Sunset Owner: RSKV

Replaced By: None

# AN1071 – Single Versus Multiple Transaction Translator

# AN1071

Associated Project: No

Associated Part Family: CY7C65620/30, CY7C65640/40A/40B, CY7C65632/42

Software Version: None

**Associated Application Notes: None**

# **Application Note Abstract**

High-speed USB 2.0 hubs have a component to provide communication to full-speed and low-speed devices when the hub is operating at high-speed. This component is called a transaction translator (TT). The USB 2.0 specification allows two different implementations: one TT for all downstream ports (TT/hub) or one TT for each downstream port (TT/port). The TetraHub™ (CY7C65640/40A/40B), which is a four-port high-speed hub, provides you with the option of using this part in single TT (TT/Hub) or multiple TT (TT/Port) mode. AN1071 presents the differences and advantages of using multiple TT high-speed hub.

## Introduction

A transaction translator is an important component of a high-speed hub device which, in essence, provides a communication link between the upstream-facing port of the hub and a downstream-facing port when they are operating at different data transfer rates. This is the case when the hub is connected to a high-speed host with full-speed or low-speed device(s) plugged into the ports facing downstream.

The USB 2.0 specification allows a hub to be configured to have a single TT for all the downstream ports or one TT for each of the downstream ports. The TetraHub implements both these configurations. To understand the technical trade-offs of these two implementations, a knowledge of the process involved in host-initiated transfers to/from a full- or low-speed device is necessary.

This application note provides this information briefly, followed by a discussion on the TT and its functionality in the hub architecture. This is followed by a section discussing how the operating system recognizes the capabilities and limitations of the hub. The application note ends with a discussion and illustration of cases of the hub functioning in multiple TT and single TT modes.

**Note**: In this application note, Tetrahub is used to refer to CY7C65640/40A/40B/42 except where noted.

## **Transaction Translator**

The transaction translator is the logic component in the hub that is responsible for isolating the high-speed signaling environment from the full- or low-speed signaling environment. This is especially important when the hub is operating at high-speed when connected to a high-speed host with full-speed or low-speed devices connected to the

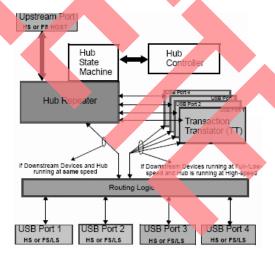

downstream-facing ports. This causes an incompatibility in the rate of data transfers between the upstream and the downstream ports. A special mechanism (logic) is needed to convert the upstream data transfer speed to the downstream data rate for the device and the host to be in conformity with the data transfer rate. This function is performed by the transaction translator logic in the hub. Figure 1 shows the place of the transaction translator in the hub architecture.

Figure 1. Hub Architecture Displaying the Four TTs

The TT participates in the high-speed split transactions on the high-speed bus through the upstream port and issues full- and low-speed transactions on its downstream facing ports.

Details on how the split transactions are handled by the high-speed handler for the upstream port. The full- and low-speed handlers for the downstream ports are not discussed

in this application note. This mechanism is covered in detail in the USB specification 2.0. However, this application note covers the functionality and performance of the hub related to having a single TT versus a multiple TT operating mode with illustrations.

## **Enumeration of the USB 2.0 Hubs**

When a USB 2.0 hub is connected to a high-speed capable port of the host, the host determines the TT implementation of the hub as a part of the enumeration process of the device. This information is specified in the bDeviceProtocol field of the device descriptor. A hub with a single TT must specify a value of one while a hub with multiple TTs must specify a value of two. Because all USB 2.0 hubs must support the TT/hub implementation, hubs with multiple TTs have a default interface of TT/hub operation and an alternate setting for TT/port operation. The bInterfaceProtocol field of the interface descriptor for TT/hub operation must be set to two. This is summarized in the following table.

| Descriptor Field<br>Name | Single TT<br>(TT/Hub) | Multiple TT<br>(TT/Port) |

|--------------------------|-----------------------|--------------------------|

| bDeviceProtocol          | 1                     | 2                        |

| bInterfaceProtocol       | 1                     | 2                        |

See section 11.23.1 in the USB 2.0 specification for more information on the hub device descriptor.

If the hub has the TT/Port implementation and the host has driver support (hub driver) for TT/port operation, then the hub driver may select the hub's alternate setting numbered one, configuring the hub to operate in TT/port mode and enabling all TTs. Otherwise, the hub operates in the default TT/hub mode and only one TT is enabled.

When a device is attached to a high-speed hub, the hub's notification pipe returns a value corresponding to the port to which the device is connected. The host resets the port, enabling access to that device. If the device is a full- or low-speed device, the host must issue all transactions through the TT associated to the device using the split transaction protocol.

#### **Transaction Translator Functionality**

Being a high-speed hub device, the TetraHub uses the split transaction tokens mechanism to support transfers between the high-speed host controller and the full- or low-speed devices connected to the downstream-facing ports. This high-speed split transaction is used to initiate a full- or lowspeed transaction through the hub and some full-/low-speed device endpoint. The high-speed split transaction also allows the completion status of the full- or low-speed transaction to be retrieved from the hub. This approach allows the host controller to start a full- or low-speed transaction through a high-speed transaction and then continue with other high-speed transactions without having to wait for the full-/low-speed transaction proceed/complete at the slower speed. This entire process is covered in the USB 2.0 specification. Refer to chapter 11 for more details about the state machines and the definitions of split transactions.

The host sends a split transaction token specifying the TT through the hub address and port number. If the hub is configured to operate in TT/hub mode, the port number is ignored, and the transaction will be executed on all full- and low-speed enabled ports.

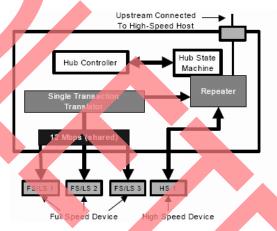

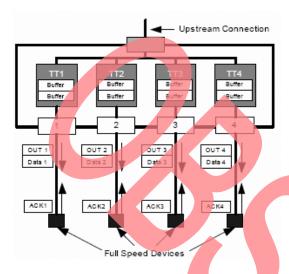

When the hub is operating at high-speed and is configured to TT/Hub mode, all of the full-speed devices plugged into the downstream facing port of the hub share the same 12-Mbps pipe. Therefore, when three full-speed USB 1.1 devices are attached to a single-TT hub, each device shares a single 12-Mbps pipe created by the single TT as shown in Figure 2.

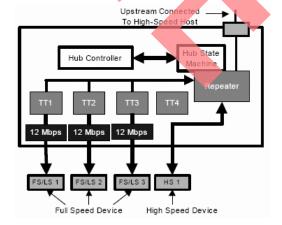

If the hub is configured to operate in TT/port mode, then the transaction is executed on only the port associated with the TT. Therefore, the TT/port implementation allows multiple transactions to be executed simultaneously, thus improving performance. Each TT is an independent entity. Just as TTs in different hubs may operate in parallel, so may TTs in the same hub. The host may overlap the operation of TTs so that a system may achieve the bandwidth equivalent of having an independent USB 1.1 host controllers in the system. Each TT adds approximately the equivalent of 12 Mbps of USB 1.1 bandwidth. Figure 3 shows the operation of the transaction translators when the hub is configured in multiple TT mode.

Figure 2. Bandwidth Shared among the Full-Speed Devices in Single TT Mode of Hub

Figure 3. Designated Pipe for Each Full-Speed Device in Multiple TT Mode of Hub

## Illustrations

This section provides clarification of the performance of the hub in TT/Hub versus the TT/Port with some case illustrations. The first two cases show the TetraHub functionality in single TT mode, while the last two involve the TetraHub functionality in multiple TT mode. The sets of examples presented illustrate how the TT/port architecture provides superior performance for full-/low-speed transfers as it enables simultaneous transfers to occur on each downstream port.

## Single TT Mode (TT/Hub)

In the single TT mode, all IN/OUT tokens are broadcast over all the enabled ports facing downstream. A single TT is tasked with servicing all the devices connected to the downstream facing ports. This reduces the efficiency when all the four ports are active (a full- or low-speed device connected to each of the downstream facing port).

The following examples display how the TT handles an OUT transfer and IN transfer between a host and a full-speed device plugged into the hub.

## OUT Transfer in TT/Hub Mode

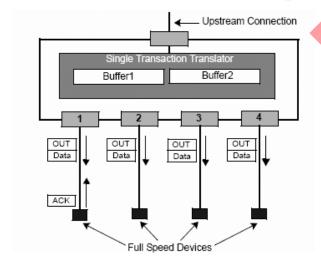

Figure 4 displays a hub performing a full-speed OUT transfer from the host to a full-speed device plugged in one of the downstream-facing ports. The TT broadcasts the OUT token followed by the data and awaits a response from one of its downstream ports. Since the OUT transfer was designated for an endpoint on a device that is connected to port 1, the ACK token is returned on that connection while all other connections remain idle. There is no response from the rest of the enabled ports.

Figure 4. TT/Hub OUT Transfer

## IN Transfer in TT/Hub Mode

In Figure 5, the TT is performing an IN transfer from a fullspeed device plugged into one of the downstream ports to the host.

Figure 5. TT/Hub IN Transfer

The IN token is broadcast on all the downstream ports. Since the IN transfer was designated for a particular endpoint on a device that is connected to port 3, the data is returned on that connection while all other connections remain idle. Note that although not shown, the OUT token for the status stage would be broadcast on all downstream ports, to which only the Port 3 would respond.

## Multiple TT Mode (TT/Port)

In the Multiple TT mode, where each port has a dedicated transaction translator, an IN/OUT token is sent to only one specific port by its dedicated transaction translator. This improves performance as compared to the single TT mode, even when all the four ports are active (a full- or low-speed device connected to each of the downstream facing port). The following examples display how the TT handles an OUT transfer and IN transfer between a host and a full speed device plugged into the hub when the hub is operating in TT/Port mode.

## OUT Transfer in TT/Port Mode

In Figure 6, the TTs are all performing OUT transfers simultaneously. Each TT has a unique set of buffers from which the data is sent only to the corresponding port connection.

Figure 6. TT/Port OUT Transfer

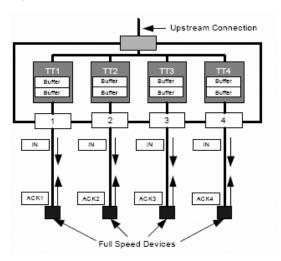

#### IN Transfer in TT/Port Mode

In the example shown in Figure 7, the TTs are all performing IN transfers simultaneously. Each TT has a unique set of buffers in which one buffer per TT stores the data read in from the corresponding port connection. Each TT is operating independently. Each of these TTs functions in parallel, improving the efficiency and performance.

Figure 7. TT/Port IN Transfer

# Summary

This application note illustrates the advantages of operating a high-speed hub in multiple transaction translator mode versus a single transaction translator mode. The maximum possible bandwidth a hub can provide for classic-speed devices is the number of enabled TTs times 12 Mbps. Therefore, a hub with a single TT can only provide a maximum of 12 Mbps.

The illustrations presented in this application note show that a four-port hub with a TT/port implementation can support as much USB 1.1 bandwidth as supported by four separate hubs with single TT implementations. Developers of hubs should consider their application before choosing which TT architecture to use.

When implementing a system, consider the types of devices and the speeds they will run at. If downstream devices are either all high-speed or just a single full-/low-speed device a lower cost single TT hub can be considered. If the application is multiple full-/low-speed devices with a need for bandwidth a multi-TT hub should be used. In the case of consumers connecting full-/low-speed devices with USB 2.0 hubs that use single-TT technology, they are bound to face performance issues when multiple devices are used. Therefore, when designing for the general use only a multi-TT hub implementation will give the throughput benefit that USB 2.0 offers for their classic speed devices.

Currently, Cypress offers the TetraHub (CY7C65640A) which can be configured in either single TT mode or the multiple TT mode. Cypress also offers the low power TetraHub (CY7C65642) optimized for low-cost designs. Contact Cypress's technical support (www.cypress.com/support) for more information on this product.

## **Document History**

**Document Title: AN1071 – Single Versus Multiple Transaction Translator**

Document Number: 001-65252

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                               |

|----------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------|

| **       | 3095718 | NMMA               | 11/26/2010         | Created spec number and updated template for an old application note that was there on the website. |

| *A       | 3229000 | AASI               | 04/15/2011         | Added information on HX2VL.                                                                         |

| *B       | 4209084 | RSKV               | 12/03/2013         | Obsolete document.                                                                                  |

|          |         |                    |                    | Completing Sunset Review.                                                                           |

In March of 2007, Cypress recataloged all of its Application Notes using a new documentation number and revision code. This new documentation number and revision code (001-xxxxx, beginning with rev \*\*\*), located in the footer of the document, will be used in all subsequent revisions

TetraHub is a trademark of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone: 408-943-2600 Fax: 408-943-4730 http://www.cypress.com/

© Cypress Semiconductor Corporation, 2010-2013. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.