# Altirra Hardware Reference Manual 2020-10-23 Edition Avery Lee

# **Table of Contents**

|    | 1.1 . Introduction                       |    |

|----|------------------------------------------|----|

|    | 1.2 . What's new in this edition         |    |

|    | 1.3 . Conventions in this manual         |    |

|    | 1.4 . Concepts                           | 15 |

| 2. | CPU                                      |    |

|    | 2.1 . Registers                          | 19 |

|    | 2.2 . Decimal mode                       | 19 |

|    | 2.3 . Cycle timing                       |    |

|    | 2.4 . Interrupts                         | 22 |

|    | 2.5 . Undocumented instructions          | 25 |

|    | 2.6 . 65C02 compatibility                | 28 |

|    | 2.7 . 65C816 compatibility               | 30 |

|    | 2.8 . 65C816 new features                | 31 |

|    | 2.9 . Examples                           | 33 |

|    | 2.10 . Further reading                   | 34 |

| 3. | System control                           | 35 |

|    | 3.1. System Reset button                 |    |

|    | 3.2 . Peripheral Interface Adapter (PIA) | 36 |

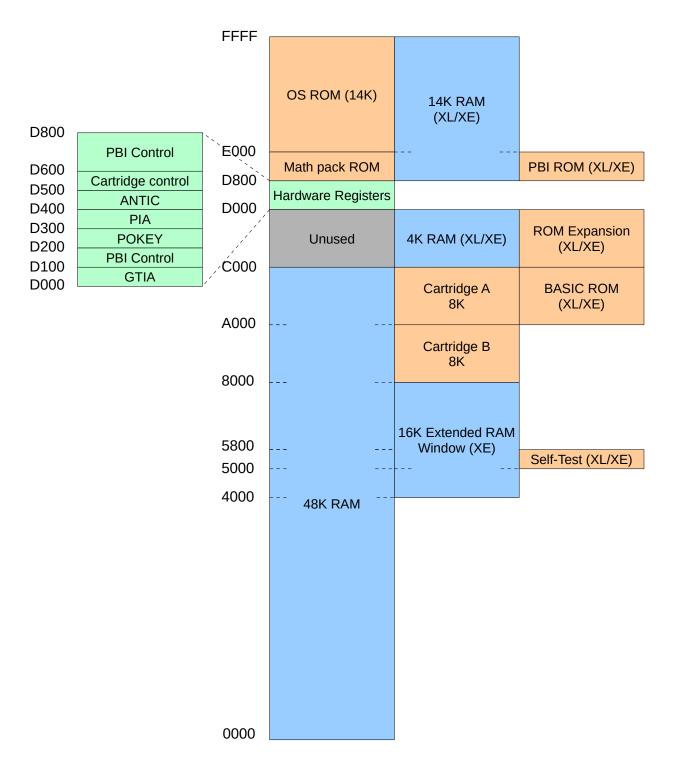

|    | 3.3 . Memory system                      | 38 |

|    | 3.4 . Bank switching                     | 40 |

|    | 3.5 . Extended memory                    | 40 |

|    | 3.6 . Miscellaneous connections          |    |

|    | 3.7 . Examples                           |    |

|    | 3.8 . Further reading                    | 44 |

| 4. | ANTIC                                    | 45 |

|    | 4.1 . Basic operation                    |    |

|    | 4.2 . Display timing                     | 47 |

|    | 4.3 . Playfield                          |    |

|    | 4.4 . Character modes                    |    |

|    | 4.5 . Mapped (bitmap) modes              |    |

|    | 4.6 . Display list                       |    |

|    | 4.7 . Scrolling                          |    |

|    | 4.8 . Non-maskable interrupts            |    |

|    | 4.9 . WSYNC                              |    |

|    | 4.10 . VCOUNT                            | 64 |

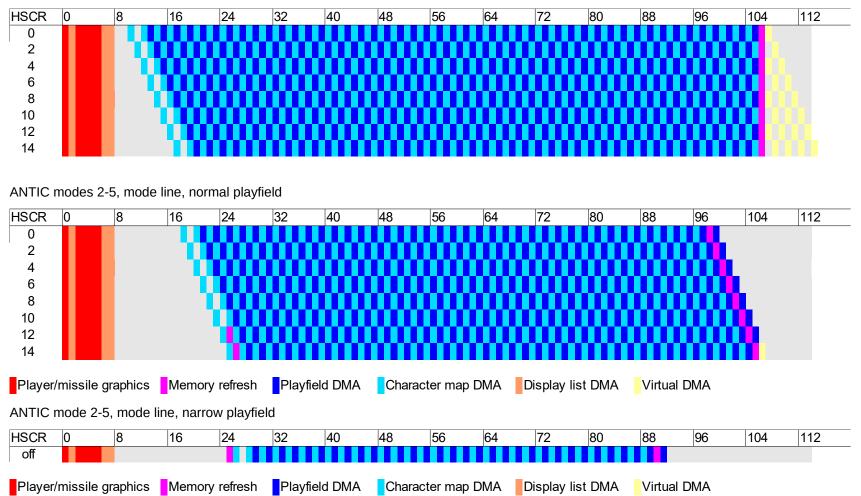

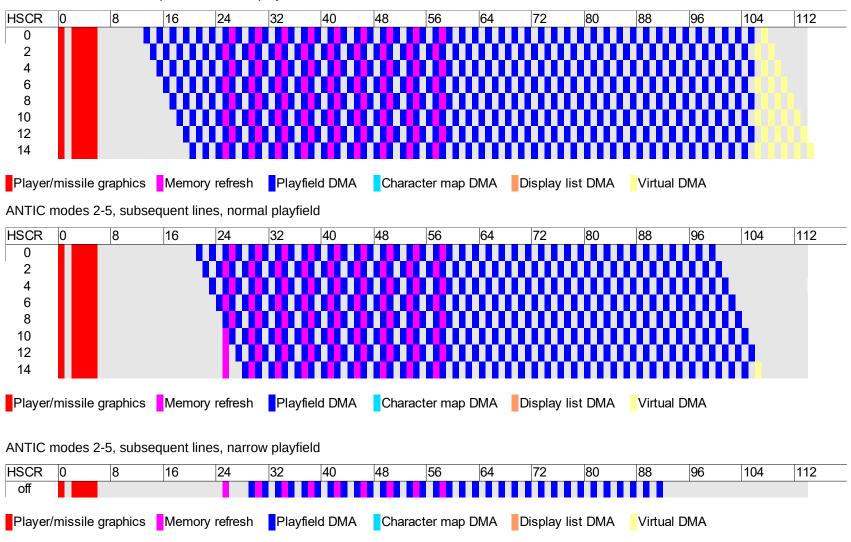

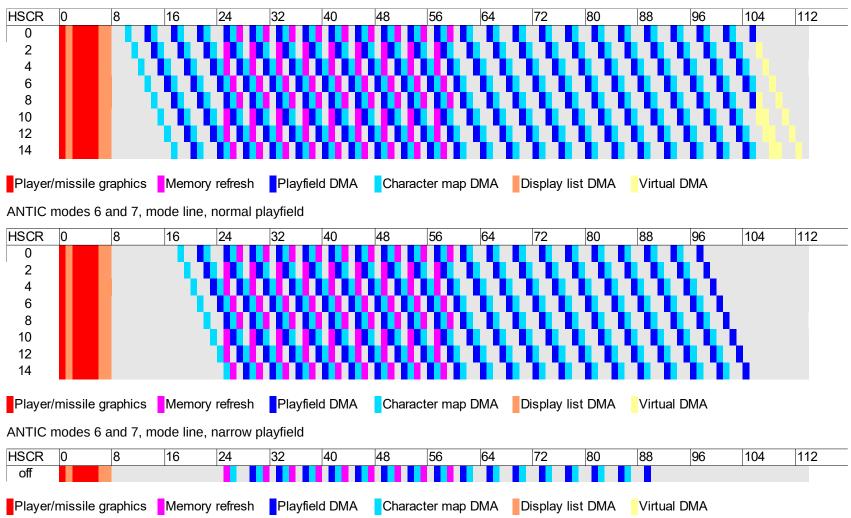

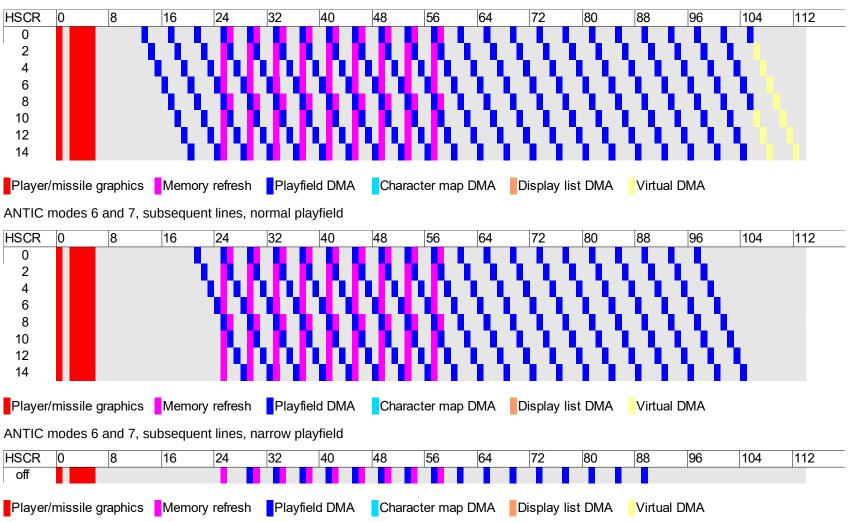

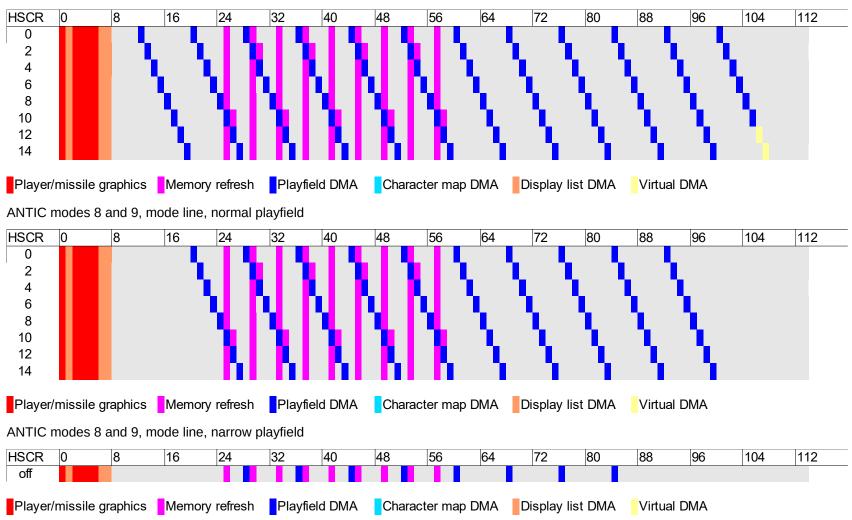

|    | 4.11 . Playfield DMA                     |    |

|    | 4.12 . Abnormal playfield DMA            | 66 |

|    | 4.13 . Player/missile DMA                | 71 |

|    | 4.14 . Scan line timing                  | 71 |

|    | 4.15 . Cycle counting example            |    |

|    | 4.16 . Examples                          | 84 |

|    | 4.17 . Further reading                   | 85 |

| 5. | POKEY                                    | 86 |

|    | 5.1 . Addressing                         | 87 |

|    | 5.2 . Initialization                     | 87 |

|    | 5.3 . Sound generation                   | 87 |

|    | 5.4 . Serial port                        | 90 |

|    | 5.5 . Clock generation                   |    |

|    | 5.6 . Noise generators                   | 98 |

|    | 5.7 . Interrupts                         | 99 |

|    |                                          |    |

|     | 5.8 . Keyboard scan                                  | 101 |

|-----|------------------------------------------------------|-----|

|     | 5.9 . Paddle scan                                    |     |

|     | 5.10 . Examples                                      |     |

|     | 5.11 . Further reading                               | 107 |

| 6.  | CTIA/GTIA                                            |     |

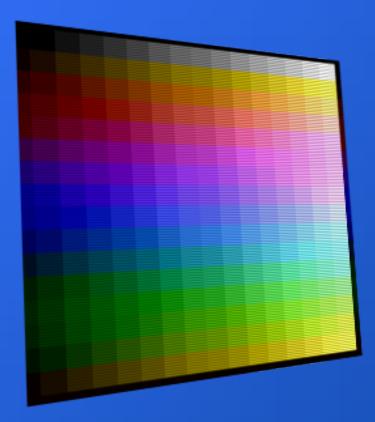

| • • | 6.1 . Color encoding                                 |     |

|     | 6.2 . Artifacting                                    |     |

|     | 6.3 . Player/missile graphics                        |     |

|     | 6.4 . Collision detection                            |     |

|     | 6.5 . Priority control                               |     |

|     | 6.6 . High resolution mode (ANTIC modes 2, 3, and F) |     |

|     | 6.7 . GTIA special modes                             |     |

|     | 6.8 . Cycle timing                                   | 121 |

|     |                                                      | 120 |

|     | 6.9 . General purpose I/O                            |     |

| -   | 6.10 . Further reading                               |     |

| 1.  | Accessories                                          |     |

|     | 7.1 . Joystick                                       |     |

|     | 7.2 . Paddle                                         |     |

|     | 7.3 . Mouse                                          |     |

|     | 7.4 . Light Pen/Gun                                  |     |

|     | 7.5 . CX-85 Numerical Keypad                         |     |

|     | 7.6 . CX-20 Driving Controller                       |     |

|     | 7.7 . CX-21/23/50 Keyboard Controller                |     |

|     | 7.8 . XEP80 Interface Module                         | 131 |

|     | 7.9 . Corvus Disk System                             | 145 |

| 8.  | Cartridges                                           | 147 |

|     | 8.1 . Cartridge port                                 |     |

|     | 8.2 . Atarimax flash cartridges                      |     |

|     | 8.3 . Atarimax MyIDE-II                              |     |

|     | 8.4 . SIC!                                           |     |

|     | 8.5 . SIDE 1 / SIDE 2                                |     |

|     | 8.6 . Corina                                         |     |

|     | 8.7 . R-Time 8                                       |     |

|     | 8.8 . Veronica                                       |     |

| ٥   | Serial I/O (SIO) Bus                                 |     |

| 9.  | 9.1 . Basic SIO protocol                             | 162 |

|     | 9.2 . Polling                                        |     |

|     | 9.2 . Politing                                       |     |

|     |                                                      |     |

|     | 9.4 . 1030 Modem                                     | -   |

|     | 9.5 . SX212 Modem                                    |     |

|     | 9.6 . R-Verter                                       |     |

|     | 9.7 . 410/1010 Program Recorder                      |     |

|     | 9.8 . MidiMate                                       |     |

|     | 9.9 . Pocket Modem                                   | 178 |

| 10  | . Disk drives                                        | 180 |

|     | 10.1 . Introduction                                  | 181 |

|     | 10.2 . Basic protocol                                |     |

|     | 10.3 . Extended protocols                            | 190 |

|     | 10.4 . Commands                                      |     |

|     | 10.5 . Timing                                        |     |

|     | 10.6 . Anomalies                                     |     |

|     | 10.7 . 6532 RIOT                                     |     |

|     | 10.8 . 177X/179X/279X FDC                            |     |

|     | 10.9 . 810 disk drive                                |     |

|     |                                                      | -01 |

-

| 10.10 . 810 hardware                            | 210 |

|-------------------------------------------------|-----|

| 10.11 . Happy 810                               | 213 |

| 10.12 . 810 Turbo                               | 215 |

| 10.13 . 815 disk drive                          | 217 |

| 10.14 . 815 hardware                            |     |

| 10.15 . 1050 disk drive                         |     |

| 10.16 . 1050 hardware                           |     |

| 10.17 . US Doubler                              |     |

| 10.18 . Happy 1050                              |     |

| 10.19 . I.S. Plate                              |     |

| 10.20 . XF551 disk drive                        |     |

| 10.20 . XF 551 hardware                         |     |

| 10.22 . Indus GT disk drive                     |     |

| 10.22 . Indus GT lask arve                      |     |

| 10.23 . Indus GT hardware                       |     |

| 10.24 . Ar Robot hardware                       |     |

| 10.25 . Percom AT88-S1                          |     |

| 10.26 . Percom AT88-SPD/S1PD                    |     |

|                                                 |     |

| 10.28 . Amdek AMDC-I/II                         |     |

| 11 . Parallel Bus Interface                     |     |

| 11.1 . Introduction                             |     |

| 11.2 . Common memory map                        |     |

| 11.3 . ICD Multi I/O (MIO)                      |     |

| 11.4 . CSS Black Box                            |     |

| 11.5 . Atari 1090 80 Column Video Card          |     |

| 12 . Internal devices                           |     |

| 12.1 . Introduction                             |     |

| 12.2 . Covox                                    |     |

| 12.3 . Ultimate1MB                              |     |

| 12.4 . VideoBoard XE                            |     |

| 12.5 . APE Warp+ OS 32-in-1                     |     |

| 12.6 . Bit-3 Full-View 80                       |     |

| 13. 5200 SuperSystem                            | 294 |

| 13.1 . Introduction                             |     |

| 13.2 . Differences from the 8-bit computer line | 295 |

| 13.3 . Controller                               | 296 |

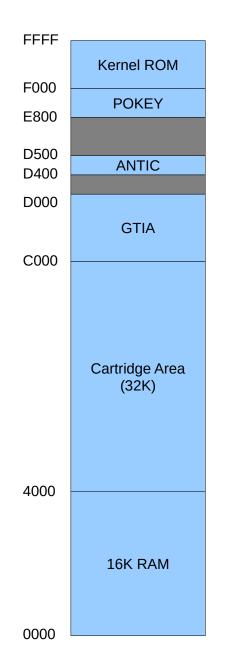

| 13.4 . 5200 Memory map                          | 298 |

| 14 . Reference                                  | 299 |

| 14.1 . Memory map                               | 300 |

| 14.2 . Register list                            | 301 |

| 14.3 . GTIA registers                           |     |

| 14.4 . POKEY registers                          |     |

| 14.5 . PIA registers                            |     |

| 14.6 . ANTIC registers                          |     |

| 14.7 . Register listing                         |     |

| 15. Bibliography                                |     |

| A. Polynomial Counters                          |     |

| B. Physical Disk Format                         |     |

| B.1 . Raw geometry                              |     |

| B.2 . Bit encoding                              |     |

| B.2 . Bit encounty<br>B.3 . Address field       |     |

| B.4 . Data field                                |     |

|                                                 |     |

| B.5 . CRC algorithm                             |     |

| C . Analog Video Model                          |     |

4

| C.1 . Introduction             |     |

|--------------------------------|-----|

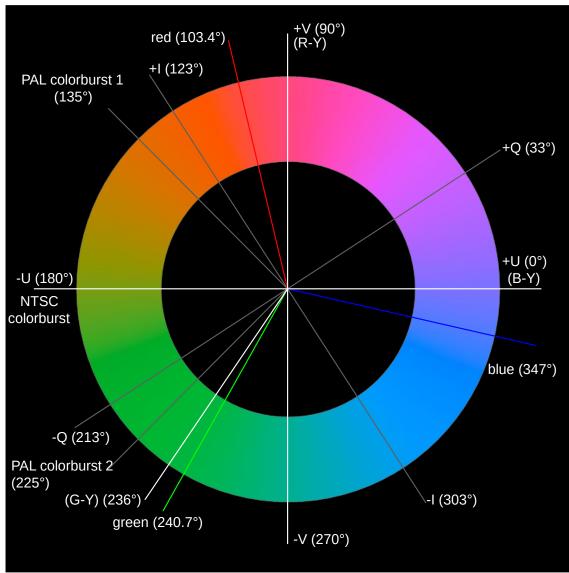

| C.2 . NTSC color encoding      | 371 |

| C.3 . NTSC artifacting         | 379 |

| C.4 . PAL color encoding       | 382 |

| C.5 . PAL artifacting          | 384 |

| D. Analog Audio Model          | 386 |

| D.1 . Introduction             |     |

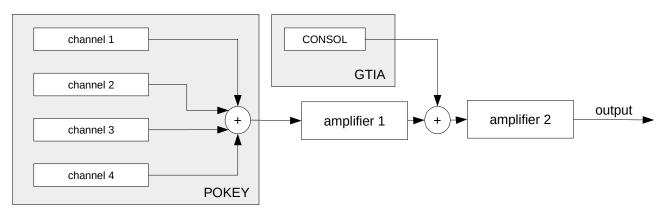

| D.2 . POKEY output             | 387 |

| D.3 . First amplifier stage    | 388 |

| D.4. External signal sum point | 389 |

| D.5 . Second amplifier stage   | 389 |

| D.6 . Final output             | 391 |

| E. Quick Reference             | 392 |

| E.1 . CPU opcode table         | 393 |

# **Index of Tables**

| Table 1: NMOS 6502 opcode table                                                                      | 25  |

|------------------------------------------------------------------------------------------------------|-----|

| Table 2: 65C02 opcode table                                                                          | 29  |

| Table 3: 65C816 opcode table                                                                         | 30  |

| Table 4: Some extended memory configurations                                                         | 42  |

| Table 5: Typical power-up values for ANTIC registers                                                 | 47  |

| Table 6: ANTIC display timing                                                                        |     |

| Table 7: DMA and shift clock rates by mode                                                           | 67  |

| Table 8: Serial port timing modes                                                                    | 92  |

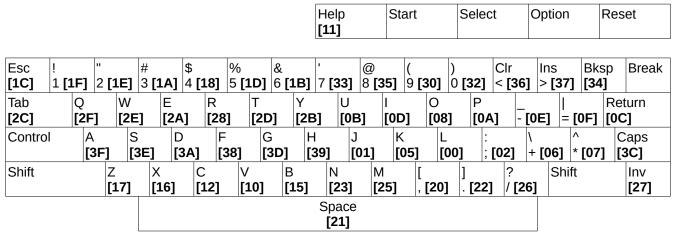

| Table 9: Key codes (scan matrix layout)                                                              |     |

| Table 10: Key codes (130XE keyboard layout)                                                          | 102 |

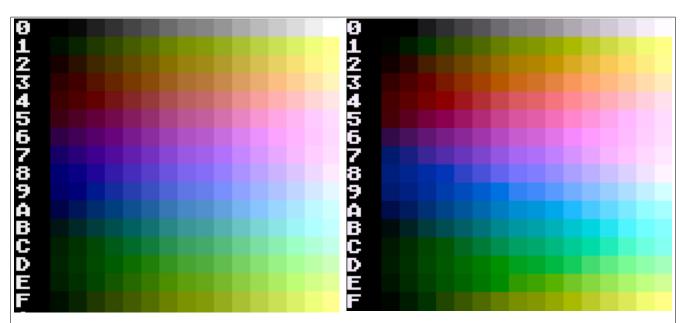

| Table 11: PAL GTIA color encodings                                                                   |     |

| Table 12: Results of various size changes in the middle of a player image                            |     |

| Table 13: Priority logic outputs for unusual priority modes                                          | 119 |

| Table 14: ANx bus encodings                                                                          | 123 |

| Table 15: Timing for mid-screen writes to GTIA registers                                             | 124 |

| Table 16: CX-85 keypad to PORTA bit pattern mapping                                                  | 130 |

| Table 17: Keyboard Controller key matrix                                                             | 130 |

| Table 18: Character bit to block graphics mapping                                                    | 135 |

| Table 19: XEP80 Timing Register Values                                                               | 144 |

| Table 20: Corvus Interface modes                                                                     | 145 |

| Table 21: SIDE 1/2 register map                                                                      | 154 |

| Table 22: SIO device IDs                                                                             | 164 |

| Table 23: Peripheral Handler Relocation Record Types                                                 | 169 |

| Table 24: 1030 Modem hardware commands.                                                              | 174 |

| Table 25: SX212 supported commands                                                                   |     |

| Table 26: Disk drive status frame                                                                    | 189 |

| Table 27: Disk drive transfer rates                                                                  | 191 |

| Table 28: PERCOM Block Contents                                                                      |     |

| Table 29: Detected Percom blocks for various disk drives and formats                                 | 193 |

| Table 30: Disk drive transmit timings by firmware                                                    |     |

| Table 31: Disk drive step rate timings                                                               | 197 |

| Table 32: Disk format strategies by drive type                                                       |     |

| Table 33: Track sector layouts by drive type and format                                              |     |

| Table 34: FDC status codes for various read sector conditions                                        |     |

| Table 35: Disk drive behavior on Read Sector command with drive door/latch open and no disk inserted |     |

| Table 36: Ideal 810 sector read timing                                                               |     |

| Table 37: Step rates for various FDC models                                                          |     |

| Table 38: Head load delays for various FDC models                                                    |     |

| Table 39: 810 drive firmware revisions                                                               |     |

| Table 40: 810 memory map                                                                             | 211 |

| Table 41: 810 RIOT I/O port assignments                                                              |     |

| Table 42: Happy 810 rev.7 drive mode bits                                                            |     |

| Table 43: 810 Turbo memory map                                                                       |     |

| Table 44: 815 memory map                                                                             |     |

| Table 45: 815 RIOT I/O port assignments                                                              |     |

| Table 46: 1050 returned ROM signatures                                                               |     |

| Table 47: 1050 memory map                                                                            |     |

| Table 48: 1050 RIOT I/O port assignments                                                             |     |

| Table 49: Happy 1050 drive mode bits                                                                 |     |

| Table 50: XF551 drive status flags                                                                   |     |

| Table 51: XF551 PERCOM configuration block values                                                    |     |

|                                                                                                      |     |

| Table 52: XF551 8040 I/O port connections         Table 53: Indus GT stock firmware revisions | 237 |

|-----------------------------------------------------------------------------------------------|-----|

|                                                                                               | 238 |

| Table 54: Commonly used Indus GT uploadable code fragments                                    |     |

| Table 55: Indus GT memory map                                                                 | 239 |

| Table 56: Indus GT status 1 port signals                                                      | 240 |

| Table 57: Indus GT status 2 port signals                                                      |     |

| Table 58: ATR8000 input port assignments                                                      | 242 |

| Table 59: ATR8000 drive control port layout (OUT 30-3FH)                                      | 243 |

| Table 60: ATR8000 SIO status port layout (IN 70-7FH)                                          | 244 |

| Table 61: ATR8000 printer status port layout (IN 20-2FH)                                      |     |

| Table 62: Percom RFD firmware revisions                                                       | 245 |

| Table 63: Percom RFD-40S1 memory map                                                          | 245 |

| Table 64: Percom AT88-S1 memory map                                                           | 247 |

| Table 65: Percom AT88-S1 PIA connections                                                      | 247 |

| Table 66: Percom AT88-SPD/S1PD memory map                                                     | 248 |

| Table 67: Percom AT88-SPD/S1PD PIA connections                                                | 249 |

| Table 68: Amdek AMDC-I/II memory map                                                          | 252 |

| Table 69: MIO memory map                                                                      | 256 |

| Table 70: Black Box memory map                                                                |     |

| Table 71: 80CVC hardware registers                                                            |     |

| Table 72: VBXE extended display list (XDL) entry format                                       | 276 |

| Table 73: VBXE overlay priority bits                                                          | 278 |

| Table 74: VBXE attribute map block layout                                                     |     |

| Table 75: VBXE blitter setup block                                                            |     |

| Table 76: VBXE blit modes                                                                     | 282 |

| Table 77: VBXE blitter speeds                                                                 | 283 |

| Table 78: VBXE registers                                                                      |     |

| Table 79: Bit-3 Full-View 80 \$D508 register bits                                             | 292 |

| Table 80: Measured signal levels for sync and all luminances                                  | 374 |

| Table 81: NTSC saturation ratios                                                              | 376 |

| Table 82: Measured artifacting delays                                                         |     |

| Table 83: CPU opcode table                                                                    | 394 |

# Index of Figures

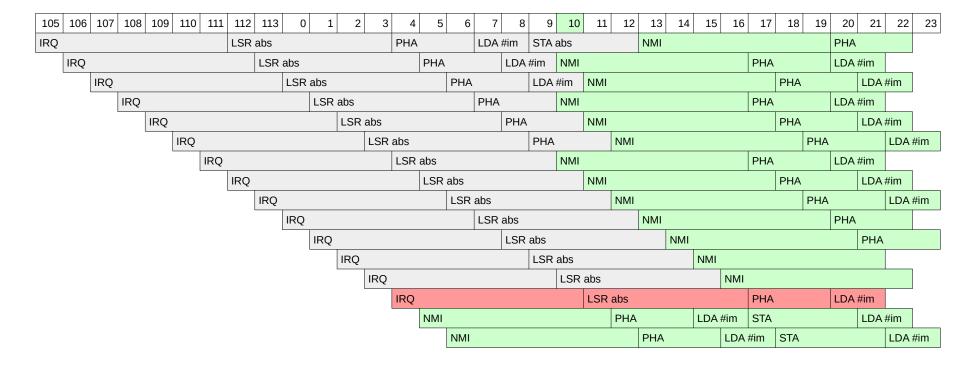

| Figure 1: Effects of overlapping IRQ/NMI timing             | 24  |

|-------------------------------------------------------------|-----|

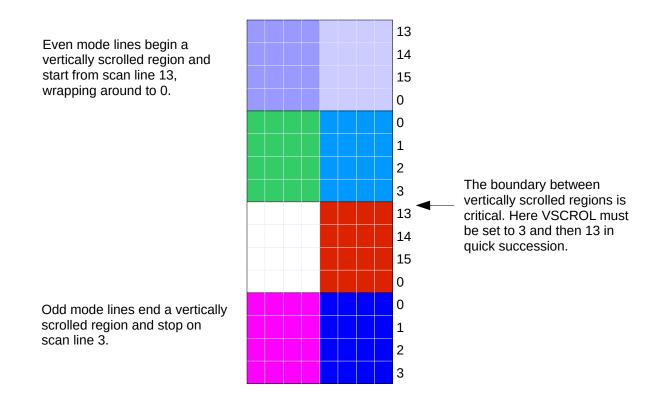

| Figure 2: Effect of vertical scrolling on mode lines        | 57  |

| Figure 3: Abusing vertical scrolling in the "GTIA 9++" mode | 59  |

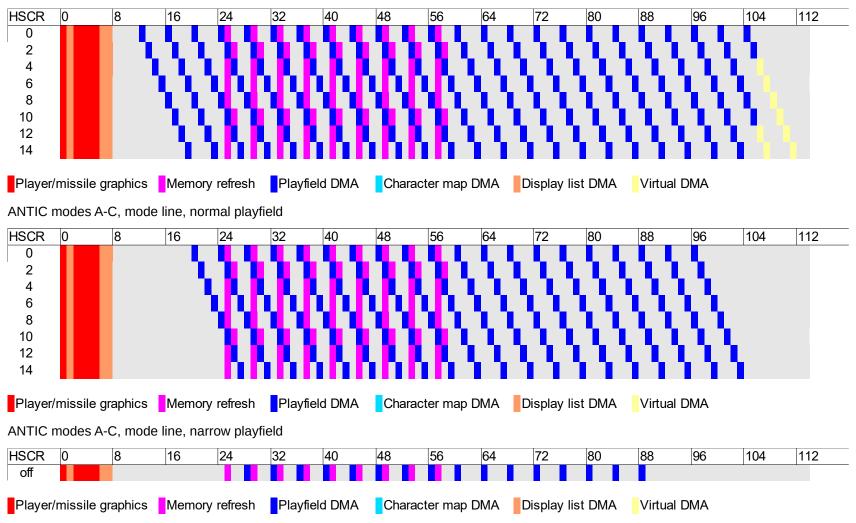

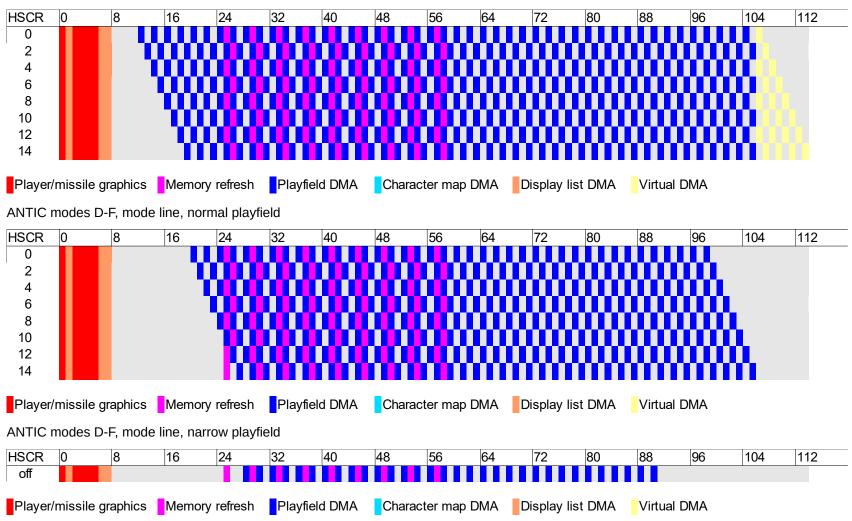

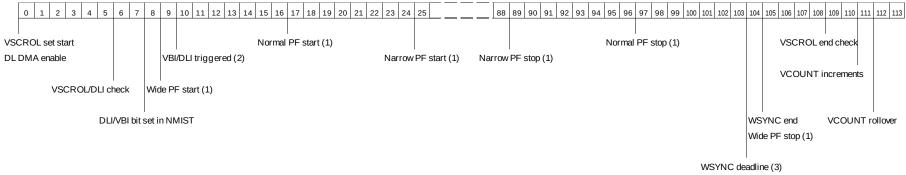

| Figure 4: ANTIC event timing                                |     |

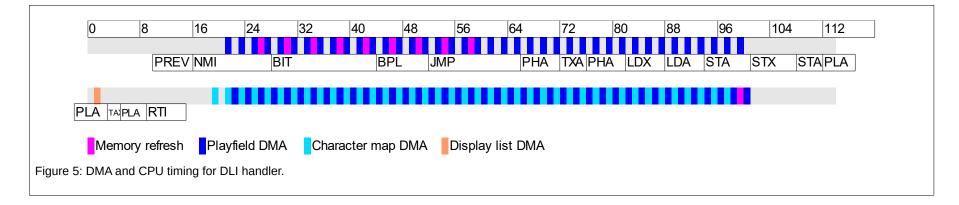

| Figure 5: DMA and CPU timing for DLI handler                | 83  |

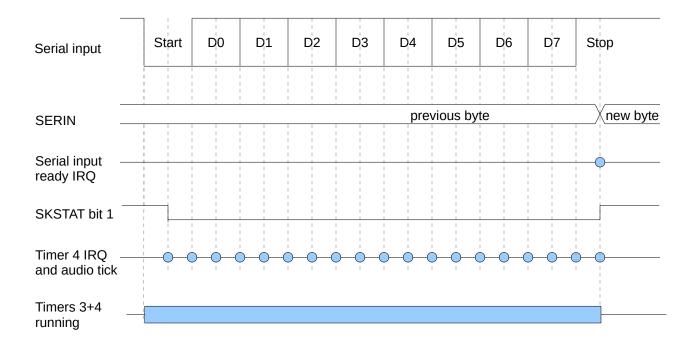

| Figure 6: POKEY asynchronous serial receive timing          | 95  |

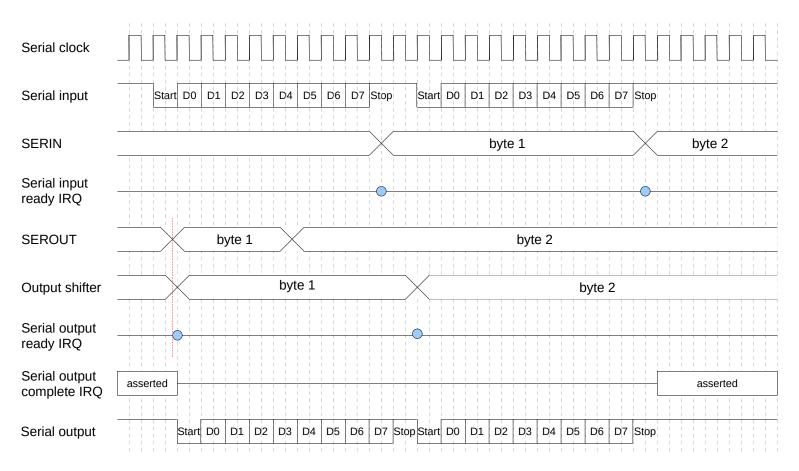

| Figure 7: POKEY synchronous serial receive/transmit timing  | 96  |

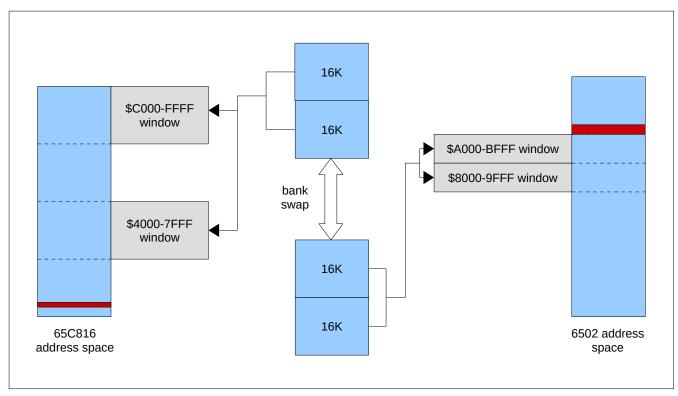

| Figure 8: Veronica memory layout                            | 158 |

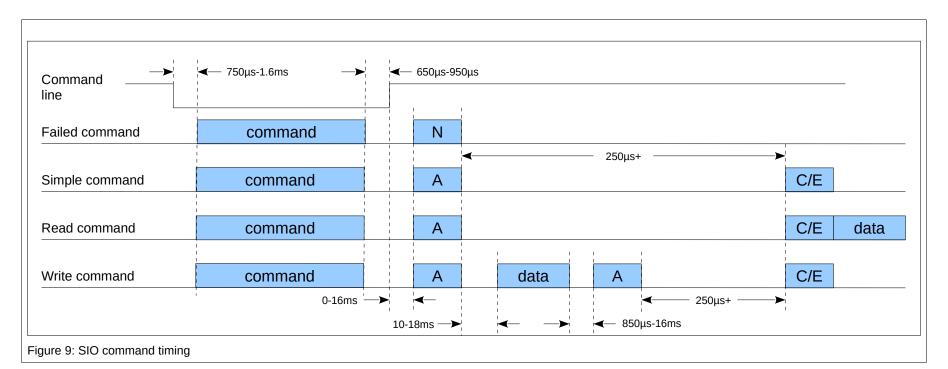

| Figure 9: SIO command timing                                | 165 |

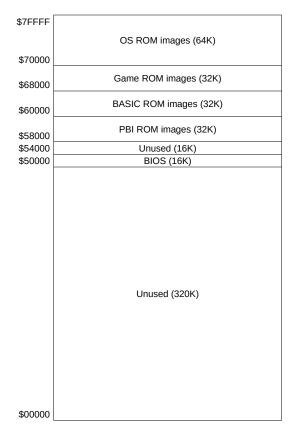

| Figure 10: Ultimate1MB flash memory map                     |     |

| Figure 11: YIQ/YUV color space relations                    | 371 |

| Figure 12: Effect of color correction on computed palette   | 376 |

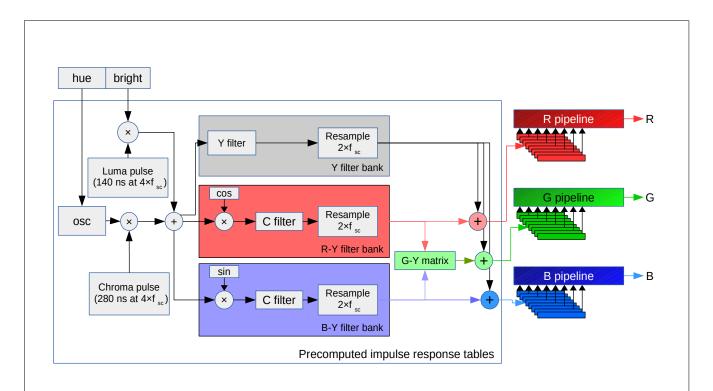

| Figure 13: Altirra NTSC high artifacting pipeline           |     |

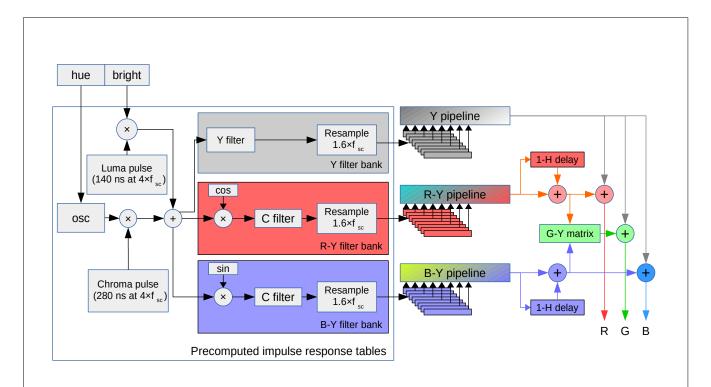

| Figure 14: Altirra PAL high artifacting pipeline            |     |

| Figure 15: Analog audio block model                         |     |

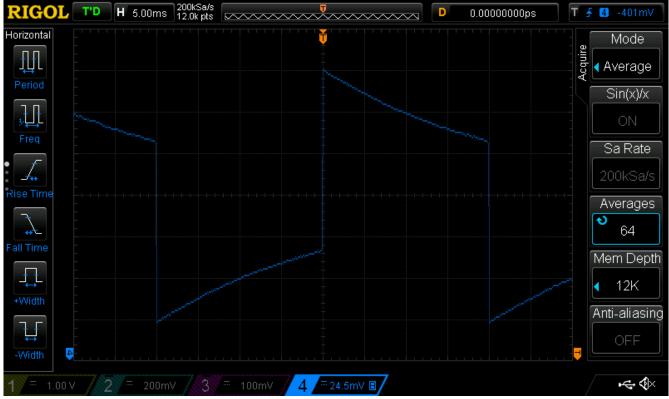

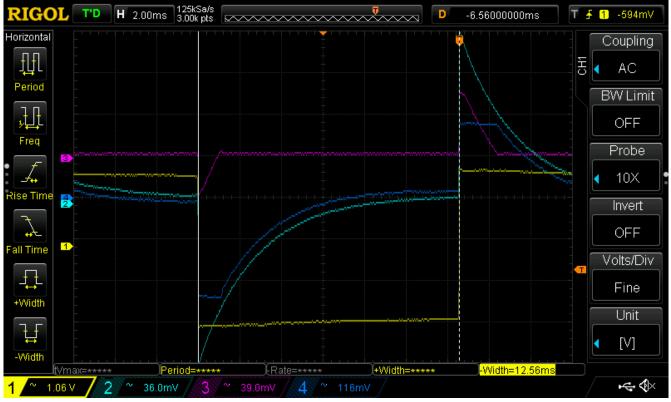

| Figure 16: Decay from second stage amplifier                |     |

| Figure 17: Dynamic clamping effect                          |     |

|                                                             |     |

#### Altirra Hardware Reference Manual

-

Copyright © 2009-2020 Avery Lee, All Rights Reserved.

Permission is granted to redistribute this document in verbatim form as long as it is done free of charge and for non-commercial purposes.

All trademarks are the property of their respective owners.

While the information in this document is presumed correct, no guarantee is provided as to its accuracy or fitness for a particular use.

# **1.1 Introduction**

This document describes the hardware programming model used by Altirra, an emulator for the Atari 8-bit series of home computers, including the 400, 800, 600XL, 800XL, 1200XL, 130XE, and XEGS models. Although the emulator provides a virtual programming environment, it is intended to mimic the actual hardware. This document attempts to describe the hardware in detail as the target to which the emulator aspires to imitate. Some of this information has been collected from both official and unofficial sources, and some of it has been determined by hand through testing on a real, still functioning Atari 800XL.

While I've spent a lot of time tracking down details myself, I have to acknowledge the substantial amount of literature already available which provided background for this document. First and foremost, I'm indebted to the technical staff behind the *Atari Home Computer System Hardware Manual*, which did a very good job of describing the behavior and programming specifications for the official functionality in the Atari hardware, and which should be considered required reading prior to this document. Similar shout-outs go to the authors of Atari's *OS Manual*, which similarly documents the software side, and to Ian Chadwick and his *Mapping the Atari, Revised Edition*, which contains the most detailed and complete memory map of the Atari I know of.

If you have the time and inclination, please check out my Altirra emulator, available at the following web address:

http://www.virtualdub.org/altirra.html

-- Avery Lee

# **1.2** What's new in this edition

#### This release

- Disk drives

- Fixed swapped PB0 and PB7 definitions for 1050 drives.

- Added behavior of various drives with no disk inserted.

- Clarified FDC handling of the head/side address field value.

- Added firmware revision information for 1050, Indus GT, and Percom RFD.

- Added Atari 815.

- Added Percom AT88-S1 and AT88-SPD.

- Internal devices

- Added Bit-3 Full-View 80.

- Added Atari 1090 80 Column Video Card.

#### 2019-12-30 release

- System control

- Fixed a typo in the PAL clock rate.

- ANTIC

- Timing and behavior for the 400/800 System Reset NMI, even on XL/XE computers.

- GTIA

- Clarified listed behavior for mode 9 combining with the fifth player (PF3) and for mode 11 regarding unusual COLBK values.

- POKEY

- Fixed a typo in the keyboard layout for the Return key.

- Disk drives

- Fixed 810 port B entries being listed in reversed order.

- Added information on the 810 Turbo, Astra 1001 / The "One", and Amdek AMDC-I/II.

- Added info on specific behaviors of the 6532 RIOT and 177X/277X floppy drive controllers.

- Added info on Happy 1050 US Doubler emulation data corruption bug.

- Added info on XF551 format behavior.

- Internal devices

- Corrected VBXE blitter pattern width bitfield from 7 to 6 bits.

- Added section on APE Warp+ 32-in-1.

• New appendices for analog video and audio models.

#### 2018-08-12 release

- CPU: Clarified exact rules for when a branch crosses a page.

- CPU: Fixed some erroneous illegal instructions in the 6502 opcode chart.

- ANTIC: Fixed wrong modes being listed for 512 byte / 1K character set size.

- POKEY: Additional information about high-pass filter timing.

- GTIA:

- New section on NTSC and PAL artifacting.

- Clarified behavior of GR.9/GR.11 with fifth player or background having non-zero luma for GR.9 or hue for GR.11.

- Disk: Added information about task sequencing in disk drive controllers, I.S. Plate, sector interleaving order used by disk drive firmware, XF551 FDC error codes, long sector behavior, 810 revision B firmware, US Doubler hardware and commands, fixed incorrect sector ranges for XF551 back side encoding.

#### 2017-05-17 release

- Additional light pen information.

- Rewritten and expanded section on POKEY's serial port hardware, including precise timing diagrams.

- MyIDE-II CompactFlash reset behavior.

- SX212 power-on behavior.

- New chapter on disk drives, including information on the Happy 810, Happy 1050, ATR8000, Percom RFD-40S1, and the hardware for the 810, 1050, XF551, and Indus GT.

#### 2016-03-25 release

- 65C816 opcode table.

- 800 floating I/O data bus.

- POKEY: Additional details on serial port behavior and keyboard and paddle scans.

- Additional XEP-80 details.

- Controllers: CX-20 Driving Controller, CX-21/23/50 Keyboard Controller.

- New device info: Indus GT disk drive, Corvus Disk Interface, Pocket Modem.

- 810 and 1050 updates: long sector behavior, FDC status.

- SIDE 2 corrections.

- Physical disk format: sector length behavior.

#### 2015-07-05 release

- System: Added information about floating PIA port B bits.

- CPU: Added new sections on new 65C816 functionality, undocumented 6502 opcodes, and opcode tables.

- ANTIC: New sections on display timing, effects of extending the height of mode lines.

- POKEY: Added info about keyboard conflicts.

- GTIA: Added info about color generation.

- New chapter on cartridges: AtariMax, SIC!, SIDE, Corina, R-Time 8, Veronica.

- New chapter on Parallel Bus Interface devices: Black Box, Multi I/O.

- Additional device information: R-Verter, MidiMate, Ultimate1MB, VideoBoard XE.

- Additional XEP-80 commands.

- New appendices on polynomial counters and physical floppy disk formats.

#### 2014-04-27 release

- CPU: Added section on 65C02 and 65C816 compatibility issues.

- System Control: Added information on Parallel Bus Interface IRQs.

- POKEY: Added keyboard scan code table.

- GTIA: Updated with new table of player/missile/playfield priority conflicts and information about priority conflicts in GTIA modes.

- Serial I/O: Now has its own chapter, including information about type 0-4 polling and device-provided relocatable loaders.

- 850: Corrected errors in the description of the Write command, expanded description of the Stream command, and added sections on the 850 bootstrap process.

- Disk: Added more details on 810 FDC controller status and command error conditions, and a new section about disk anomalies used by protection mechanisms.

- New section on XEP80 device.

- Reference: Updated to note guarantees on PAL register bits, and fixed errors in PACTL listing and register quick reference.

#### 2013-05-14 release

- ANTIC updates:

- Bus activity during WSYNC.

- Abnormal playfield DMA.

- GTIA updates:

- Border behavior in mode 10.

- Player/missile shift details and lockup state.

- POKEY updates:

- Polynomial counter patterns and timing behaviors.

#### 2012-09-15 release

- Cycle numbers have been readjusted back so that cycle 0 is once again the missile DMA fetch.

- PIA corrections and interrupt behavior.

- CPU interrupt acknowledge timing.

- Parallel Bus Interface (PBI) information.

- XEGS game ROM selection and keyboard sense.

- ANTIC updates:

- Virtual playfield DMA

- Vertically scrolled jump instructions

- VSCROL vs. DLI timing

- POKEY updates:

- Additional serial port initializing and timing information

- GTIA updates:

- Lo-res mode 10 anomaly

- Additional peripheral documentation:

- CX-85 numerical keypad

- 850 Interface Module

- 1030 Modem

- 810, 1050, and XF551 Disk Drives

- Generic SIO protocol

- Fixed backwards serial port and keyboard overrun bits in SKCTL reference.

- Fixed swapped Control and Shift bits in KBCODE reference.

- Removed incorrect location of international character set from memory map; this is an OS convention anyway, not inherent in hardware.

#### 2010-11-23 release

- 5200 SuperSystem documentation.

- BRK anomalies, decimal mode, and I flag timing.

- ANTIC horizontal scrolling bug.

- NMIST timing.

- Temperature sensitive POKEY and GTIA behaviors.

- Keyboard scan behavior.

- All scan line cycle numbers have been corrected to match the horizontal position counter (one less than previous).

# **1.3** Conventions in this manual

#### Number format

Unless specified, numbers without a prefix are given in base 10 (decimal). Numbers prefixed by \$ are given in base 16 (hexadecimal). In sections that describe Z80-based devices, Intel-style hex conventions are used instead with hex numbers ending in H, i.e. 50H.

### Scan line timing

A significant number of hardware events with interesting timing occur relative to a particular offset within the timing of a *scan line*, which is one horizontal sweep of the display CRT beam. Many activities within the hardware occur at specific positions within a scan line and it is frequently useful to synchronize the CPU to scan line timing. There are 114 machine cycles for each scan line.

There is no program visible horizontal position counter in the Atari hardware. To make it easier to refer to specific offsets within a scan line, the cycles within a scan line are numbered from 0-113 in this manual, where cycle 0 corresponds to the missile DMA at the beginning of a scan line. This is also approximately the beginning of horizontal sync in the output video signal. Altirra also uses this convention in its debugger.

#### Deadlines

Sometimes it is necessary for the CPU to write to a hardware register before or after a particular deadline to produce a desired behavior. For purposes here, A CPU write to a register *on cycle N* satisfies a requirement to write *by cycle N*, *before cycle N+1*, and *after cycle N-1*. The cycle number is always in terms of the actual write cycle from the CPU and not the write instruction. For instance, an INC NMIRES instruction that begins execution on cycle 90 writes to NMIRES at cycles 95 and cycle 96, assuming no DMA contention.

#### **Event timing**

An event observable by a register is said to occur on a particular cycle when that is the first cycle in which a read of that register reflects the event. For instance, if an interrupt bit activates in IRQST on cycle 95 of a scan line, it means that reading the register on or prior to cycle 94 will not show the interrupt and reading it on or after cycle 95 will.

In most cases, event timing is described in this manual in terms of when it becomes visible to program execution. For instance, interrupts are described according to when the 6502 can either sense a change in interrupt status or begins executing an interrupt routine, and not when the IRQ signal on 6502 is asserted. An exception is externally visible outputs, such as video, audio, and I/O.

#### Active low and active high signals

In hardware designs, the signals may be designated as either *active low* or *active high* depending on the interpretation of the circuit design. The IRQ line on the CPU, for instance, is an active low signal and is activated by pulling the signal line to the low state. On the other hand, the RD5 signal from the cartridge that maps \$A000-BFFF is active high, and is pulled up to +5V to signal that cartridge ROM is present.

To avoid confusion, this manual uses the terms **asserted** and **negated** to indicate the state of a signal line. An active low signal is asserted in the low state, and negated in the high state; an active high signal is asserted in the high state and negated in the low state.

# **1.4 Concepts**

#### **Program visible behavior**

A behavior or effect in the hardware which can be detected by a running program is *program visible*. Most of the hardware behavior described in this manual is program visible. For instance, the serialization behavior of the player/missile registers in GTIA is program visible because it can be detected through the collision registers. Any program-visible behavior is detectable by program code and can therefore be checked to detect incomplete emulation or broken hardware.

In contrast, a non program visible behavior cannot be detected by a running program: there is no way for an Atari program to detect the colors produced by the GTIA priority logic unless external hardware provides a loopback path.

#### Byte order (endian)

The 6502 is a little endian processor and therefore writes words with the lower order byte at the lower address of the byte pair. The hardware follows the same convention: in the few cases where word registers exist or words are fetched, the byte with the lower address is the lower order byte.

The opposite case is a big endian convention, where the higher order byte comes before the lower order byte. The 6809 is an example of a CPU that uses big endian byte ordering, and this endianness is also used in Percom block data because the convention originated in Percom's 6809-based disk drives.

#### **Bit order**

Within a byte, bit 7 is the most significant bit (MSB), and bit 0 is the least significant bit (LSB). A left shift moves bits toward the MSB from the LSB, and is equivalent to multiplying by a power of two.

Whenever data in a byte represents graphics patterns, the left-most (MSB) pixel is displayed on the left side on screen. Wider two-bit and four-bit pixels are stored with the same bit ordering within a pixel, allowing arithmetic operations to function on those pixels.

A *bit reversal* or *reverse bits* operation flips the order of the bits, exchanging bits 0 and 7, bits 1 and 6, etc. This has a few applications, including horizontally flipping 1-bit playfield or player/missile graphics, and compensating for different shift orders in serial protocols.

#### Address alignment

The timing of certain CPU operations and the behavior of DMA by ANTIC can depend on the addresses of bytes within a block of memory. The start of a block of memory is said to be aligned to a particular boundary if it is a multiple of that value. For instance, the address \$0800 is aligned to a 1K boundary because \$0800 is divisible by a 1K block size (\$0400 bytes). The address \$0A00, however, is not.

A memory block crosses an alignment boundary if the addresses of the first and last bytes result in different values when divided by the alignment block size. A 40 byte block at \$090A-0931 is contained within a 1K boundary, whereas \$07FF-0826 crosses the 1K boundary at \$0800. There are two specific behaviors associated with crossing such a boundary. One is that the 6502 sometimes requires an extra cycle when boundary is crossed; another is that the 6502 or ANTIC may fail to cross an alignment boundary and wrap addresses within the alignment block instead.

A *page* is a 256 byte block of memory aligned on a 256 byte boundary. Many operations in the 6502 require accesses to specific pages or require extra cycles when indexing causes address arithmetic to produce a final

address in a different page. Two 16-bit addresses have the same page if their first two hex digits are the same, i.e. \$A900 and \$A947.

#### **Read-only and write-only registers**

Most registers in the hardware are either read-only or write-only: you cannot read a write-only register or write to a read-only register. The address locations are also often shared between different read-only and write-only registers, meaning that an attempt to use an unsupported memory operation will actually access the wrong register. For instance, although the GTIA's HPOSP0 register is set by writing to \$D000, it can't be read at that address; attempting to read \$D000 gives MOPF instead.

There are a few notable exceptions where registers are read/write, such as CONSOL in GTIA and the data direction registers in the PIA.

Because not being able to read back write-only registers makes saving and restoring registers difficult, the OS maintains a number of *shadow registers* in the kernel database to allow reading back the value of those registers. By convention, the shadow register is updated whenever the hardware register is updated, and so any code that needs to read the hardware register can use the shadow register to do so. The downside is that this requires an additional write for every update to the hardware register.

#### Strobe registers

Some hardware registers, such as POTGO and WSYNC, are strobe registers. These registers trigger an action in the hardware when written by the CPU. The value written to the register is irrelevant and ignored, and the strobe is activated even if the same value is written multiple times.

There are also registers that will trigger changes on a read cycle. The PIA data registers are examples, as reading them clears pending interrupts. Similarly, some cartridge banking hardware only decodes addresses without checking the read/write line and thus respond to a read by switching cartridge banks.

#### Latched (sticky) bits

Latched bits are activated when an event occurs and stay in that state until reset. Most of the interrupt status bits in IRQST work that way, asserting IRQ on the CPU until the interrupt is acknowledged.

#### Incomplete address decoding (aliasing or mirroring)

Address decoding is the hardware process of determining if a memory address corresponds to a particular device. A device with full address decoding responds only to the specific addresses it is designed. For efficiency reasons, many hardware devices on the Atari only partially decode addresses by checking a subset of address bits. An example is the PIA, which only contains four addressable locations but is assigned a 256 byte region at \$D300-D3FF. Because bits 2-7 of the address are ignored, the PIA is mirrored 64 times within this address space. This is also called *aliasing*, because two or more addresses serve as aliases for the same memory location.

Although all of the mirror addresses of a hardware register are equivalent, there is typically still a *canonical* address associated with that register, the address intended to be used. Using the canonical address of a register is less likely to run into problems in expanded configurations. For instance, while \$D3C0 is a valid address to access the PORTA register on stock hardware, it may be overlaid and repurposed by expansion hardware.

#### Machine cycles (clocks)

Although most of the system actually runs at a faster rate, the smallest atomic unit of time for CPU execution is a

#### Altirra Hardware Reference Manual

single cycle at approximately 1.8MHz. All CPU instructions must begin and end on a cycle boundary; all reads and writes to registers must take place on a particular cycle. Unless otherwise specified, all cycles in this document refer to machine cycles.

#### **Color clock**

Much of the graphics system in the Atari runs at the speed of the *color clock*, which for NTSC machines runs at the color subcarrier (3.579545MHz). A *color cycle* is completed every time the color clock advances. The highest resolution possible for most graphics is determined by this clock, which produces 160 low resolution pixels across at standard playfield width. High resolution displays run at twice this frequency, for a dot clock of 7MHz, but only luminance effects are possible at this rate. Playfield and sprite positioning also occur at color clock rate.

There are two color cycles for every machine cycle. On PAL machines, where the color subcarrier is at a much higher frequency, most of the faster processes within GTIA still occur at twice the machine cycle rate.

#### Machine-specific behavior

There are unfortunately a few cases in which marginal timing causes systems to differ in behavior. Examples are the interrupt delay between POKEY and the 6502 and the behavior of the GTIA fifth player bit. In some cases this can even manifest as temperature sensitivity, where a system will change behavior once a certain involved chip has warmed up and display erratic behavior during the transition. It is best that code be written to avoid dependency on such cases and to tolerate variance between systems.

# Chapter 2 CPU

The 6502 chip is the CPU of the Atari. Used in many computers of the time and still in use as a microcontroller in enhanced forms, both the official and unofficial behaviors of the 6502 are well known. While the 6502 was later superseded by chips such as the 65C02 and the 65C816, the Atari 8-bit line continued using the original 6502 until the very end.

Note that there is some confusion as to the precise chip used in the Atari 8-bit series. The original 400/800 use the NMOS 6502, along with a handful of extra circuitry to provide the ability to halt the CPU for ANTIC DMA; this was later replaced with the 6502C, a custom version that contains the HALT logic built-in. This should not be confused with the CMOS 65C02, which is an enhanced 6502 with additional instructions and which was never used in the Atari 8-bit line.

The 6502 contains many nuances and unusual undocumented behaviors which are crucial to understand when programming to the metal on the Atari 8-bit series. For the sake of brevity, the basic architecture of the 6502 will be omitted here to allow more space for documenting these corner cases.

# 2.1 Registers

### Unused flag

The 6502 does not use bit 5 of the P register. It can't be cleared and always reads as a 1 when pushed to the stack with the PHP instruction or by interrupt entry.

On the 65C816, bit 5 is reused as the (M)ode bit in native mode.

#### Break (B) flag

Bit 4 of the processor status register is the (B)reak bit and is used to indicate whether an IRQ or a BRK instruction caused the IRQ routine to be run. It is set if the trigger was an BRK and cleared if it was a IRQ.

Contrary to both official and unofficial documentation, the B bit does not actually exist in the P register. Attempting to clear bit 4 of P and reading the result back always gives a 1 bit. The only time the B flag is visible is when the 6502 pushes the P register on the stack as part of interrupt handling. In that case, the P value pushed onto the stack will have bit 4 cleared for a BRK.

#### **Decimal (D) flag**

The D bit (bit 3) in the processor status register activates decimal mode in the 6502. When set to 1, the ADC and SBC instructions perform BCD correction. CMP, CPX, CPY, INC, DEC, and indexed addressing are not affected.

NMOS 6502s do not clear the D flag automatically, so it must be cleared on reset. It should also be cleared in an interrupt handler if the interrupt code uses ADC or SBC and mainline code may use decimal mode.

# 2.2 Decimal mode

#### **Decimal correction**

Decimal arithmetic in the 6502 works by correcting each nibble after addition or subtraction. For addition, 6 is added if the nibble result exceeds 10; for subtraction, 6 is subtracted if the result is negative. The carry between the low and high nibbles is computed before this correction, so the correction can never cause a double carry. For instance, for \$0F + \$0F, an intermediate result of \$1E is computed, and the correction then produces \$14.

#### Flags computation

All flags are computed after carries are propagated between nibbles but before decimal correction occurs.<sup>1</sup>

For addition, the C flag is set whenever there is a carry out from the high nibble, allowing for extended precision decimal arithmetic. For instance, \$99 + \$01 = \$00 with carry set. For subtraction, it is cleared for a borrow.

The Z flag is set when the intermediate result is \$00, before decimal correction. Example: FF + 01 = 66, with Z set.

The N flag is also set according to the intermediate result, to match bit 7. Example: \$99 + \$01 = \$00, with N set.

The V flag is set when the carry between bit 6 and bit 7 is different than the result carry, or alternatively, when there is a signed overflow in binary arithmetic.

[1] [IJO10]

#### 65C02 behavior

ADC and SBC take an additional cycle in decimal mode on the 65C02.

The 65C02 computes the N, V, and Z flags differently in decimal mode. All three are computed the same way as if the same result were achieved in binary mode. That is, N is set if bit 7 of the result is set; Z is set if the result is \$00; V is set if the carry from bit 6 to bit 7 is different than the carry flag.

ADC produces the same results for invalid BCD encodings on the 65C02 as it does on the 6502, but SBC can produce different results.<sup>2</sup>

#### 65C816 behavior

The 65C816 computes decimal flags and results the same way as the 65C02, regardless of the state of the E flag. This means that the flags can be tested to distinguish a 6502 from a 65C816 in the same way. No extra cycle is taken as with the 65C02.

Unlike the 65C02, the 65C816 produces the same accumulator results as the 6502 for an SBC instruction with invalid opcodes.

# 2.3 Cycle timing

#### **Clock speed**

On an NTSC machine, the 6502 runs at exactly half the speed of the color clock, or 1.789773MHz. There are exactly 114 cycles per scan line and 29,868 cycles per frame. On a PAL machine, the 6502 runs at 2/5ths the color subcarrier frequency, or 1.773447MHz; there are still 114 cycles per scan line, but 35,568 cycles per frame.

#### DMA contention

On occasion the Atari's custom chips must fetch data from memory. This is known as Direct Memory Access (DMA), and when it occurs, the 6502 is blocked from the memory bus while ANTIC does a read cycle. This phenomenon slows down execution of code on the CPU and is known as DMA contention. All DMA in the Atari is related to the display and therefore the graphics setup determines the reduction in CPU performance. For NTSC, the highest rate at which the CPU can run is 92% (1.65Mcycles/sec); the standard Graphics 0 display reduces this to 64% (1.14Mcycles/sec). PAL runs noticeably faster since all display related DMA runs only 5/6ths as often.

#### **Dead memory cycles**

The 6502 uses the memory bus on every cycle without exception. Most of the time this is for useful work and therefore leads to very efficient bus utilization. There are cases, however, when these memory cycles are wasted cycles, such as:

- The second cycle of an implied mode instruction. (TXA)

- The ALU cycle of a read-modify-write instruction. (INC abs)

- The second-to-last cycle of a zero page indexed read or write. (LDA zp,X)

- The second-to-last cycle of an absolute or indirect indexed write. (STA abs, X)

[2] [6502Dec]

- The second-to-last cycle of an absolute or indirect indexed read that crosses a page boundary (AND abs, Y).

- Conditional branches that cross a page boundary (BNE).

A memory transaction is issued during these dummy cycles and therefore these dead cycles cannot be overlapped by DMA – the CPU must still be halted. For the most part these cycles are harmless, as the Atari is a fairly safe platform where reads to hardware registers seldom have side effects. There are a few cases in which this does matter and indexing should be used with care:

- Accessing the PIA (\$D300-D3FF), because reads from the data registers will clear pending interrupts.

- Accessing the cartridge control region (\$D500-D5FF). Some cartridges use this region to switch banks and will respond to both reads and writes.

- Accessing PBI devices (\$D100-D1FE and \$D600-D7FF), which may also have read-sensitive regions.

- Any access with a read-modify-write instruction, since the extra cycle is a **write** cycle (except on the 65C02 or 65C816 in native mode).

#### **Crossing page boundaries**

The 6502 attempts to optimize indexed reads by issuing a speculative read before it has adjusted for a possible carry in the high byte. If no carry is required, a cycle is saved. Otherwise, if a carry is required, it will retry the read with the correct address. For example, given the following sequence:

LDX #\$80 LDA \$20F0,X

...the 6502 will read \$2070 first, and then retry with the correct address \$2170. The only modes that have this behavior are: abs,X, abs,Y, and (zp),Y. The zp,X, zp,Y, and (zp,X) modes do not need to index outside of zero page and wrap from \$00FF to \$0000 without an extra cycle; (zp),Y does not incur an extra cycle for using \$FF as the zero-page address. The (abs) mode, unique to JMP, also lacks the extra clock due to the well-known bug on the NMOS 6502 of accessing \$xxFF and \$xx00.

Writes, on the other hand, cannot be done speculatively as a wrong guess would trash an unrelated memory location. Therefore, stores using the abs,X, abs,Y, and (zp),Y modes always take the extra clock cycle. The first clock cycle is a speculative read and the second clock cycle is a write with the correct address. Read-modify-write instructions also always take an extra clock cycle, indexed or not, except that the dummy cycle is a **write** cycle.

Branches that cross a page boundary also have this behavior, doing a read with an incorrect address high byte first, and taking four clock cycles instead of three. No additional cycle is taken to cross a page boundary for a non-taken branch, a JMP, JSR, RTI, or RTS instruction, or any other non-branch execution.

#### Note

A branch crosses a page boundary when the addition of the signed branch offset changes the high byte of the PC. This means that a page crossing occurs if the target is on a different page from the address of the *next* instruction, not from the address of the branch instruction. For instance, a BCC \$80C0 instruction at \$80FE crosses a page because it is branching from \$8100 to \$80C0, even though the branch instruction itself is entirely within the same page as its target. Similarly, a BEQ \$8110 instruction at \$80FE does *not* cross a page. This happens because the branch offset is added after the PC has already been incremented for both bytes of the branch instruction.

# 2.4 Interrupts

#### Level-based vs. edge-based interrupts

IRQs on the 6502 are level triggered interrupts, which means that the interrupt request is a continuing condition that is active as long as the IRQ line is asserted. This facilitates delayed response to the IRQ as the 6502 will eventually respond to the IRQ as long as the device continues to assert the IRQ line. It also allows for multiplexing as multiple devices can assert IRQ and the 6502 will execute the IRQ handler repeatedly until all interrupts are handled. However, this also means that the interrupt condition must be cleared on the device or else the IRQ handler will continue to execute. It also means there is no memory of an interrupt event – if an interrupt request occurs while IRQs are masked in the 6502 and is revoked before they are unmasked, the IRQ handler will not execute.

NMIs, on the other hand, are edge triggered and are one-time event rather than a condition. Once the NMI signal is asserted, the 6502 will execute the NMI handler at the next opportunity. If a second NMI is requested before the first one is acknowledged, the NMI handler will only run once and the other NMI is lost.

#### Interrupt timing

The 6502 does not abort or resume instructions and can only respond to an interrupt on instruction boundaries. This means that longer instructions can increase interrupt response delay. The longest standard instruction possible on the 6502 is seven clocks, which can be due to a (zp),Y access crossing a page boundary, a read-modify-write instruction using abs,X mode, or a BRK/interrupt. A delay of 8 cycles is possible with undocumented read-modify-write instructions that use indirect indexed or indexed indirect mode, such as opcode \$13. However, much longer delays can occur if a store to WSYNC [D40A] is performed, which can lengthen an instruction by as much as a hundred clock cycles. Use of WSYNC should be avoided if display list interrupts or other time-critical interrupts are active.

#### **Clearing I with an interrupt pending**

If an interrupt is already pending but is blocked by the I flag, clearing the I flag with a CLI or PLP instruction will result in the interrupt occurring at the end of the next instruction, and not immediately after the clearing instruction. For instance, given the following code:

#### CLI NOP

The pending interrupt will not be serviced until the end of the NOP instruction. This does not happen with the RTI instruction; an IRQ can be serviced immediately after an RTI that clears the I flag.

#### Setting the I flag with an interrupt pending

Because of pipelining within the 6502, it is possible for the last cycle of a SEI or PLP instruction to execute immediately after the 6502 begins to acknowledge an IRQ. When this happens, the IRQ routine begins executing before the next instruction, and the curious result is that an IRQ executes with the pushed flags on the stack having the I bit set. The most common way to hit this behavior is using the following sequence to dispatch pending IRQs at a well-defined time:

CLI SEI

This does not happen with the RTI instruction, which changes the flags earlier in the instruction. This effect occurs with CLI+SEI and CLI+PLP pairs; it does not occur with CLI+RTI, PLP+[SEI/RTI/PLP], or RTI+[SEI/RTI/PLP], for which no IRQ is dispatched even if one is pending.

#### Taken branch delay

A taken relative branch delays interrupt acknowledgment by one cycle: a case in which the earliest opportunity to respond to an interrupt is immediately after the branch instead is delayed to the next instruction. This occurs for any Bcc instruction which does not cross a page boundary. The effect does not occur if the branch instruction crosses a page (4 cycles), or for any other control flow instruction such as JMP, JSR, RTS, or RTI.

#### **Overlapping interrupts**

It is possible for the 6502 to first begin executing the seven-cycle interrupt sequence for an IRQ and then jump to the NMI vector instead if an NMI occurs quickly enough.

For IRQ+NMI conflicts, this behavior simply leads to faster acknowledgment of the NMI. However, it also has unfortunate consequences for the BRK (\$00) instruction. The BRK instruction is essentially the same as an IRQ except that the flags byte pushed on the stack has the B flag set. Because of this, it is possible for an NMI to hijack the BRK sequence in the same way. When this occurs, the NMI vector is invoked with the B flag set on the flags byte on the stack. Thus, robust handling of BRK instructions requires it to be checked for in both the IRQ and NMI handlers.<sup>3</sup>

There are no issues with an overlapping IRQ and BRK instruction. However, when multiplexing the IRQ vector for both IRQ and BRK, the BRK instruction must be serviced before the handler exits. For multiplexed IRQs, the handler can service one IRQ at a time, relying on the hardware to keep IRQ asserted as causing the handler to re-execute until all IRQs are serviced. This is not true for BRK, which will be lost if not serviced.

On the Atari, this effect occurs if a BRK instruction begins execution at between cycles 4-8 of a scan line where either the DLI or VBI is activated.

<sup>[3]</sup> This effect is covered in detail in [VIC09], under 6510 Instruction Timing. The effect of an IRQ on a BRK is arguably not a bug, as I can find no program-visible effects: the BRK executes as expected, and the IRQ is then acknowledged afterward assuming that the IRQ line is still asserted. This does require that the IRQ handler check BRK first, though, which usually doesn't happen.

Figure 1: Effects of overlapping IRQ/NMI timing

The table above shows how the 6502 responds to IRQ and NMI being asserted at varying offsets from each other. When the IRQ occurs sufficiently before the NMI, the 6502 completes the pending interrupt sequence or current instruction before beginning the interrupt sequence for the NMI. This always entails a minimum of at least 7 cycles for the interrupt sequence and 6 cycles for the first instruction of the IRQ handler (LSR abs, 6 cycles). Unusual behavior starts when the IRQ sequence begins on cycle 4, which causes the NMI to be lost entirely. Afterward, the IRQ sequence that would begin at cycle 5 or later is taken over by the NMI, resulting in the NMI handler executing earlier than usual. The exact same timing occurs with BRK instead of IRQ.

#### **Consecutive interrupts**

The 6502 cannot acknowledge an interrupt immediately after executing an interrupt sequence. This includes BRK, IRQ, and NMI. The first instruction of the IRQ or NMI handler is always executed, regardless of any pending interrupt. The one case where interrupt sequences will execute back-to-back is if the first instruction of the interrupt handler is a BRK instruction. Because the BRK instruction is piggybacked on top of the interrupt logic, a pending interrupt can hijack the BRK instruction to run the interrupt handler instead.

# 2.5 Undocumented instructions

Out of the 256 possible 8-bit opcode encodings, 151 correspond to defined instructions. Due the way that the 6502 decodes instructions, some of the other 101 opcodes activate strange internal behaviors instead of being ignored or raising an interrupt.

Table 1 shows the complete opcode table for the 6502. Opcodes in gray are undocumented instructions that appear to have stable behavior; opcodes in yellow are undocumented instructions that appear to be unstable. Opcodes in red lock up the 6502 until reset.

|    | x0   | x1     | x2   | x3     | x4   | x5   | x6   | x7   | x8  | x9    | хA  | хB    | xC    | xD    | xE    | xF    |

|----|------|--------|------|--------|------|------|------|------|-----|-------|-----|-------|-------|-------|-------|-------|

| 0x | BRK  | ORA    | KIL  | SLO    | NOP  | ORA  | ASL  | SLO  | PHP | ORA   | ASL | ANC   | NOP   | ORA   | ASL   | SLO   |

|    |      | (zp,X) |      | (zp,X) | zp   | zp   | zp   | zp   |     | #imm  |     | #imm  | abs   | abs   | abs   | abs   |

| 1x | BPL  | ORA    | KIL  | SLO    | NOP  | ORA  | ASL  | SLO  | CLC | ORA   | NOP | SLO   | NOP   | ORA   | ASL   | SLO   |

|    | rel  | (zp),Y |      | (zp),Y | zp,X | zp,X | zp,X | zp,X |     | abs,Y |     | abs,Y | abs,X | abs,X | abs,X | abs,X |

| 2x | JSR  | AND    | KIL  | RLA    | BIT  | AND  | ROL  | RLA  | PLP | AND   | ROL | ANC   | BIT   | AND   | ROL   | RLA   |

|    | abs  | (zp,X) |      | (zp,X) | zp   | zp   | zp   | zp   |     | #imm  |     | #imm  | abs   | abs   | abs   | abs   |

| 3x | BMI  | AND    | KIL  | RLA    | NOP  | AND  | ROL  | RLA  | SEC | AND   | NOP | RLA   | NOP   | AND   | ROL   | RLA   |

|    | rel  | (zp),Y |      | (zp),Y | zp,X | zp,X | zp,X | zp,X |     | abs,Y |     | abs,Y | abs,X | abs,X | abs,X | abs,X |

| 4x | RTI  | EOR    | KIL  | SRE    | NOP  | EOR  | LSR  | SRE  | PHA | EOR   | LSR | ASR   | JMP   | EOR   | LSR   | SRE   |

|    |      | (zp,X) |      | (zp,X) | zp   | zp   | zp   | zp   |     | #imm  |     | #imm  | abs   | abs   | abs   | abs   |

| 5x | BVC  | EOR    | KIL  | SRE    | NOP  | EOR  | LSR  | SRE  | CLI | EOR   | NOP | SRE   | NOP   | EOR   | LSR   | SRE   |

|    | rel  | (zp),Y |      | (zp),Y | zp,X | zp,X | zp,X | zp,X |     | abs,Y |     | abs,Y | abs,X | abs,X | abs,X | abs,X |

| 6x | RTS  | ADC    | KIL  | RRA    | NOP  | ADC  | ROR  | RRA  | PLA | ADC   | ROR | ARR   | JMP   | ADC   | ROR   | RRA   |

|    |      | (zp,X) |      | (zp,X) | zp   | zp   | zp   | zp   |     | #imm  |     | #imm  | (abs) | abs   | abs   | abs   |

| 7x | BVS  | ADC    | KIL  | RRA    | NOP  | ADC  | ROR  | RRA  | SEI | ADC   | NOP | RRA   | NOP   | ADC   | ROR   | RRA   |

|    | rel  | (zp,Y) |      | (zp),Y | zp,X | zp,X | zp,X | zp,X |     | abs,Y |     | abs,Y | abs,X | abs,X | abs,X | abs,X |

| 8x | NOP  | STA    | NOP  | SAX    | STY  | STA  | STX  | SAX  | DEY | NOP   | TXA | ANE   | STY   | STA   | STX   | SAX   |

|    | #imm | (zp,X) | #imm | (zp,X) | zp   | zp   | zp   | zp   |     | #imm  |     | #imm  | abs   | abs   | abs   | abs   |

| 9x | BCC  | STA    | KIL  | SHA    | STY  | STA  | STX  | SAX  | TYA | STA   | TXS | SHS   | SHY   | STA   | SHX   | SHA   |

|    | rel  | (zp),Y |      | (zp),Y | zp,X | zp,X | zp,Y | zp,X |     | abs,Y |     | abs,Y | abs,X | abs,X | abs,Y | abs,Y |

| Ax | LDY  | LDA    | LDX  | LAX    | LDY  | LDA  | LDX  | LAX  | TAY | LDA   | TAX | LXA   | LDY   | LDA   | LDX   | LAX   |

|    | #imm | (zp,X) | #imm | (zp,X) | zp   | zp   | zp   | zp   |     | #imm  |     | #imm  | abs   | abs   | abs   | abs   |

| Bx | BCS  | LDA    | KIL  | LAX    | LDY  | LDA  | LDX  | LAX  | CLV | LDA   | TSX | LAS   | LDY   | LDA   | LDX   | LAX   |

|    | rel  | (zp),Y |      | (zp),Y | zp,X | zp,X | zp,Y | zp,Y |     | abs,Y |     | abs,Y | abs,X | abs,X | abs,Y | abs,X |

| Сх | CPY  | CMP    | NOP  | DCP    | CPY  | CMP  | DEC  | DCP  | INY | CMP   | DEX | SBX   | CPY   | CMP   | DEC   | DCP   |

|    | #imm | (zp,X) | #imm | (zp,X) | zp   | zp   | zp   | zp   |     | #imm  |     | #imm  | abs   | abs   | abs   | abs   |

| Dx | BNE  | CMP    | KIL  | DCP    | NOP  | CMP  | DEC  | DCP  | CLD | CMP   | NOP | DCP   | NOP   | CMP   | DEC   | DCP   |

|    | rel  | (zp),Y |      | (zp),Y | zp,X | zp,X | zp,X | zp,X |     | abs,Y |     | abs,Y | abs,X | abs,X | abs,X | abs,X |

| Ex | CPX  | SBC    | NOP  | ISB    | CPX  | SBC  | INC  | ISB  | INX | SBC   | NOP | SBC   | CPX   | SBC   | INC   | ISB   |

|    | #imm | (zp,X) | #imm | (zp,X) | zp   | zp   | zp   | zp   |     | #imm  |     | #imm  | abs   | abs   | abs   | abs   |

| Fx | BEQ  | SBC    | KIL  | ISB    | NOP  | SBC  | INC  | ISB  | SED | SBC   | NOP | ISB   | NOP   | SBC   | INC   | ISB   |

|    | rel  | (zp),Y |      | (zp),Y | zp,X | zp,X | zp,X | zp,Y |     | abs,Y |     | abs,Y | abs,X | abs,X | abs,X | abs,X |

Table 1: NMOS 6502 opcode table

#### Note on opcode names

Because the additional instructions were neither supported nor documented, there are no official names for the instructions. As such, emulators, assemblers, and disassemblers vary widely in the names used. The names used here match a popularly used assembler, but they are by no means definitive.<sup>4</sup>

#### KIL

Opcodes: \$02, 12, 22, 32, 42, 52, 62, 72, 92, B2, D2, F2.

The KIL opcodes permanently lock up the 6502 such that it stops executing instructions and no longer responds to interrupts. Only a reset will restart execution.

#### NOP

Opcodes: \$04, 0C, 14, 1A, 1C, 34, 3C, 44, 54, 5A, 4C, 64, 74, 7A, 7C, 80, 82, 89, D4, DA, DC, F4, FA, FC.

NOP opcodes may execute addressing modes but do not change registers, flags, or control flow. Opcode \$EA is the only official NOP instruction.

Note that these opcodes proceed similarly to ALU operations, so they will read operands similarly as to an LDA instruction. This includes executing an additional cycle when indexing across a page boundary.

#### Merged read-modify-write and read-modify instructions

Many of the illegal instructions are a result of combining read-modify-write instructions such as INC/DEC with ALU instructions like ADC and SBC. The combinations are:

- DCP = DEC + CMP

- ISB = INC + SBC

- SLO = ASL + ORA

- RLA = ROL + AND

- SRE = LSR + EOR

- RRA = ROR + ADC

The read-modify-write portion proceeds in the same manner, but the result of the RMW instruction is then used as the argument of the ALU instruction, changing the flags and potentially A. Cycle count is the same as the RMW instruction.

The ISB and RRA instructions are sensitive to the decimal mode flag due to incoporation of the SBC and ADC functions.

#### LAX (LDA + LDX)

Opcodes: \$A3, A7, AF, B3, B7, BF

LAX instructions load the same value into both A and X, setting the N and Z flags.

<sup>[4]</sup> For more information on undocumented opcodes and alternative mnemonics: [VIC09] [IIIOpc]

#### SAX (STA + STX)

Opcodes: \$87, 8F, 97, 9F

Stores the bitwise AND of A and X to memory. No flags are changed.

#### SHA

Opcodes: \$93

Stores the bitwise AND of A, X, and the high byte read from the base address. Note that this is the high byte of the *base* address as read from page zero, not the high byte after Y has been added.

In addition, if a page crossing occurs during indexing with Y, the result of the bitwise AND also replaces the high address byte.

#### Warning

The \$93 opcode has been reported to be unstable – the interaction between the high byte and bitwise AND operation does not reliably occur on all CPUs.

#### SHX

Opcodes: \$9E

Stores the bitwise AND of X and the high byte + 1 of the base address. If a page crossing occurs during indexing with Y, the bitwise AND result also replaces the high address byte.

#### ANC

Opcodes: \$0B

Same as AND, except with the result bit 7 also being copied into the carry flag.

## ASR (AND + LSR)

Opcodes: \$4B

Same as an AND instruction followed by and LSR A instruction.

#### ARR (ADC + AND + ROR)

Opcodes: \$6B

Performs a complex operation involving a rotate right and possible decimal correction, changing the A register and the N, V, Z, and C flags.

#### ANE

#### Opcodes: \$8B

Bitwise AND with accumulator, X, and immediate data, written back to accumulator.

#### Warning

The \$8B opcode is not stable and may produce varying results where not all bits in the above formula participate in the bitwise AND instruction.<sup>5</sup>

#### SHS (TXS + STA abs,Y)

Opcodes: \$9B

The stack pointer (S) is set to the bitwise AND of X and A, and the data written to abs, Y is this result bitwise ANDed with the high byte + 1.

#### LXA (LDA + TAX)

Stores the bitwise AND of A and the argument to both A and X, setting the N and Z flags.

#### Warning

The \$AB opcode is not stable. It has been reported to load the immediate argument to A and X without the bitwise AND on an Atari 800.

#### LAS (LDA + TSX)

A, X, and S are set to the bitwise AND of the read data and S, with the N and Z flags set as usual.

#### SBX

AND A into the X register, then CMP with data.

#### 2.6 65C02 compatibility

The 65C02 is an enhanced version of the 6502 implemented in CMOS and with additional instructions added. While it is mostly compatible with the 6502, there are a few differences in both documented and undocumented behavior.

Note that the 65C02 is not the same as a 6502C. Some Atari computers had a custom CPU called the 6502C (Sally) that had integrated HALT logic. This chip uses the same NMOS 6502 core and lacks the additional instructions or behavior of the newer 65C02.

#### **Opcode table**

None of the undocumented instructions of the 6502 work on the 65C02. All previously unassigned opcodes are reassigned to new opcodes or defined as NOPs with specific behavior. Table 2 shows the new opcodes in green and the defined NOPs in gray. Bit change/branch opcodes in purple are only supported by some 65C02 variants; other 65C02 makes and the 65C816 do not support bit opcodes.

<sup>[5]</sup> See <u>http://visual6502.org/wiki/index.php?title=6502\_Opcode\_8B\_%28XAA,\_ANE%29</u> for an extended discussion of this opcode.

|    | x0   | x1     | x2   | x3  | x4   | x5   | x6   | x7   | x8  | x9    | хA  | хB  | xC      | xD    | хE    | xF     |

|----|------|--------|------|-----|------|------|------|------|-----|-------|-----|-----|---------|-------|-------|--------|

| 0x | BRK  | ORA    | NOP  | NOP | TSB  | ORA  | ASL  | RMB0 | PHP | ORA   | ASL | NOP | TSB     | ORA   | ASL   | BBR0   |

|    |      | (zp,X) |      |     | zp   | zp   | zp   | zp   |     | #imm  |     |     | abs     | abs   | abs   | zp,rel |

| 1x | BPL  | ORA    | ORA  | NOP | TRB  | ORA  | ASL  | RMB1 | CLC | ORA   | INC | NOP | TRB     | ORA   | ASL   | BBR1   |

|    | rel  | (zp),Y | (zp) |     | zp   | zp,X | zp,X | zp   |     | abs,Y |     |     | abs     | abs,X | abs,X | zp,rel |

| 2x | JSR  | AND    | NOP  | NOP | BIT  | AND  | ROL  | RMB2 | PLP | AND   | ROL | NOP | BIT     | AND   | ROL   | BBR2   |

|    | abs  | (zp,X) |      |     | zp   | zp   | zp   | zp   |     | #imm  |     |     | abs     | abs   | abs   | zp,rel |

| 3x | BMI  | AND    | AND  | NOP | BIT  | AND  | ROL  | RMB3 | SEC | AND   | DEC | NOP | BIT     | AND   | ROL   | BBR3   |

|    | rel  | (zp),Y | (zp) |     | zp,X | zp,X | zp,X | zp   |     | abs,Y |     |     | abs,X   | abs,X | abs,X | zp,rel |

| 4x | RTI  | EOR    | NOP  | NOP | NOP  | EOR  | LSR  | RMB4 | PHA | EOR   | LSR | NOP | JMP     | EOR   | LSR   | BBR4   |

|    |      | (zp,X) |      |     |      | zp   | zp   | zp   |     | #imm  |     |     | abs     | abs   | abs   | zp,rel |

| 5x | BVC  | EOR    | EOR  | NOP | NOP  | EOR  | LSR  | RMB5 | CLI | EOR   | PHY | NOP | NOP     | EOR   | LSR   | BBR5   |

|    | rel  | (zp),Y | (zp) |     |      | zp,X | zp,X | zp   |     | abs,Y |     |     |         | abs,X | abs,X | zp,rel |

| 6x | RTS  | ADC    | NOP  | NOP | STZ  | ADC  | ROR  | RMB6 | PLA | ADC   | ROR | NOP | JMP     | ADC   | ROR   | BBR6   |

|    |      | (zp,X) |      |     | zp   | zp   | zp   | zp   |     | #imm  |     |     | (abs)   | abs   | abs   | zp,rel |

| 7x | BVS  | ADC    | ADC  | NOP | STZ  | ADC  | ROR  | RMB7 | SEI | ADC   | PLY | NOP | JMP     | ADC   | ROR   | BBR7   |

|    | rel  | (zp,Y) | (zp) |     | zp,X | zp,X | zp,X | zp   |     | abs,Y |     |     | (abs,X) | abs,X | abs,X | zp,rel |

| 8x | BRA  | STA    | NOP  | NOP | STY  | STA  | STX  | SMB0 | DEY | BIT   | TXA | NOP | STY     | STA   | STX   | BBS0   |

|    | rel  | (zp,X) |      |     | zp   | zp   | zp   | zp   |     | #imm  |     |     | abs     | abs   | abs   | zp,rel |

| 9x | BCC  | STA    | STA  | NOP | STY  | STA  | STX  | SMB1 | TYA | STA   | TXS | NOP | STZ     | STA   | STZ   | BBS1   |

|    | rel  | (zp),Y | (zp) |     | zp,X | zp,X | zp,Y | zp   |     | abs,Y |     |     | abs     | abs,X | abs,X | zp,rel |

| Ax | LDY  | LDA    | LDX  | NOP | LDY  | LDA  | LDX  | SMB2 | TAY | LDA   | TAX | NOP | LDY     | LDA   | LDX   | BBS2   |

|    | #imm | (zp,X) | #imm |     | zp   | zp   | zp   | zp   |     | #imm  |     |     | abs     | abs   | abs   | zp,rel |

| Bx | BCS  | LDA    | LDA  | NOP | LDY  | LDA  | LDX  | SMB3 | CLV | LDA   | TSX | NOP | LDY     | LDA   | LDX   | BBS3   |

|    | rel  | (zp),Y | (zp) |     | zp,X | zp,X | zp,Y | zp   |     | abs,Y |     |     | abs,X   | abs,X | abs,Y | zp,rel |

| Сх | CPY  | CMP    | NOP  | NOP | CPY  | CMP  | DEC  | SMB4 | INY | CMP   | DEX | WAI | CPY     | CMP   | DEC   | BBS4   |

|    | #imm | (zp,X) |      |     | zp   | zp   | zp   | zp   |     | #imm  |     |     | abs     | abs   | abs   | zp,rel |

| Dx | BNE  | CMP    | CMP  | NOP | NOP  | CMP  | DEC  | SMB5 | CLD | CMP   | PHX | STP | NOP     | CMP   | DEC   | BBS5   |

|    | rel  | (zp),Y | (zp) |     |      | zp,X | zp,X | zp   |     | abs,Y |     |     |         | abs,X | abs,X | zp,rel |

| Ex | CPX  | SBC    | NOP  | NOP | CPX  | SBC  | INC  | SMB6 | INX | SBC   | NOP | NOP | CPX     | SBC   | INC   | BBS6   |

|    | #imm | (zp,X) |      |     | zp   | zp   | zp   | zp   |     | #imm  |     |     | abs     | abs   | abs   | zp,rel |

| Fx | BEQ  | SBC    | SBC  | NOP | NOP  | SBC  | INC  | SMB7 | SED | SBC   | PLX | NOP | NOP     | SBC   | INC   | BBS7   |

|    | rel  | (zp),Y | (zp) |     |      | zp,X | zp,X | zp   |     | abs,Y |     |     |         | abs,X | abs,X | zp,rel |

Table 2: 65C02 opcode table

## Absolute indirect addressing bug

The JMP (abs) instruction (\$6C) no longer wraps within a page on the 65C02: a JMP (\$02FF) instruction will access \$2FF and \$300 instead of \$2FF and \$200, and take an additional cycle when doing so.

#### Decimal mode

ADC and SBC instructions take one additional cycle in decimal mode on the 65C02. This is to compute proper flag results.

The 65C02 automatically clears the decimal flag on reset or on entry to an interrupt. On the 6502, it was undefined on power-up and left at the previous state on interrupt.

#### **Read-modify-write instructions**

Instructions that do read-modify-write cycles – INC, DEC, ASL, LSR, ROL, and ROR – behave differently during the modify cycle. On the original 6502, the sequence is read-write-write, where the second cycle is a write cycle that just rewrites the data that was just read. On the 65C02, the second cycle is a read cycle to that address. This alters the timing of RMW instructions to WSYNC and breaks fast IRQ acknowledgment hacks involving RMW cycles on IRQEN/IRQST.

#### Read-modify-write with absolute indexing

The abs,X mode versions of read-modify-write instructions only take 6 cycles on the 65C02 when indexing within a page, instead of 7 as on the 6502.

# 2.7 65C816 compatibility

The 65C816 is a further enhanced version of the 65C02 with even more instructions and addressing modes as well as new native execution mode. It is actually slightly more compatible with the original 6502 than the 65C02 due to some corrections in emulation mode. Because of its greatly increased power, the 65C816 is more common of an addition to Atari computers than the 65C02.

#### **Opcode table**

The 65C816 doesn't support any of the 6502's undocumented instructions either, but it has even more of the previously unused opcodes filled with valid instructions, including ones that were NOPs on the 65C02. There are no unassigned opcodes on the 65C816. New opcodes are shown in blue in Table 3.

|    | x0   | x1     | x2    | x3      | x4   | x5   | x6   | x7     | x8  | x9    | хA  | хB  | xC       | xD    | xE    | xF   |

|----|------|--------|-------|---------|------|------|------|--------|-----|-------|-----|-----|----------|-------|-------|------|

| 0x | BRK  | ORA    | COP   | ORA     | TSB  | ORA  | ASL  | ORA    | PHP | ORA   | ASL | PHD | TSB      | ORA   | ASL   | ORA  |

|    |      | (dp,X) | imm   | d,S     | dp   | dp   | dp   | [dp]   |     | #imm  |     |     | abs      | abs   | abs   | al   |

| 1x | BPL  | ORA    | ORA   | ORA     | TRB  | ORA  | ASL  | ORA    | CLC | ORA   | INC | TCS | TRB      | ORA   | ASL   | ORA  |

|    | rel  | (dp),Y | (dp)  | (d,S),Y | dp   | dp,X | dp,X | [dp],Y |     | abs,Y |     |     | abs      | abs,X | abs,X | al,X |

| 2x | JSR  | AND    | JSR   | AND     | BIT  | AND  | ROL  | AND    | PLP | AND   | ROL | PLD | BIT      | AND   | ROL   | AND  |

|    | abs  | (dp,X) | al    | d,S     | dp   | dp   | dp   | [dp]   |     | #imm  |     |     | abs      | abs   | abs   | al   |

| 3x | BMI  | AND    | AND   | AND     | BIT  | AND  | ROL  | AND    | SEC | AND   | DEC | TSC | BIT      | AND   | ROL   | AND  |

|    | rel  | (dp),Y | (dp)  | (d,S),Y | dp,X | dp,X | dp,X | [dp],Y |     | abs,Y |     |     | abs,X    | abs,X | abs,X | al,X |