#

1

## LEVEL 6

HARDWARE

TYPE CPF9509 WRITABLE CONTROL STORE USER'S GUIDE

### TYPE CPF9509 WRITABLE CONTROL STORE USER'S GUIDE

Document No.: 71010620-100 Order No.: FQ41, Rev. 0

#### System Integrity Disclaimer

Honeywell normally assumes responsibility for assuring the compatible coexistence of the total computer system, including hardware and software modules, as specified in appropriate Honeywell literature. The assumption of this responsibility is based on extensive planning, specification, stability, and qualification testing of each component and of the integrated system.

The Writable Control Store allows a user to control the underlying hardware base of a Model 43 or higher system. Because user microprogramming can bypass both the normal hardware and software integrity controls, Honeywell cannot ensure system integrity, compatibility, or performance once the WCS is utilized to execute user generated firmware.

#### PREFACE

This manual describes how to use the Writable Control Store (WCS) feature, enabling a user to successfully generate and execute firmware routines in the Central Processing Unit (CPU), and includes a description of the Model 43/53 CPU. It is written to provide a microprogrammer with an understanding of the microinstruction codes, the assembler, and the loading procedures to perform the above tasks. It assumes that the reader has a working knowledge of the Level 6 architecture, the CPU, the associated system software, and the applicable operation procedures. For those who are unfamiliar with this information, it is recommended that they familiarize themselves with the material contained in the following support documentation.

- Honeywell Level 6 Minicomputer Handbook (Order No. AS22)

- GCOS 6 Program Preparation (Order No. CBU1)

- GCOS 6 Commands (Order No. CB02)

- GCOS 6 Assembly Language Reference (Order No. CB07)

- GCOS 6 MOD 400 Program Execution and Checkout (Order No. CB21)

- GCOS 6 MOD 400 System Building (Order No. CB23)

- GCOS 6 MOD 400 Operator's Guide (Order No. CB24)

ŧ

Copyright (C) 1978 Honeywell Information Systems Inc.

C

(

C

| Section |                                                                 |                                                                                                            |                                                                                                     |                                                                                                                                                                                                | Page                                                                                                                        |

|---------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| I       | INTRODU<br>1. <u>]</u><br>1.2                                   | General (                                                                                                  | Characteris<br>e WCS                                                                                | stics                                                                                                                                                                                          | 1-1<br>1-1<br>1-2                                                                                                           |

| II      | HARDWAH<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8 | Microprod<br>Internal<br>Megabus I<br>Miscellar<br>Firmware<br>Master CI<br>Entering<br>Use of CH<br>2.8.1 | and Leavin<br>PU Elements                                                                           | area<br>vare Area<br>Area<br>and Timing Considerations<br>og the WCS<br>visible<br>Dedicated<br>orage                                                                                          | $\begin{array}{c} 2-1 \\ 2-3 \\ 2-4 \\ 2-5 \\ 2-6 \\ 2-7 \\ 2-7 \\ 2-9 \\ 2-11 \\ 2-11 \\ 2-12 \\ 2-15 \\ 2-18 \end{array}$ |

| III     | MICROIN<br>3.1<br>3.2                                           | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5                                                                  | cessor Area<br>Syntax<br>Microproce<br>Destinatio<br>Microproce<br>Microproce<br>Bus Area<br>Syntax | essor Sources and                                                                                                                                                                              | 3-1 3-1 3-3 3-3 3-6 3-8 3-11 3-12 3-14 3-14 3-15                                                                            |

|         |                                                                 | 3.2.3                                                                                                      | 3.2.2.2<br>3.2.2.3<br>3.2.2.4<br>3.2.2.5<br>Internal B<br>3.2.3.1<br>3.2.3.2<br>3.2.3.3<br>3.2.3.4  | RAM Locations<br>Megabus Buffers<br>Constants<br>Other Internal Bus<br>Sources<br>US Destinations<br>Megabus Address<br>Registers<br>RAM Locations<br>Indicator Register<br>Other Destinations | 3-15<br>3-16<br>3-17<br>3-18<br>3-25<br>3-25<br>3-25<br>3-25<br>3-26<br>3-26                                                |

5

Section

|     |                                                                                                                                                                                                                                                                                   | Page                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 3.3 | <ul> <li>3.2.4 Internal Bus Examples</li> <li>Megabus Interface Area</li> <li>3.3.1 Syntax</li> <li>3.3.2 Megabus Interface Functions</li> </ul>                                                                                                                                  | 3 28<br>3-29<br>3-33<br><b>3-3</b> 3                                                         |

| 3.4 | 3.4.1 Syntax<br>3.4.2 Indicator Register (I) Bits                                                                                                                                                                                                                                 | 3-34<br>3-38<br>3-38<br>3-38                                                                 |

| 3.5 | 3.5.1 Transparent and Sequential Mode                                                                                                                                                                                                                                             | 3-39<br>3-40<br>3-40<br>3-42<br>3-48<br>3-49                                                 |

| 3.6 | Differences<br>3.5.2 Transparent Mode Syntax<br>3.5.3 Sequential Mode Syntax<br>3.5.4 Conditions<br>3.5.5 Address Values<br>3.5.6 Firmware Sequencing Examples<br>Master Clock Area                                                                                               | 3-49<br>3-50<br>3-52<br>3-53<br>3-61<br>3-61<br>3-63                                         |

|     | <ul><li>3.6.1 Syntax</li><li>3.6.2 Usage of Master Clock</li><li>Microinstructions</li></ul>                                                                                                                                                                                      | 3-63<br>3-63                                                                                 |

| 3.7 | Examples of Firmware Routines                                                                                                                                                                                                                                                     | 3-63                                                                                         |

| 4.1 | <ul> <li>4.1.1 Mnemonic Codes</li> <li>4.1.2 Symbolic Names</li> <li>4.1.3 Constants</li> <li>4.1.4 Statement References</li> <li>4.1.5 Punctuation</li> </ul>                                                                                                                    | 4 - 1<br>4 - 3<br>4 - 4<br>4 - 4<br>4 - 5<br>4 - 6<br>4 - 7                                  |

| 4.2 | Source Statement Formats<br>4.2.1 Firmware Statement<br>4.2.2 Pseudo-Op Statement<br>4.2.3 Blank Lines<br>4.2.4 Comment Lines                                                                                                                                                     | $ \begin{array}{r} 4 - 3 \\ 4 - 8 \\ 4 - 9 \\ 4 - 10 \\ 4 - 10 \\ \end{array} $              |

| 4.3 | Control Statements<br>4.3.1 DEFAULT Statement<br>4.3.2 END Statement<br>4.3.3 EQU Statement<br>4.3.4 LABEL Statement<br>4.3.5 LIST Statement<br>4.3.6 NATIVE Statement<br>4.3.7 NLST Statement<br>4.3.8 NO LIST Statement<br>4.3.9 SEQUENTIAL Statement<br>4.3.10 TITLE Statement | 4 10<br>4-11<br>4-11<br>4-12<br>4-13<br>4-13<br>4-13<br>4-13<br>4-13<br>4-13<br>4-13<br>4-13 |

ΙV

C

(

C

| Section  |                            |                                                                                                                                                                                                                                                                                    | Page                                               |

|----------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

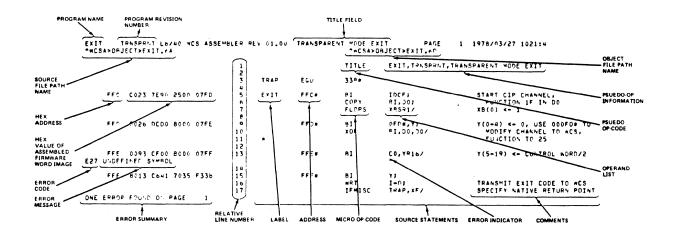

|          | 4.4<br>4.5<br>4.6          | Interpreting WCS Assembly Listings<br>WCS Assembler Object Deck Format<br>Assembler Output Listing Error Messages                                                                                                                                                                  | 414<br>4-14<br>4-15                                |

| v        | OPER<br>5.1<br>5.2         | Loading the WCS<br>5.2.1 Writable Control Store Load<br>(WCSLD) Command                                                                                                                                                                                                            | 5-1<br>5-1<br>5-3<br>5-4                           |

|          | 5.3                        | <ul> <li>5.2.2 Error Handling</li> <li>Debugging WCS Microprograms</li> <li>5.3.1 User Generic Not Invoked</li> <li>5.3.2 Instruction Does Not Exit</li> <li>5.3.3 Instruction Exits Via Unexpected<br/>Trap</li> </ul>                                                            | 5-5<br>5-6<br>5-7<br>5-8                           |

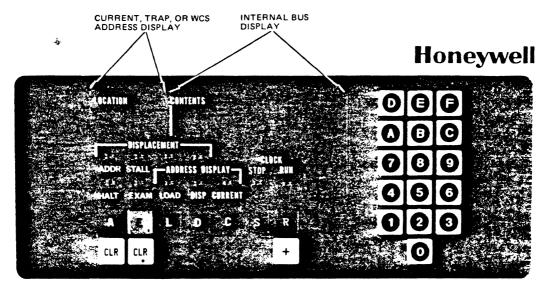

|          | 5.4<br>5.5                 | <ul> <li>5.3.4 Instructions Executes and Produces<br/>Unexpected Results</li> <li>WCS Patch Procedure<br/>Microcode Analyzer</li> <li>5.5.1 Front Panel</li> <li>5.5.1.1 Front Panel Keys</li> <li>5.5.1.2 Front Panel Indicators</li> <li>5.5.1.3 Internal Bus Display</li> </ul> | 5-9<br>5-9<br>5-10<br>5-10<br>5-11<br>5-12<br>5-12 |

|          |                            | 5.5.1.4 Address Display<br>5.5.2 Normal Operation<br>5.5.2.1 Operate in Single Step<br>Mode                                                                                                                                                                                        | 5-12<br>5-13<br>5-13                               |

|          |                            | 5.5.2.2 Return to Continous<br>Operation<br>5.5.2.3 Set Up a Halt Address<br>5.5.2.4 Halt at a Particular                                                                                                                                                                          | 5-13<br>5-13                                       |

|          |                            | Address<br>5.5.2.5 Disable Address Halt<br>5.5.2.6 Display the Current<br>Data<br>5.5.2.7 Display History                                                                                                                                                                          | 5-14<br>5-14<br>5-14<br>5-14                       |

| VI       | PROG:<br>6.1<br>6.2<br>6.3 | 5.5.2.8 Synchronize Oscilloscop<br>RAMMING CONSIDERATIONS<br>Logical and Physical Layout<br>Loading Firmware Image into WCS<br>Relationship of User Generics to WCS<br>Entry Points                                                                                                | e 5-15<br>6-1<br>6-1<br>6-1<br>6-4                 |

| Appendia | K A I                      | Writable Control Store Assembler Abort Codes                                                                                                                                                                                                                                       | A-1                                                |

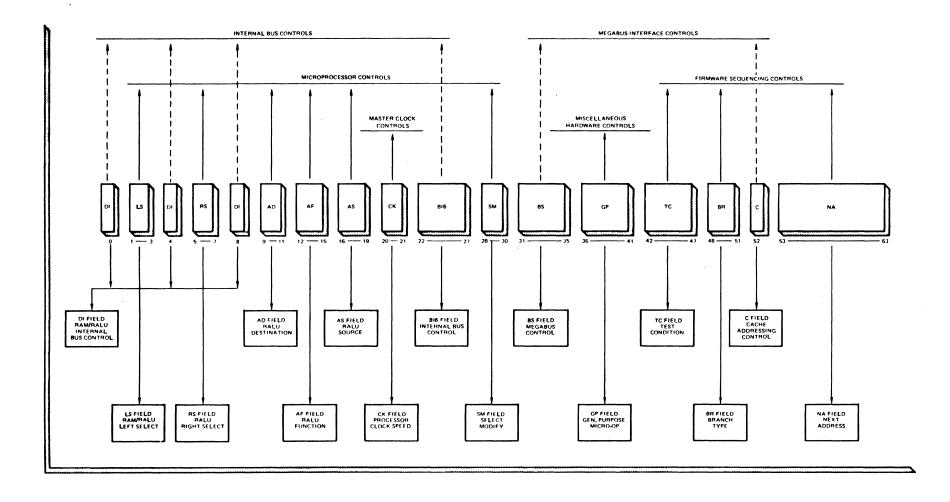

| Appendi  | K B I                      | Firmware Word Format                                                                                                                                                                                                                                                               | B-1                                                |

| Appendix | K C I                      | Reserved Word List and Encodings                                                                                                                                                                                                                                                   | C-1                                                |

v

| Section    |                           | Page |

|------------|---------------------------|------|

| Appendix D | Summary of Restrictions   | D-1  |

| Appendix E | Instruction Register Maps | E-1  |

# ILLUSTRATIONS

| Figure                                               |                                                                                                                                                                                                        | Page                                          |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8 | Hardware Configuration<br>Central Processor Area<br>Microprocessor Area<br>Internal Bus Area<br>Megabus Interface Area<br>Miscellaneous Hardware Area<br>Firmware Sequencing Area<br>Master Clock Area | 2-1<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8 |

| 3-1<br>3-2<br>3-3<br>3-4                             | Microprocessor Area<br>Internal Bus Area<br>Megabus Interface Area<br>Link Register Operands                                                                                                           | 3-2<br>3-13<br>3-30<br>3-51                   |

| 4-1<br>4-2<br>4-3                                    | Relationship of Source File, Assembler, and<br>Object File<br>Sample Output Listing<br>Sample File Dump                                                                                                | <b>4</b> -2<br><b>4</b> -14<br><b>4</b> -15   |

| 5-1                                                  | Front Panel                                                                                                                                                                                            | 5-11                                          |

| 6-1                                                  | Typical Loading Procedure                                                                                                                                                                              | 6-3                                           |

| B-1                                                  | Firmware Word Format                                                                                                                                                                                   | B-2                                           |

vi

TABLES

C

C

C

| Table                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page                                                                                                          |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 2-1                                                                                                         | Use of CPU Elements                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-19                                                                                                          |

| 3-1 3-2 3-3 3-4 3-5 3-6 3-7 3-8 3-9 3-10 3-11 3-12 3-13                                                     | ALU Source and Destination Operands<br>ALU Functions<br>Internal Bus Sources<br>Internal Bus Destinations<br>Megabus Interface Microinstructions<br>Miscellaneous Hardware Operands<br>Permissible GP Combinations<br>Transparent Mode Branch Address Operands<br>Firmware Sequencing Conditions<br>IFBCND Test Function<br>Data Field Size Tests<br>Source Statements for Transparent Mode<br>Source Statements for Sequential Mode | 3-5<br>3-8<br>3-21<br>3-37<br>3-43<br>3-47<br>3-52<br>3-54<br>3-59<br>3-60<br>3-62<br>3-62                    |

| 6-1                                                                                                         | WCS Entry Points                                                                                                                                                                                                                                                                                                                                                                                                                     | 6-5                                                                                                           |

| B-1<br>B-2<br>B-3<br>B-4<br>B-5<br>B-6<br>B-7<br>B-8<br>B-9<br>B-10<br>B-11<br>B-12<br>B-13<br>B-14<br>B-15 | General Purpose (GP) Field Decodes<br>RALU Left Select (LS) Field Decodes                                                                                                                                                                                                                                                                                                                                                            | B-3<br>B-4<br>B-5<br>B-5<br>B-6<br>B-8<br>B-9<br>B-10<br>B-12<br>B-13<br>B-14<br>B-18<br>B-19<br>B-20<br>B-21 |

| C-1<br>C-2<br>C-3                                                                                           | Register File Operand Encodings<br>RAM Location Operand Encodings<br>LS/RS and SM Encoding Values                                                                                                                                                                                                                                                                                                                                    | C-21<br>C-22<br>C-22                                                                                          |

| D-1<br>D-2<br>D-3<br>D-4<br>D-5                                                                             | Register File/RAM Locations Legal Groups<br>Register File "Restricted Selection" Criteria<br>Register File/RAM Location Operand<br>Correspondence<br>Permissible GP Combinations<br>Operands Affecting AUZ, CRY, and OVFL                                                                                                                                                                                                            | D-7<br>D-7<br>D-8<br>D-8<br>D-10                                                                              |

| E-1<br>E-2<br>E-3<br>E-4<br>E-5<br>E-6                                                                      | Main Splatter Map<br>Key to XR<br>Key to XW<br>XA Variations<br>XB Variations<br>Test Conditions                                                                                                                                                                                                                                                                                                                                     | E-3<br>E-4<br>E-4<br>E-5<br>E-6<br>E-8                                                                        |

# SECTION 1 - INTRODUCTION

Today's continued advancement of computer technology has produced a user-accessible control store extension within a Central Processor Unit (CPU) called Writable Control Store (WCS). This WCS feature provides a user with extremely powerful hardware instructions that extend as well as enhance the standard CPU software instruction set to achieve optimum CPU performance for software routines critical to a particular application, and allows them to execute at speeds comparable to the native CPU instructions. They accomplish this by enabling a user to write customized microprograms (firmware) into a CPU to replace repetitive software routines. Much of the speed enhancement derives from the ability of the firmware to perform several simultaneous operations in a single firmware step.

The application for the WCS feature varies considerably from one user to another. It enables a microprogrammer to enhance and augment the native CPU firmware to produce the equivalent of a customer built, specialized central processor. Software routines (or programs) designed to run without the WCS feature are unaffected by its presence.

The closeness of the firmware to hardware requires that the microprogrammer have a solid understanding of all the CPU functions, characteristics, and limitations. The key to effective custom-microprogramming lies in identifying the most frequently used algorithms for a particular application, and coding only those functions into microprogram routines. With effective microprogramming, a user can increase the overall performance of the CPU with a minimum conversion of software programs to micro-programs.

#### 1.1 GENERAL CHARACTERISTICS

The WCS feature augments the control store facility in the CPU with additional storage capacity that is alterable by the user. Its basic functional characterictics are:

- Capacity of 1K or 2K 64-bit words.

- WCS assembler to assemble firmware routines.

- Loader to load the assembled routines into the WCS.

- Facility for a Microcode Analyzer to display and monitor firmware sequencing and key data with the execution of each firmware step.

This feature does NOT replace the standard firmware, but provides a micorprogrammer with the opportunity to add to it.

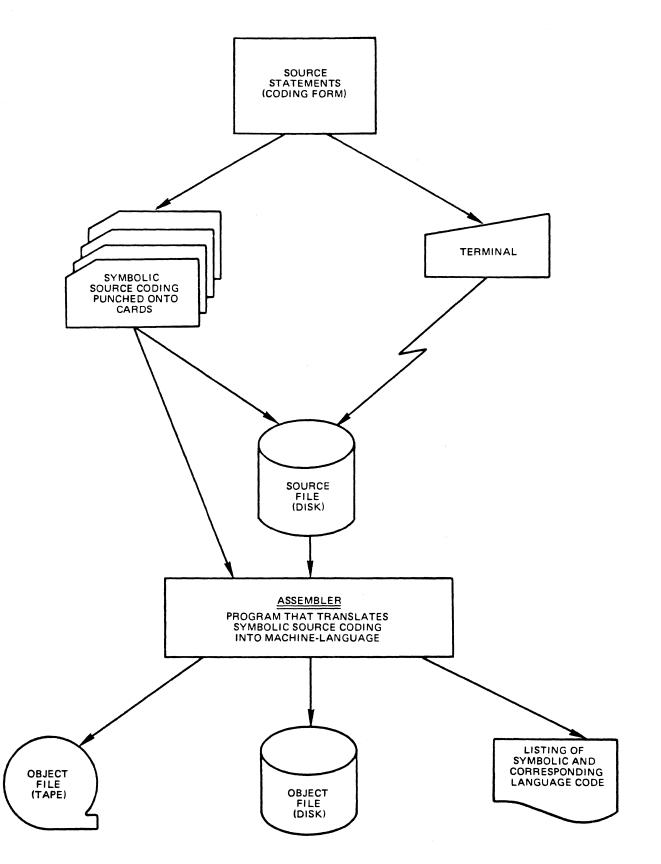

#### 1.2 USING THE WCS

All microprograms (firmware routines) are initially processed through the WCS assembler, which accepts mnemonic source input and creates object files suitable for loading into control store. The WCS loader accepts the assembler generated object code and loads it into the WCS. When User Generic instructions are processed in the CPU, control is passed from the standard firmware to the user firmware in the WCS, where control of the CPU is maintained until completion of the user microroutine. Upon completion, the user firmware returns CPU control to the standard firmware. The entry point into the standard firmware is normally at the starting location of a microroutine used to fetch the next procedure word (i.e., next instruction). However, the user can specify any return address. It should be noted that while user firmware is in control of the CPU, the user is responsible for maintaining software service routines, such as polling for interrupts, testing for traps, etc.

Writing microprograms should be performed in a systematic and orderly manner. The user should:

- 1. Define the function of each new instruction.

- Acquire a good working knowledge of CPU functions, characteristics, and limitations.

- Define the task(s) the hardware must perform, such as drawing a cycle on a screen, and design a hardware algorithm to perform the task(s).

- Determine the firmware steps required to implement the subject algorithm.

NOTE

A firmware step can perform several parallel operations. Hence, a microprogrammer who may tend to think in terms of sequential programming operations, can save considerable steps and timing in the microprogram by combining the applicable operations into one step, thus taking maximum advantage of the parallel operation, as well as writing a more efficient microprogram. For example, an Add and a Branch operation can be combined into a single firmware step instead of two steps.

5. Enter each firmware step as a source statement on a suitable coding form.

- Transcribe each source statement onto punched cards, or enter each statement directly onto a disk file via an online terminal.

- 7. Process the source file through the WCS assembler to obtain a machine-language object file, and output the object file to disk or magnetic tape. This operation also produces a combined listing of the source file, object file, and assembler diagnostic messages for use during debugging.

- Load the object file into the CPU for analysis and debugging.

A Microcode Anaylzer is available that selectively displays pertinent CPU and WCS information for use in debugging microprograms. Included are the control facilities to single step the CPU through a microprogram, to set up a halt address that halts the CPU at any specified address, and to display the last 16 steps executed by the CPU.

Ę

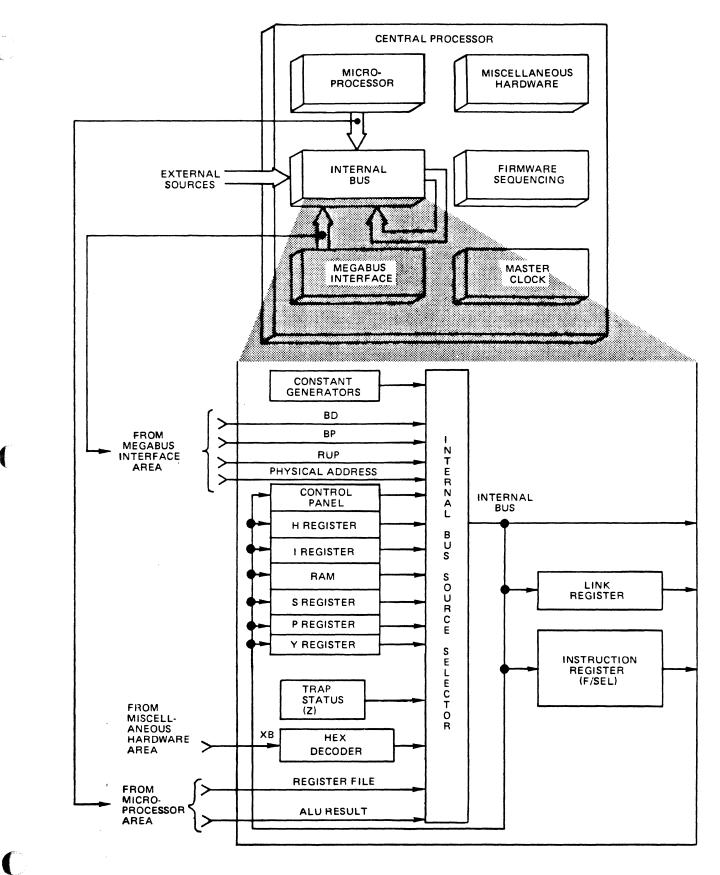

The microprogrammer must know the hardware configuration in use to properly program the firmware. An understanding of the function of each unit and its relation to the entire system will make the task easier.

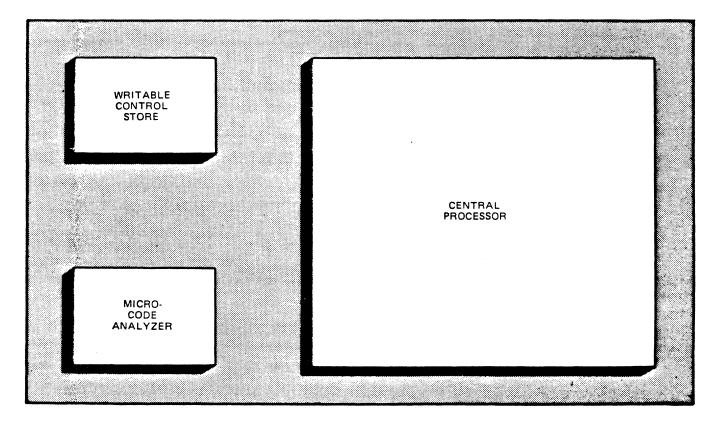

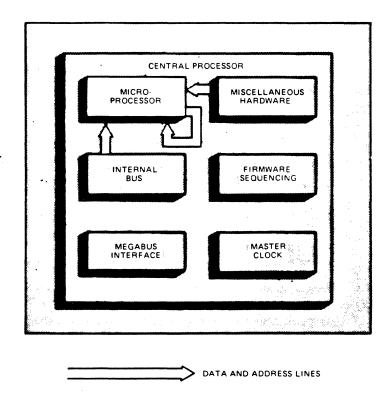

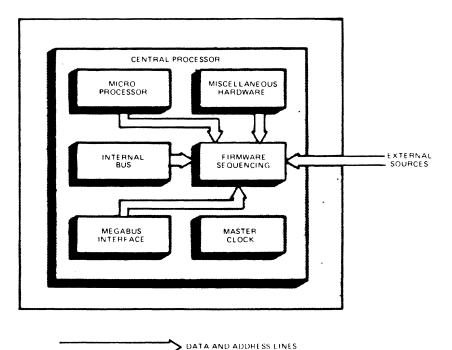

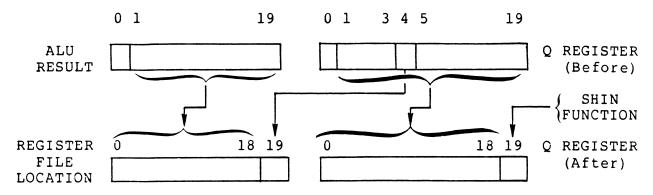

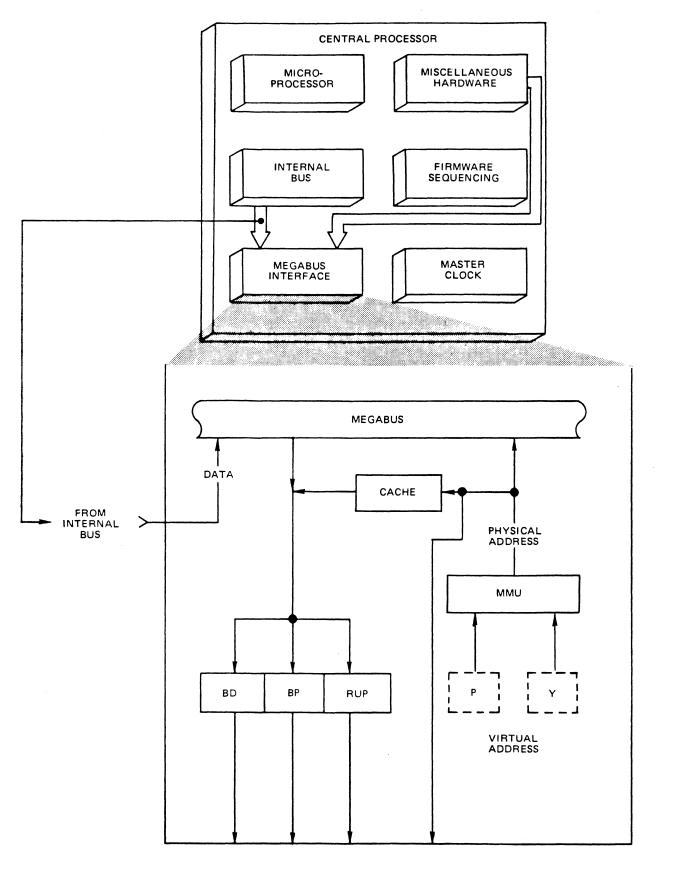

The hardware required to implement user generated microprograms consists of two basic units (see Figure 2-1); the Central Processor Unit (CPU) and the Writable Control Store (WCS). The Microcode Analyzer is a tool to aid microprogram debugging.

Figure 2-1 Hardware Configuration

The CPU is the computing and control portion of the Level 6 system, which processes the data and address information required by the microprogram. It controls not only the flow of information within the CPU but also the flow of data between the CPU and other units of the Level 6 system. Control over system operations is accomplished by selecting, interpreting, and controlling execution of all software instructions.

The WCS provides a variable extension of the native control store, which manipulates the central processor hardware. The WCS firmware functions as an extension of the native control store firmware, manipulating the CPU hardware in exactly the same manner as the native firmware. The WCS firmware is not a replacement for the standard firmware used to implement the base instruction set, but provides the user with the opportunity to add to it.

Key features of the CPU in the microprogramming environment, in addition to the 26 software-visible registers, are a number of data paths, firmware registers, and control flops; some of which are dedicated to specific functions, either by hardware structure or by native firmware usage. The CPU registers differ in length, functionality (shifting, counting, etc.) and ability to communicate with other CPU elements and the Level 6 system. Regardless of length, the bits of each register or data path are numbered from left (most significant bit) to right (least significant bit), starting with zero. Thus, a 4-bit register would have bits numbered 0 through 3, while a 20-bit register or data path would have bits numbered 0 through 19.

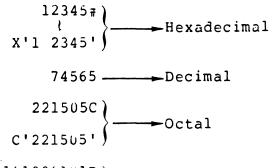

All addresses and many other values in this manual are expressed in hexadecimal (base 16) notation, using the digits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F. When there is any danger of ambiguity between hexadecimal and decimal numbers, the hexadecimal number is written in this manual using the pound sign (#) as a suffix.

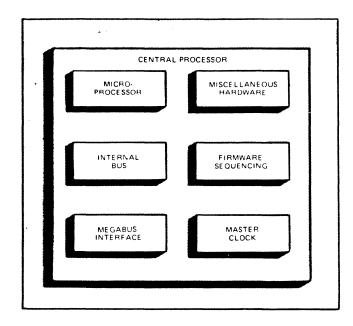

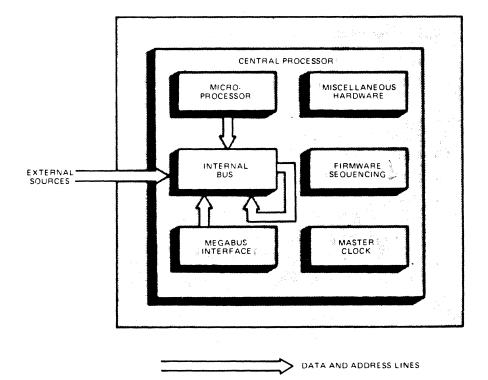

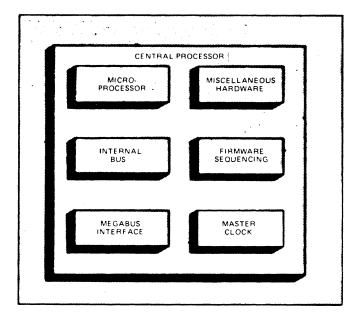

The registers, flops, data paths, and processing elements that comprise the CPU are divided into six functional areas: microprocessor, internal bus, Megabus\* interface, miscellaneous hardware, firmware sequencing, and master clock (see Figure 2-2). Each of these areas is controlled by a distinct set of microinstructions, which are described in detail in Section Three.

The remainder of this section describes:

- The six areas of the CPU

- Entering and leaving the WCS

- Use of the CPU registers, counters, and control flops.

\*Trademark of Honeywell Informations Systems, Inc.

2-2

Figure 2-2 Central Processor Area

2.1 MICROPROCESSOR AREA

0

The microprocessor area (see Figure 2-3) performs the arithmetic, logical, and shift operations required by the Level 6 system, including storage of operands for subsequent use by the microprogram and over half of the software visible registers.

Figure 2-3 Microprocessor Area

2-3

The interface to the microprocessor area from the internal bus area enables processing of operands from CPU areas that are external to the microprocessor area. The microprocessor area includes a register file that provides storage for sixteen 20-bit registers. Among these are software visible registers Rl through R7 and Bl through B7. Results of the microprocessor operations can (optionally) be stored within the microprocessor area, but regardless of whether or not these storage facilities are used, the results are available for testing and/or distribution (via the internal bus) to destinations outside the microprocessor area.

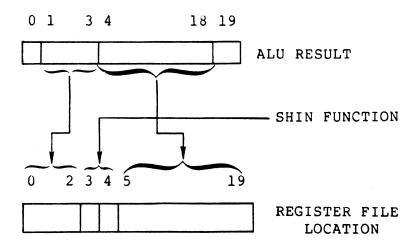

#### 2.2 INTERNAL BUS AREA

The internal bus area (see Figure 2-4) selects data from any one of several sources, and makes the data available to destinations both inside and outside the internal bus area.

Figure 2-4 Internal Bus Area

Elements that functions as internal bus sources include:

- Microprocessor outputs

- Sixteen additional 20-bit registers (RAM)

- Megabus buffer registers

- Constant-generation facilities

- Other sources.

Elements (within the internal bus area) that may serve as destinations for the internal bus data include:

• 16 RAM registers

(

- Memory address register and program counter

- Indicator register

- Other registers.

In general, the internal bus microinstruction permits selecting a single source and optionally delivering copies to one destination in each of the four categories previously listed. Internal bus data are also available for use by the other CPU areas.

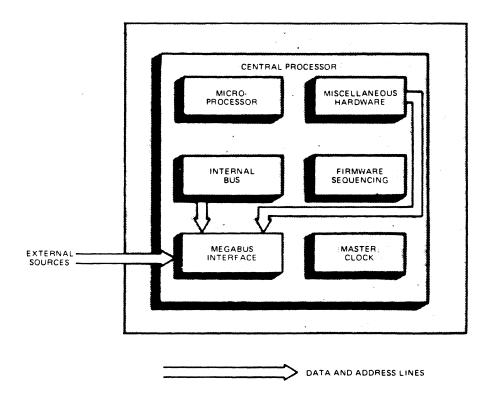

#### 2.3 MEGABUS INTERFACE AREA

Megabus cycles originating from the CPU are processed by the Megabus interface area (see Figure 2-5). For example, if the CPU wants to store a word in main memory, it sends the word together with its memory address (via the Megabus interface area) down the Megabus to main memory.

Figure 2-5 Megabus Interface Area

The six types of communication permitted over the Megabus are: (1) memory read request, (2) I/O read request, (3) read response, (4) memory write, (5) I/O write, and (6) interrupt. The microprogrammer can use combinations of these Megabus operations depending on the type of communication desired with other units of the Level 6 system.

#### NOTE

Communication types (1), (2), (4), and (5) are subject to control by the Megabus interface area, while types (3) and (6) are controlled by the internal bus area.

The interfaces among the internal bus, miscellaneous hardware, and Megabus interface areas enables the sending of data, address, and control information to the Level 6 Megabus from CPU areas that are outside the Megabus interface area.

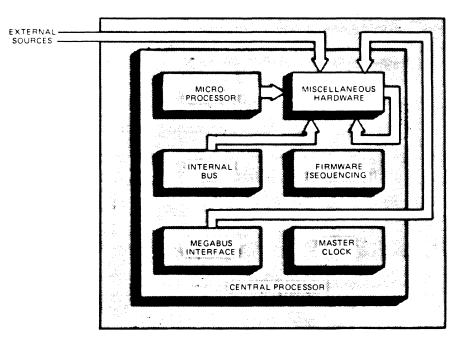

#### 2.4 MISCELLANEOUS HARDWARE AREA

The miscellaneous hardware area (see Figure 2-6) includes the remaining control flops and registers required by the CPU.

DATA AND ADDRESS LINES

Figure 2-6 Miscellaneous Hardware Area

The interface to the miscellaneous hardware area from the microprocessor, internal bus, and Megabus interface areas permit the microprogrammer to alter the state of the various control elements using sources both internal and external to the miscellaneous hardware area. These control elements modify the actions of other CPU areas, and can also be used to save signals generated in the current firmware step for use in subsequent firmware steps. For example, if the microprogrammer wants to postpone a firmware branch based on whether or not an arithmetic operation produced overflow, the overflow signal from the microprocessor area can be used to alter the state of a control flop within the miscellaneous hardware area. The state of the control flop can later be used as the test conditon for a firmware branch operation.

#### 2.5 FIRMWARE SEQUENCING AREA

The firmware sequencing area (see Figure 2-7) provides the next firmware address for the control store. Every firmware step specifies a test condition that interrogates various flops and signals from other CPU areas to determine which of two alternate addresses is the next firmware address. Unconditional branching is supported by a test condition that always evaluates "false".

DATA AND ADDRESS EINES

Figure 2-7 Firmware Sequencing Area

There are two addressing modes; Transparent and Sequential. In the Transparent mode, the mode used by the native firmware, every firmware step explicitly specifies the address of its successor. The Sequential mode appears more like typical software in that control generally proceeds to the next sequential location. The Transparent mode makes it possible to produce more compact code, whereas the Sequential mode is easier to learn.

#### 2.6 MASTER CLOCK AREA AND TIMING CONSIDERATIONS

The master clock area (see Figure 2-8) generates the timing signals necessary for proper operation of the CPU.

Figure 2-8 Master Clock Area

The timing signals distributed throughout the CPU provide four clock cycles that differ only in the duration of the cycle. The duration of the clock cycle for each firmware step is selected by the firmware assembler to provide the fastest performance consistent with reliable operation of the hardware. In rare circumstances, it will be necessary for the microprogrammer to override the assembler clock controls. This action will be required when the duration of a clock cycle must be increased to accommodate conditions arising from the actions of a prior firmware step.

All firmware controlled registers and flops in all areas of the CPU, with the sole exception of the 12-bit instruction register (F), are loaded, cleared, incremented, and/or shifted synchronously at the end of the firmware step calling for such action(s). Any testing, copying, etc., dependent on the content of a register that is being altered in the same firmware step, may be assumed to operate on the current contents of the register (i.e., the register contents before being altered by the current firmware step), except as explicitly noted.

Special timing considerations apply to firmware steps involving Megabus read request or Megabus write operations. Read requests are not generally completed until well into the next firmware step, imposing some restrictions on the microprogrammer. If the read request is not immediately followed by a firmware step that uses the response, the address selection must be maintained during the first step following the read request step. The acknowledge signal from the Megabus may be copied and/or tested during the firmware step immediately following the read request step.

2-8

During Megabus write operations, the acknowledge signal from the Megabus is received in time to be copied within the same firmware step, but not early enough to affect firmware sequencing reliably (refer to subsection 3.3).

A different situation exists regarding read responses (via the Megabus) to a CPU request. If the response arrives before the firmware is ready to use it, the data are buffered until requested. If the firmware attempts to use the data before the response has been received, the interface hardware automatically stalls the CPU master clock until the data arrives. The microprogrammer must avoid requesting data from a Megabus buffer if the read request was rejected; there is no limit to the patience of the master clock awaiting data that will not be received.

#### 2.7 ENTERING AND LEAVING THE WCS

To minimize timing problems when transferring microprogram control from native control to the WCS, or vice versa, advantage is taken of the synchronization capability already designed into the Megabus interface area. Control is transferred by causing the CPU to issue a Megabus cycle (I/O write) addressed to the WCS. By properly timing its acceptance of this command, the WCS hardware automaticlly assures a clean transfer of control.

Native firmware performs the above operation whenever the first word of an instruction lies in the range 0080# through 00BF#. The location to which control is transferred is one of the first 16 locations in the WCS; the specific location is identified by the least significant hexadecimal digit of the instruction word. The content of the various CPU registers and flops at the time of entry into the WCS is described in subsection 2.8.

When it is desired to return control from the WCS to the native control store, the user must create the appropriate I/O control word (with the WCS channel number and a function code of 25#) and transmit this command to the Megabus, simultaneously specifying the native control store address to which control should return (refer to examples 6 and 7 in subsection 3.7). Normally, return is to location 020# for the next instruction fetch operation.

Trap conditions of two kinds can occur:

- Conditions detected by hardware during Megabus cycles.

- Conditions detected by firmware test and branch operations.

The first category includes:

- Bus parity errors, memory parity errors, and uncorrectable errors detected by the memory Error Detection and Correction (EDAC) logic. These are sensed by the CPU when the bus data are sourced to the internal bus.

- 2. References to unavailable resources. These are sensed by the CPU during a write cycle, or during the firmware step following a read request cycle.

- 3. Illegal addresses. These are detected by WRAP testing (refer to subsection 2.8.2 - WRAP Control Flop), or by the Memory Management Unit (MMU); sensing of illegal addresses by the CPU is timed similarly to that of unavailable resource references.

When any of the above trap conditions are encountered, hardware forces the firmware to location 000 in the native control store; this is the starting address for the native firmware sequence that analyzes the trap condition and generates an appropriate trap.

All other trap conditions are considered under the second category, i.e., they are detected by conditional firmware branches as required by the functional specification applicable to the instruction being executed. When such a trap is detected, the firmware should exit to the location TRAP (33B#) in the native firmware, after first ensuring that:

- RAM location 0 contains the instruction word to be reported\*.

- The XB and CTR register contents are appropriate for the Z-word\*.

- The Q register contains the address (if any) to be reported in the A-word\*.

- Register BU contains a trap vector code equal to 40# minus the desired trap number\*.

<sup>\*</sup>Refer to Honeywell Level 6 Minicomputer Handbook (Order Number AS22) for a description of Trap Save Area contents. The following subsection defines all CPU registers, counters, and control flops that are visible to the microprogrammer, including those registers and counters mentioned above.

#### 2.8 USE OF CPU ELEMENTS

The CPU registers, counters, and control flops that are visible to the microprogrammer can be classified into four categories:

- Software Visible (SWV)

- Firmware Dedicated (DEDIC)

- Working Storage (WORK)

- Autonomous (AUTO).

The possible uses for elements in the above categories are described in the following subsections and summarized in Table 2-1.

### 2.8.1 Software Visible

The registers in this category should not be altered except as explicitly required by the functional definition of the current instruction.

#### Registers Dl through D7

Registers Dl through D7 reside in bits 4 through 19 of microprocessor register file locations 1 through 7 (bits 0 through 3 of each register are not software visible, but are not usually useful as working storage).

#### Registers Bl through B7

Registers Bl through B7 reside in microprocessor register file locations 9 through F.

#### Register Ml through M7

Registers Ml through M7 reside in bits 12 through 19 of internal bus RAM locations 1 through 7 (refer to subsection 2.8.2 -RAM locations 4 and 6 and subsection 2.8.3 - RAM locations 1, 3, 5, and 7 for the use of other bits in these locations).

#### T and RDB Registers

The T and RDB registers reside in RAM locations A and B (respectively).

#### S and I Registers

<u>ید</u>

The S register contains the system status and security codes for use within the CPU. The I register contains the CPU indicators.

#### P Register

The P register normally functions as a program counter, but can be freed for use as a working register (refer to subsection 2.8.3 - P register).

#### 2.8.2 Firmware Dedicated

The registers and flops in this category contain control information and/or trap context. They should be loaded only with the information described herein so that the native functionality is preserved. They can also be used as sources for this information.

#### RAM Location 0

This RAM location contains the instruction word to be reported when a trap occurs.

#### RAM Locations 4 and 6 (bits 4 through 11)

Bits 4 through 11 of these RAM locations contain the mode information for:

- 1. Enabling the Real Time Clock (RTC).

- 2. Enabling the Watch Dog Timer (WDT).

#### RAM locations C and D

RAM locations C and D contain pointers to the most recently accepted Commercial Instruction Processor (CIP) and Scientific Instruction Processor (SIP) instructions, respectively. Each location must remain NULL if the corresponding external processor is not configured.

#### RAM location F

This RAM location must be NULL except when it points to the next word of procedure, freeing the P register for use as a working register (refer to subsection 2.8.3 - P Register).

#### CTR Register

The CTR register is a 4-bit counter that indicates the number of procedure words consumed in the processing of the current instruction. It is incremented (or cleared) every time the P register is incremented (refer to subsection 2.8.3 - P register).

#### XB Register

The XB register is a 4-bit shift register that supplies trap context information regarding indexing of bit or byte operations (refer to subsection 2.8.3 - XB register).

#### WRAP Control Flop

Ę

The WRAP control flop facilitates the checking of addressarithmetic firmware to detect attempts to exceed the 20-bit capacity of the address registers. If the WRAP control flop is on, any access to the Megabus (read request or write operation) will result in the transmission of an illegal address or I/O channel number. This action results in no response via the Megabus, which is interpreted as an "unavailable resource".

Whenever an index value or other displacement is to be added to a base address, the algebraic sign of the displacement should first be copied into the SIGN control flop. Then, the address modification can be performed, using the sign-extension capabilities of the microprocessor area (refer to subsection 3.1). Simultaneously, the carry signal from the most significant end of the microprocessor should be compared with the state of the SIGN control flop, and the comparison result copied to the WRAP control flop.

#### Read-Modify-Write Control Flop (RMWF)

RMWF is set to One when memory has been locked for the duration of a read-modify-write operation. RMWF is set and cleared by the Megabus interface area CHGLOCK operand (refer to subsection 3.3) if the F register contains one of the following instruction codes (refer to subsection 2.8.3 - F/SEL Instruction Register):

> F = 002, 003, 006, 007#, or 880#  $\leq$  F  $\leq$  897#, or 8A0#  $\leq$  F  $\leq$  887#.

#### LOAD, TRAFFIC, and PANOK Control Flops

These flops communicate control information between firmware and the operator. Although they are described here for completeness, it is not anticipated that normal user firmware will involve any of them.

The LOAD flop can be set and cleared both by the operator and by firmware in the miscellaneous hardware area. During the system startup operations, LOAD is normally set by the operator and, when bootload action is completed, cleared by firmware. Thereafter, this flop usually remains off, but is sometimes set briefly by firmware as a means of preventing a trap to location 000 when a Megabus cycle is addressed to a possibly unavailable resource. LOAD must never be left on at the end of an instruction.

The TRAFFIC flop is loaded by firmware in the miscellaneous hardware area to control the corresponding indicator on the control panel. However, the flop is held off by hardware unless the control panel is in the Run mode. As the native firmware extracts the first word of each instruction, the word is tested to determine if the instruction op-code is HLT. The result of this test is transferred (via the ZERO flop) to the TRAFFIC flop (subject to hardware override if the Run mode is not in effect).

The PANOK flop synchronizes the servicing of operator requests. It is set to Zero whenever the CLEAR or EXECUTE pushbutton is depressed and when in Register-Change mode, a hexadecimal key is depressed. This flop is set to One by the firmware that services the request, and is used to prevent multiple servicing of a single key-stroke.

#### EFFRING, NONPROC, NOCHEK, SEGERR, and PROV Controls

These signals and flops support normal MMU operations, permit temporary alteration of access rules, and reports errors detected by the MMU.

EFFRING is a 2-bit register containing the "effective ring number", which the MMU uses to determine the degree of privilege appropriate to the current instruction, and against which memory access requests are tested. Native firmware loads EFFRING from the S register RING field at the start of each instruction. Correct procedure requires that EFFRING be modified to decrease its privilege level whenever, in the course of formulating an address, it uses data that might have been generated by a less privileged program.

NONPROC establishes a temporary change in the rules of access. Memory references which use the P register as the address source normally require "Execute" permission; when NONPROC has been set, they require only "Read" permission (refer to subsection 2.8.3 - P register).

NOCHEK establishes a temporary suspension of the rules of access (it does not affect the mapping of segmented virtual addresses to physical, nor the detection of illegal, non-existent addresses). The intent of this functionality is to remove restrictions on memory access by system firmware (interrupt and trap handler, RTC/WDT service, panel routine, etc.).

SEGERR signals that the MMU has detected an error in a virtual address; the referenced segment is not valid, its size has been exceeded, or a protection violation has been detected. If SEGERR occurs during a memory reference, it causes the transmission of an illegal physical address. This action results in no response via the Megabus, which is interpreted as an "unavailable resource". If no memory reference or access-rights test (refer to subsection 3.3.3. - MMURDACC, MMUWRACC) is requested, the SEGERR signal is ignored.

PROV signals that the MMU has detected a protection violation (failure of access rights check) on an otherwise legal address (i.e., an address in a valid segment and within the segment size). If a protection violation occurs during a memory

reference, the PROV flop is locked in the set state until cleared by the firmware function NOCHEK (this function is normally issued by the trap generation firmware). If a protection violation occurs during a firmware step that explicitly requests an accessrights test, the next firmware step may copy PROV to the MISC control flop.

#### NEWXR Control Flop

C

The NEWXR flop is used in the Transparent mode to distinguish between reentrant invocations of the XR "splatter" branch. This flop is set when the SEL register is loaded from the internal bus (e.g., during instruction fetch); it is cleared when a branch is performed to XR, XE, XW, or XF (refer to subsection 3.5), and when the WRAP flop is set or cleared (refer to subsection 3.4). The effect of NEWXR is shown in Appendix E.

#### 2.8.3 Working Storage

These are the registers and flops available to the microprogrammer for temporary storage of operands, imtermediate results, control information, etc., during execution of each instruction. Their contents cannot generally be depended on to retain information between instructions, especially in the presence of asynchronous actions such as interrupts, unexpected traps, and RTC/WDT service requirements.

#### RAM Location 8

This RAM location initially\* contains a pointer to the next word of procedure (copy of P register), but may be altered as desired.

#### RAM Locations 9 and E

These RAM locations initially contain no predictable information.

#### RAM Locations 1, 3, 5, and 7 (bits 0 through 11)

Bits 0 through 11 of these RAM locations normally contain zeros, and are unused by the native firmware. These fields are not easily altered because bits 12 through 19 of these locations contain software visible data (M registers) that must be preserved. They do, however, have the advantage of being able to retain formation between instructions and for prolonged periods.

<sup>\*</sup>In this context, "initially" refers to the instant when the native firmware transfers control of the User Generic execution to WCS firmware.

### Register File Locations 0 and 8

Register file locations 0 and 8 are called registers D0 and B0, respectively, and initially contain no predictable information.

#### Q Register

The Q register initially contains a pointer to the first word of the current instruction, but may be altered as desired.

#### F/SEL Instruction Register(s)

The F/SEL register initially contains the first word of the current instruction, but may be altered as desired. Specifically, it may be useful to copy all or a portion of subsequent instruction words into the instruction register to facilitate decoding and/or branch control.

#### NOTE

Numerous mappings of the contents of the instruction register are available as listed in Tables 3-8, 3-9, and Appendix E. These instructions are designed for the native repertoire; their utility to the WCS microprogrammer will depend to a large extent on the functional specification of the new instructions, and on their similarity to the native instructions.

#### Y Register

The Y register initially contains no predictable information. This register is primarily designed to hold nonprocedural addresses (or I/O control words) for transmission to the Megabus; however, during periods of inactivity in the Megabus interface area, the Y register may be used for other tasks.

#### H Register

The H register initially contains no predictable information. The principal functions of this register are to:

- Facilitate the handling of halfwords (bytes) by accepting l6-bit quantities from the internal bus, and later delivering them back to the internal bus with the two halves inter-changed.

- Assist the expansion of a 8-bit algebraic quantities to 16 bits.

- Retrieve 20-bit addresses from two adjacent words in memory.

#### LINK Register

Ę

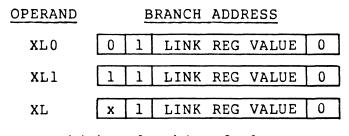

The LINK register initially contains no predictable information. Loaded from the internal bus, this register is usable only by the firmware sequencing area: Transparent mode XL, XLO, and XL1 or Sequential mode LBRANCH.

#### MISC, SHIN1, SHIN2, SIGN, and ZERO Control Flops

These flops are initially cleared to zero.

#### DDLEQ0 Control Flop

This flop initially contains no predictable information.

#### XB Register

The XB register is initially cleared to zero. Depending on the functional definition of the current instruction, the contribution of this register to the Z-Word\* may include no useful information. In this event, the XB register may be used for working storage.

#### P Register

As previously indicated, the P register can be freed of its normal procedure-pointing duties, and used for any purpose desired. To accomplish this the user must first copy the content of P into RAM location F (RAMF) and must notify the MMU to treat subsequent procedure references as data read operations for the purpose of checking access rights. The P register may then be loaded and used as desired. If an unexpected trap should occur (e.g. a parity fault), the native firmware will report the content of RAMF in the trap context in lieu of P. Similarly, the Z-word\* will report an instruction size of one, rather than the content of CTR. Before returning control to native firmware (e.g., at the end of the instruction), the user must copy the procedure pointer from RAMF back to the P register, and then clear RAMF to NULL.

The user may find it worthwhile to invest the overhead required by the previous paragraph if the User Generic instructions to be implemented involves reading a long consecutive nonprocedural data string from memory. The relative economy of time and code space possible when using P as the address register for such an operation can quickly repay the investment.

\*Refer to the Honeywell Level 6 Minicomputer Handbook (Order Number AS22) for a description of Trap Save Area contents.

#### 2.8.4 Autonomous

These buffer registers and flops are set by external agencies (i.e., agencies which are not firmware controlled), and supply information for firmware use.

#### Acknowledge (ACK) Control Flop

The ACK control flop remembers whether the most recent Megabus action was accepted or rejcted: if ACK is ON, the action was accepted, if ACK is off, the action was rejected.

#### Megabus Data Buffer (BD)

The Megabus data buffer retains the data received from memory or an I/O channel in response to the most recent CPU read request. The content of BD remains valid, and may be reused, until the firmware issues the next read request or references the Megabus procedure buffer.

#### Megabus Procedure Buffer (BP)

The Megabus procedure buffer supplies the next procedure word from memory (i.e., the word pointed to by the P register). BP can be read only once per word because this read operation increments the P register.

#### Megabus Interrupt Buffer (RUP)

The Megabus interrupt buffer retains the latest external interrupt received (i.e., one not involved with RTC, WDT, or LEV actions). The content of RUP is valid while the Interrupt Busy (INTBSY) flop is on.

#### YELLOW and PARER Megabus Data Error Flops

The YELLOW and PARER flops signal detection of an error in memory or on the Megabus. YELLOW remembers if at least one data error was corrected by memory EDAC hardware since the last interrogation of this flop; YELLOW is cleared each time it is interrogated by the firmware. PARER remembers if the most recent Megabus buffer reference (BD or BP) reported either a Megabus parity error or a data error not correctable by memory EDAC hardware. Unless the control panel is in Load, Read, or Write mode, the setting of PARER forces the firmware to native location 000 for suitable trap generation (refer to subsection 2.7).

#### EXTRAP, INTBSY, and TICK Service Request Flops

The EXTRAP, INTBSY, and TICK service request flops are set by hardware to signal a requirement for a break in firmware flow. If execution of the current instruction is lengthy, as defined below, the user is responsible for polling these flops frequently enough to avoid degradation of system performance. The native firmware performs this polling while extracting the first word of each instruction. It is recommended that, when polling detects such a request, the user should execute a branch to suitable firmware which will prepare the current instruction to be resumed or restarted, as appropriate, then exit to native firmware (location 020#).

EXTRAP is true when one or more external processors (CIP or SIP) has detected a trap condition. User firmware that does not communicate with CIP or SIP need not poll EXTRAP. If a Megabus request to such a processor is rejected, the firmware should test EXTRAP to determine whether the rejection might have been caused by a trap. If not, the Megabus request can be repeated; otherwise, a return to native firmware is recommended. EXTRAP becomes false when all external processors with trap conditions have delivered their trap words.

INTBSY is set when an external interrupt of high enough priority is received and accepted by the CPU hardware. No further interrupts, regardless of priority, can be accepted until firmware services buffer RUP, reloads the level field in the S register, and clears INTBSY. This flop must be polled often enough to ensure the interrupt response perfomance appropriate to the application.

TICK is set every 8-1/3 milliseconds by a crystal-controlled oscillator in the CPU, signalling the need for service of the YELLOW logic, the RTC and/or WDT, and the control panel. TICK must be polled at least 120 times per second.

| <b>f</b> | · · · · · · · · · · · · · · · · · · · |       |                           |                                          |

|----------|---------------------------------------|-------|---------------------------|------------------------------------------|

| ELEMENT  | LENGTH                                | TYPE  | AREA                      | PRIMARY NATIVE<br>FIRMWARE USAGE         |

| ACK      | 1                                     | AUTO  | Megabus                   | Megabus Cycle Acknowl-<br>gement Storage |

| в0       | 20                                    | WORK  | Microprocessor            |                                          |

| B1-B7    | 20                                    | SW    | Microprocessor            | Base Registers                           |

| BD       | 16                                    | AUTO  | Internal Bus              | Megabus Data Read<br>Buffer              |

| BP       | 16                                    | AUTO  | Internal Bus              | Megabus Procedure Read<br>Buffer         |

| CTR      | 4                                     | DEDIC | Miscellaneous<br>Hardware | Count Instruction<br>Length              |

| D0       | 20                                    | WORK  | Microprocessor            |                                          |

| D1-D7    | <sup>#</sup> 20                       | SWV   | Microprocessor            | Data Registers (Rl-R7)                   |

Table 2-1 Use of CPU Elements (Sheet 1 of 4)

2-19

Table 2-1 Use of CPU Elements (Sheet 2 of 4)

| ELEMENT | LENGTH | TYPE  | AREA                                       | PRIMARY NATIVE<br>FIRMWARE USAGE                    |

|---------|--------|-------|--------------------------------------------|-----------------------------------------------------|

| DDLEQU  | 1      | WORK  | Miscellaneous                              | CIP Descriptor Length<br>Hardware                   |

| EFFRING | 2      | DEDIC | Megabus                                    | MMU Effective Ring<br>Number                        |

| EXTRAP  | 1      | OTUA  | *                                          | External-Processor<br>Trap                          |

| F       | 12     | WORK  | Internal Bus                               | Instruction MSB                                     |

| н       | 16     | WORK  | Internal Bus                               | Byte Swapping                                       |

| I       | 8      | SWV   | Internal Bus/<br>Miscellaneous<br>Hardware | Indicator Register                                  |

| INTBSY  | 1      | AUTO  | *                                          | Interrupt Busy Signal                               |

| LINK    | 8      | WORK  | Internal Bus                               | Firmware Sequencing                                 |

| LOAD    | 1      | DEDIC | Miscellaneous<br>Hardware                  | Inhibit Missing - Re-<br>source Recognition         |

| MISC    | 1      | WORK  | Miscellaneous<br>Hardware                  |                                                     |

| NEWXR   | 1      | DEDIC | Firmware<br>Sequencing                     | Distinguish Reentrant<br>XR Branch                  |

| NOCHEK  | 1      | DEDIC | Miscellaneous<br>Hardware                  | Inhibit MMU Access<br>Rights Checking               |

| NONPROC | 1      | DEDIC | Miscellaneous<br>Hardware                  | Inhibit MMU Execute<br>Checking                     |

| Р       | 20     | SWV   | Internal Bus                               | Program Counter                                     |

| PANOK   | 1      | DEDIC | Miscellaneous<br>Hardware                  | Acknowledge Panel<br>Request                        |

| PARER   | 1      | AUTO  | Megabus                                    | Bus Parity Error or<br>EDAC Uncorrectable<br>Error. |

| PROV    | 1      | DEDIC | Megabus                                    | MMU Protection Viola-<br>tion                       |

С

Table 2-1 Use of CPU Elements (Sheet 3 of 4)

|         | ELEMENT         | LENGTH        | TYPE          | AREA                      | PRIMARY NATIVE<br>FIRMWARE USAGE                        |

|---------|-----------------|---------------|---------------|---------------------------|---------------------------------------------------------|

|         | Q               | 20            | WORK          | Microprocessor            | 32-bit Shifts                                           |

|         | RAM0            | 20            | DEDIC         | Internal Bus              | Holds Copy of Instruc-<br>tion Word                     |

|         | RAM1-RAM7       | 20            | SWV<br>+DEDIC | Internal Bus              | Mode Registers (Ml-M7)<br>Plus Control Informa-<br>tion |

|         | RAM8-RAM9       | 20            | WORK          | Internal Bus              |                                                         |

|         | RAMA            | 20            | SWV           | Internal Bus              | Stack Pointer (T)                                       |

|         | RAMB            | 20            | SWV           | Internal Bus              | Remote Descriptor Base<br>Register (RDB)                |

|         | RAMC            | 20            | DEDIC         | Internal Bus              | CIP Instruction<br>Pointer                              |

| antes e | RAMD            | 20            | DEDIC         | Internal Bus              | SIP Instruction<br>Pointer                              |

| 4       | RAME            | 20            | WORK          | Internal Bus              |                                                         |

|         | RAMF            | 20            | DEDIC         | Internal Bus              | Usually Must Be Null                                    |

|         | RMWF            | 1             | DEDIC         | Megabus                   | Remember That CPU<br>Locked Memory                      |

|         | RUP             | 16            | OTUA          | Internal Bus              | Interrupt Word                                          |

|         | S               | 16            | SWV           | Internal Bus              | System Status Register                                  |

|         | SEGERR          | 1             | DEDIC         | Megabus                   | MMU Segment Error                                       |

|         | SEL             | 4             | WORK          | Internal Bus              | Instruction LSB                                         |

|         | SHIN1,<br>SHIN2 | 2             | WORK          | Miscellaneous<br>Hardware | Control Shift End<br>Effects                            |

|         | SIGN            | 1             | WORK          | Miscellaneous<br>Hardware |                                                         |

|         | TICK            | 1             | AUTO          | *                         | 8.3 MS Interval Mark                                    |

|         | TRAFFIC         | 1             | DEDIC         | Miscellaneous<br>Hardware | Control Panel<br>Indicator                              |

|         |                 | - <del></del> |               |                           |                                                         |

.

| ELEMENT | LENGTH | TYPE  | AREA                      | PRIMARY NATIVE<br>FIRMWARE USAGE |

|---------|--------|-------|---------------------------|----------------------------------|

| WRAP    | 1      | DEDIC | Miscellaneous<br>Hardware | Address-Wrap-Around<br>Storage   |

| ХВ      | 4      | DEDIC | Miscellaneous<br>Hardware | Subword Indexing, Hex<br>Decoder |

| У       | 20     | WORK  | Internal Bus              | Megabus Address<br>Register      |

| YELLOW  | 1      | Αυτο  | Megabus                   | EDAC-Corrected<br>Errors         |

| ZERO    | 1      | WORK  | Miscellaneous<br>Hardware | ALU Zero Result<br>Storage       |

Table 2-1 Use of CPU Elements (Sheet 4 of 4)

\*Not controlled by firmware.

# SECTION 3 - MICROINSTRUCTIONS

The CPU hardware is controlled by firmware words (steps), each step consisting of several microinstructions that manipulate the hardware to perform desired operations. The CPU can execute up to six microincstrucions simultaneously during any given firmware step, permitting simultaneous control over the six functional CPU areas: microprocessor, internal bus, Megabus interface, miscellaneous hardware, firmware sequencing, and master clock.

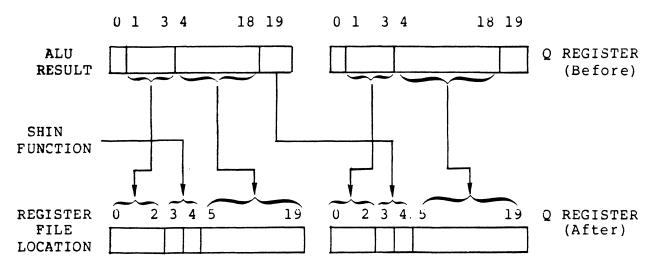

#### 3.1 MICROPROCESSOR AREA

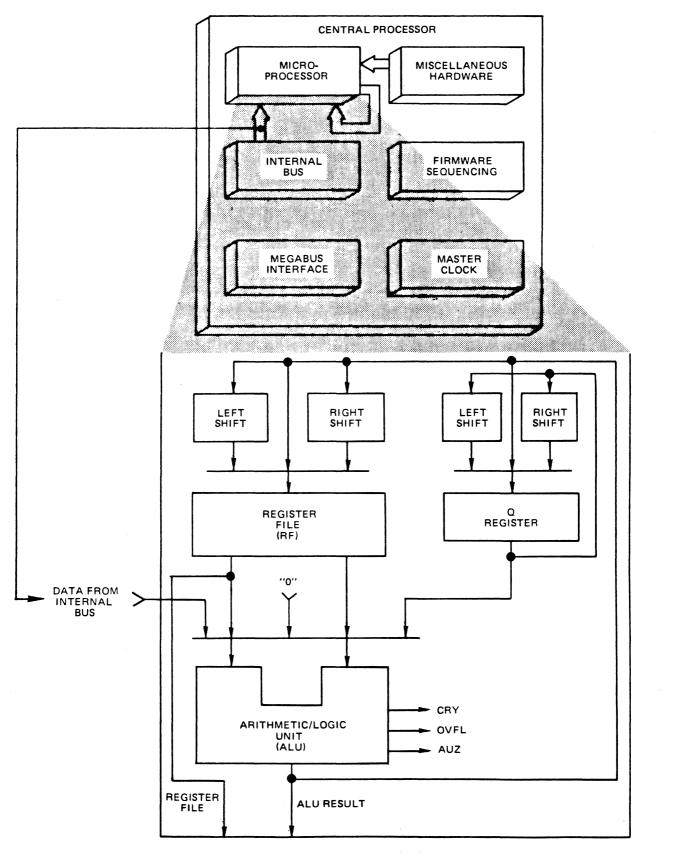

The principal elements of the microprocessor area (see Figure 3-1 include:

- Register File (RF)

- Q Register

- Arithmetic/Logic Unit (ALU)

- Shift Logic.

The register file is a memory consisting of sixteen 20-bit locations, numbered 0 through F. The first eight locations are designated as registers D0 through D7, while the last eight locations are designated as registers B0 through B7. Up to two of these registers may be addressed simultaneously to serve as sources and/or destination for the ALU. Simultaneously, the contents of one register file location may be made available to the internal bus area.

The Q register is an additional 20-bit register that is available as an ALU source and/or destination.

The ALU performs all CPU arithmetic and logical functions. It has two 20-bit inputs and one 20-bit output. The ALU output may be directed to a destination within the microprocessor and/or made available to the internal bus area. Three auxiliary signals are generated based on the ALU results: Carry (CRY), Overflow (OVFL), and Zero detect (AUZ). For the purpose of generating these signals, the ALU function may be treated as a 16-bit or a 20-bit operation as shown in the following listing; however, the actual arithmetic or logical operation is always 20 bits wide.

$\sim$  :

Figure 3-1 Microprocessor Area

| SIGNAL | 16-BIT                 | 20-BIT                                     | 16-BIT      | 20-BIT                                     |

|--------|------------------------|--------------------------------------------|-------------|--------------------------------------------|

|        | ARITHMETIC             | ARITHMETIC                                 | LOGICAL     | LOGICAL                                    |

| CRY    | Carry from bit<br>4    | Carry from bit<br>0                        | Undefined*  | Undefined*                                 |

| OVFL   | Overflow from<br>bit 4 | ALU result bit<br>0 in liew of<br>overflow | Undefined*  | ALU result<br>bit 0 in lieu<br>of overflow |

| AUZ    | =1 if ALU              | =l if ALU                                  | =1 if ALU   | =l if ALU                                  |

|        | result bits            | result bits                                | result bits | result bits                                |

|        | 4-19 = 0               | 0-19 = 0                                   | 4-19 = 0    | 0-19 = 0                                   |

\*Except for the logical AND function as described in subsection 3.1.3.

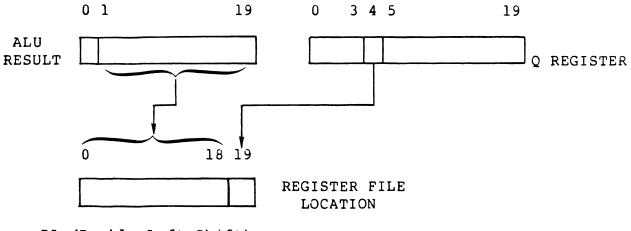

The shift logic is designed to perform single-bit left or right shifts on the 16 least significant bits of the ALU result before they are written into the register file. The Q register can be shifted simultaneously to facilitate operations on 32-bit quantities (refer to subsection 3.1.4).

# 3.1.1 Syntax

The microinstructions that affect this functional area control the Register File Arithmetic and Logic Unit (RALU). These microinstructions contain a function and up to four operands as follows:

function  $\triangle$  SRC1, SRC2, DEST, SHIFT

function  $\triangle$  SRC1, DEST, SHIFT

where:

SRC1 is an input source.

SRC2 is an additional input source.

DEST is the destination for results (optional operand).

SHIFT is the shift operand for results (optional operand).

#### 3.1.2 Microprocessor Sources and Destinations

Sources to the ALU may be any one (or two) of the following:

- Internal Bus (refer to subsection 3.2).

- Q Register

- Register File Location

- Another (or the same) Register File Location

- ZERO (20 bits, all zeros).

Destinations, if any, in the microprocessor may be to the following:

- Q Register

- Register File location.

Whether or not a microprocessor destination is specified, the ALU result, CRY, OVFL, and AUZ are available for simultaneous use by microinstructions in other areas. If SRC1, SRC2, and DEST all specify register file locations, DEST must be the same as either SRC1 or SRC2.

The possible sources and destinations for the microprocessor area are summarized in Table 3-1. Register file locations may be specified explicitly or as a function of fileds in the F/SEL instruction registers. The mnemonics are derived from the B-field (SEL register bits 1 through 3), the M-field (F register bits 9 through 11), and the N-field (F register bits 1 through 3). If the firmware step just previously executed altered the contents of SEL, those operands that depend on fields in SEL will use its previous contents (i.e., the contents before SEL was altered at the end of the firmware step just previsously executed).

If two register file locations are selected by operands SRCl, SRC2, and/or DEST, they must both be members of the same group, where the available groups are:

- D0, D3, D6, D7, B0, B3, B6, and B7.

- D0, D1, D4, D5, B0, B1, B4, and B5.

- D0, D2, D6, B0, B2, and B6.

- D0, DN, DN3, DNE, B0, BN, BN3, and BNE.

- D0, DB, DB3, DBE, B0, BB, BB3, and BBE.

- D0 DB, DB3, DBE, and REGSEL.

- D0, DM, DM3, DME, B0, BM, BM3, and BME.

Other restrictions on the selection of one of the microprocessor source operands are imposed occasionally by the simultaneous action of microinstructions in other areas. To facilitate cross-referencing, it is necessary to introduce the concept of "restricted selection." A microprocessor source operand is designated a restricted selection if it specified a register file location, and:

- it is the second operand of microinstruction ANDC, ADDSE, or ADD1SE, or

- it is also the internal bus source (refer to subsection

3.2.2 Register File Locations), or

- the destination is a different register file operand, or

- the other source is the Q register, or

- the other source is the internal bus, or

• the other source is a register file operand that does not satisfy the restricted-selection rule(s) in question (i.e., if both sources are register file locations, at least one must satisfy the restricted-selection rule).

(

# NOTE

The restricted selection concept applies only when a simultaneous microinstruction defines a restricted selection rule.

When 20-bit versions of CRY, OVFL, and AUZ are used, and the function is neither ADDSE nor ADDISE, the restricted-selection source must be a D register (except as selected by REGSEL).

| Table 3-1 | ALU Source | e and Des | tination | Operands |

|-----------|------------|-----------|----------|----------|

|           |            | (Sheet 1  | of 2)    |          |

| OPERAND | EXPLANATION                                                         |

|---------|---------------------------------------------------------------------|

| в0-в7   | RALU Base Registers B0 through B7 (register file locations 8-F)     |

| BB      | RALU Base Register (B0 through B7) specified by SEL(1-3).           |

| BB3     | RALU Base Register (B0 through B3) specified by SEL(2-3).           |

| BBE     | RALU Even Base Register (B0, B2, B4, or B6) specified by SEL(1-2).  |

| BI      | Internal Bus (source only).                                         |

| ВМ      | RALU Base Register (B0 through B7) specified by F(9-11).            |

| вмз     | RALU Base Register (B0 through B3) specifiefd by F(10-11).          |

| BME     | RALU Even Base Register (BU, B2, B4, or B6) specified by F(9-10).   |

| BN      | RALU Base Register (B0 through B7) specified by $F(1-3)$ .          |

| BN 3    | RALU Base Register (B0 through B3) specified by $F(2-3)$ .          |

| BNE     | RALU Even Base Register (B0, B2, B4, or B6) specified by $F(1-2)$ . |

| D0-D7   | RALU Data Registers D0 through D7 (register file locations 0-7)     |

3-5

| OPERAND | EXPLANATION                                                                      |

|---------|----------------------------------------------------------------------------------|

| DB      | RALU Data Register (D0 through D7) specified by SEL(1-3).                        |

| DB3     | RALU Data Register (D0 through D3) specified by SEL(2-3).                        |

| DBE     | RALU Even Data Register (D0, D2, D4, or D6) specified by SEL(1-2).               |

| DM      | RALU Data Register (D0 through D7) specified by F(9-11).                         |

| DM3     | RALU Data Register (D0 through D3) specified by F(10-11).                        |

| DME     | RALU Even Data Register (D0, D2, D4, or D6) specified by F(9-10).                |

| DN      | RALU Data Register (D0 through D7) specified by $F(1-3)$ .                       |

| DN 3    | RALU Data Register (D0 through D3) specified by $F(2-3)$ .                       |

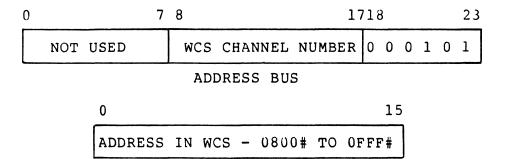

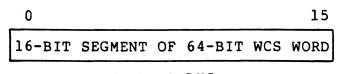

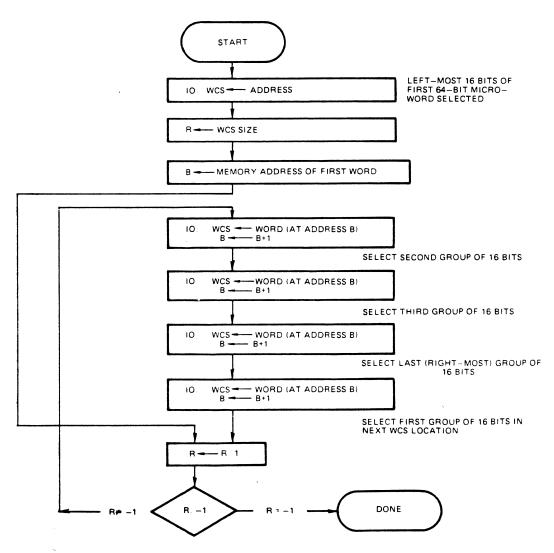

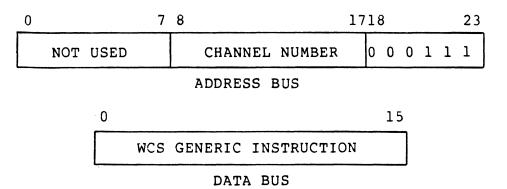

| DNE     | RALU Even Data Register (D0, D2, D4, or D6) specified by $F(1-2)$ .              |