# **AP-830**

# APPLICATION NOTE

# Pentium® II Xeon<sup>TM</sup> Processor/Intel® 450NX PCIset AGTL+ Layout Guidelines

June 1998

Order Number: 243790-001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Pentium<sup>®</sup> II Xeon<sup>™</sup> processor and the Intel<sup>®</sup> 450NX PCIset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com

Copyright © Intel Corporation 1998.

\* Third-party brands and names are the property of their respective owners.

### AP-830

# intel®

# CONTENTS

## PAGE

| 1.0. INTRODUCTION5                                                     |   |  |  |  |  |  |

|------------------------------------------------------------------------|---|--|--|--|--|--|

| 2.0. ABOUT THIS DOCUMENT                                               | 5 |  |  |  |  |  |

| 2.1. Document Organization                                             | 5 |  |  |  |  |  |

| 2.2. References                                                        | 5 |  |  |  |  |  |

| 2.3. Definition of Terms                                               | 5 |  |  |  |  |  |

| 3.0. AGTL+ DESIGN GUIDELINE                                            | 7 |  |  |  |  |  |

| 3.1. Determine Components                                              | 7 |  |  |  |  |  |

| 3.2. Initial Timing Analysis                                           | 8 |  |  |  |  |  |

| 3.3. Determine General Topology, Layout, and<br>Routing Desired1       | 1 |  |  |  |  |  |

| 3.4. Pre-Layout Simulation1                                            | 3 |  |  |  |  |  |

| 3.4.1. METHODOLOGY1                                                    | 3 |  |  |  |  |  |

| 3.4.2. SIMULATION CRITERIA1                                            | 4 |  |  |  |  |  |

| 3.5. Place and Route Board14                                           | 4 |  |  |  |  |  |

| 3.5.1. ESTIMATE COMPONENT TO<br>COMPONENT SPACING FOR AGTL+<br>SIGNALS | 4 |  |  |  |  |  |

| 3.5.2. LAYOUT AND ROUTE BOARD                                          |   |  |  |  |  |  |

| 3.6. Post-Layout Simulation1                                           |   |  |  |  |  |  |

| 3.6.1. INTERSYMBOL INTERFERENCE                                        |   |  |  |  |  |  |

| 3.6.2. CROSSTALK ANALYSIS1                                             |   |  |  |  |  |  |

| 3.6.3. MONTE CARLO ANALYSIS                                            | 5 |  |  |  |  |  |

| 3.7. Validation1                                                       |   |  |  |  |  |  |

| 3.7.1. MEASUREMENTS                                                    | 6 |  |  |  |  |  |

| 3.7.2. FLIGHT TIME SIMULATION                                          | 6 |  |  |  |  |  |

| 3.7.3. FLIGHT TIME HARDWARE<br>VALIDATION1                             | 7 |  |  |  |  |  |

|                                                                        | ' |  |  |  |  |  |

| 4.0. THEORY1                                                           | 7 |  |  |  |  |  |

| 4.1. AGTL+1                                                            |   |  |  |  |  |  |

| 4.2. Timing Requirements1                                              | 7 |  |  |  |  |  |

| 4.3. Noise Margin1                                                     | 7 |  |  |  |  |  |

| 4.3.1. FALLING EDGE OR LOW LEVEL<br>NOISE MARGIN                       |   |  |  |  |  |  |

| 4.3.2. RISING EDGE OR HIGH LEVEL NOISE<br>MARGIN1                      |   |  |  |  |  |  |

| 4.4. Crosstalk Theory2                                                 | 0 |  |  |  |  |  |

| 4.4.1. CROSSTALK MANAGEMENT2                                           | 2 |  |  |  |  |  |

| P                                                                      | AGE |

|------------------------------------------------------------------------|-----|

| 4.4.2. POTENTIAL TERMINATION<br>CROSSTALK PROBLEMS                     | 23  |

| 5.0. MORE DETAILS AND INSIGHTS                                         | 23  |

| 5.1. Textbook Timing Equations                                         | 23  |

| 5.2. Effective Impedance and Tolerance/<br>Variation                   | 24  |

| 5.3. Power/Reference Planes, PCB Stackup,<br>High Frequency Decoupling |     |

| 5.3.1. POWER DISTRIBUTION                                              | 24  |

| 5.3.2. REFERENCE PLANES AND PCB<br>STACKUP                             | 24  |

| 5.3.3. HIGH FREQUENCY DECOUPLING                                       | G26 |

| 5.3.4. SLOT 2 CONNECTOR                                                | 26  |

| 5.4. Clock Routing                                                     |     |

| 5.5. Conclusion                                                        | 27  |

| 6.0. VREF GUARDBAND                                                    | 28  |

| 7.0. OVERDRIVE REGION                                                  | 28  |

| 8.0. FLIGHT TIME DEFINITION AND<br>MEASUREMENT                         | 29  |

# FIGURES

| Figure 1. Example 6-load and 5-load Plus 6th<br>Stub Termination Network Topology12 |

|-------------------------------------------------------------------------------------|

| Figure 2. Example 5-load Network Topology<br>Optimized for 100 MHz Bus13            |

| Figure 3. Test Load vs. Actual System Load16                                        |

| Figure 4. Rising Edge Noise Margin19                                                |

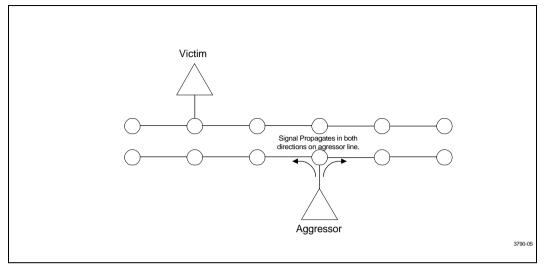

| Figure 5. Propagation on Aggressor Network20                                        |

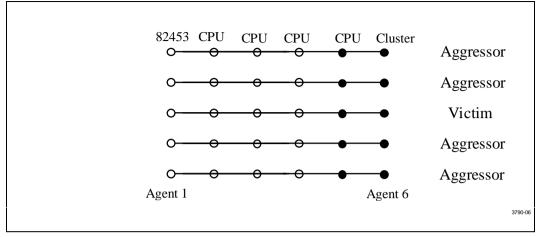

| Figure 6. Aggressor and Victim Networks21                                           |

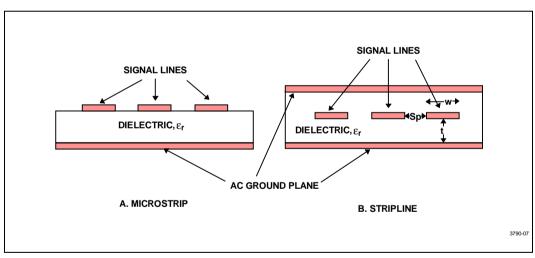

| Figure 7. Transmission Line Geometry: (A)<br>Microstrip (B) Stripline21             |

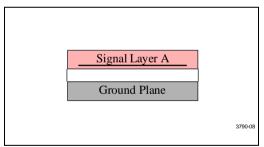

| Figure 8. One Signal Layer and One Reference<br>Plane25                             |

| Figure 9. Layer Switch with One Reference<br>Plane25                                |

| Figure 10. Layer Switch with Multiple Reference<br>Planes (same type)25             |

| Figure 11. Layer Switch with Multiple Reference<br>Planes26                         |

|                                                                                     |

### AP-830

# intel®

| Figure 12. One Layer with Multiple Reference  |      |

|-----------------------------------------------|------|

| Planes                                        | . 26 |

| Figure 13. Overdrive Region and VREF          |      |

| Guardband                                     | . 29 |

| Figure 14. Rising Edge Flight Time Definition | . 29 |

### TABLES

| Table 1. Pentium <sup>®</sup> II Xeon <sup>™</sup> Processor and |   |

|------------------------------------------------------------------|---|

| MIOC AGTL+ Parameters                                            | 9 |

| Table 2. Example TFLT_MAX Calculations for |      |

|--------------------------------------------|------|

| 100 MHz Bus                                | . 10 |

- Table 3. Example TFLT\_MAX Calculations for 90 MHz Bus (Cluster Controller Design).. 11

- Table 4. Example TFLT\_MIN Calculations (Frequency Independent) ...... 11

# 1.0. INTRODUCTION

The Pentium<sup>®</sup> II Xeon<sup>™</sup> processor is a follow-on to the Pentium Pro and Pentium II family of microprocessors and is the first 100 MHz Slot 2 processor. The design of the external Pentium II Xeon processor bus enables the Pentium II Xeon processor to be "multiprocessor ready." To relax timing constraints on a bus that supports up to six loads, the Pentium II Xeon processor implements a synchronous, latched bus protocol that allows a full clock cycle for signal transmission and a full clock cycle for signal interpretation and generation. This protocol simplifies interconnect timing requirements and supports 100 MHz system designs using conventional interconnect technology. The Pentium II Xeon processor bus uses low-voltage-swing AGTL+ I/O buffers, making high frequency signal communication between many loads easier.

The goal of this layout guideline is to provide the system designer with the information needed for the Pentium II Xeon processor and Intel® 450NX PCIset AGTL+ bus portion of PCB layout. This document provides guidelines and methodologies that are to be used with good engineering practices. See the *Pentium*<sup>®</sup> *II Xeon*<sup>TM</sup> *Processor at 400 MHz* and *Intel*® 450NX *PCIset* for component specific electrical details. Intel strongly recommends running analog simulations using the available I/O buffer models together with layout information extracted from your specific design.

# 2.0. ABOUT THIS DOCUMENT

### 2.1. Document Organization

This section defines terms used in the document. Section 3.0. discusses specific system guidelines. This is a step-by-step methodology that Intel has successfully used to design Pentium II Xeon processor systems using the Intel 450NX PCIset components. Section 4.0. introduces the theories that are applicable to this layout guideline. Section 5.0. contains more details and insights. The items in Section 5.0. expand on some of the rationale for the recommendations in the step-by-step methodology. This section also includes equations that may be used for reference.

# The actual guidelines start on Section 3.0., "AGTL+ Design Guideline."

### 2.2. References

- Pentium<sup>®</sup> II Xeon<sup>TM</sup> Processor at 400 MHz

- Intel® 450NX PCIset

- Pentium<sup>®</sup> II Xeon<sup>™</sup> Processor Power Distribution Guidelines

- Slot 2 Processor Bus Terminator Design Guidelines

- Pentium<sup>®</sup> II Processor Developer's Manual (Order Number 243341)

- VRM 8.2/8.3 DC-DC Converter Specification

## 2.3. Definition of Terms

**Aggressor** - a network that transmits a coupled signal to another network is called the aggressor network.

AGTL+ - The Pentium II Xeon processor system bus uses a new bus technology called AGTL+, or Assisted Gunning Transceiver Logic. AGTL+ buffers are opendrain and require pull-up resistors for providing the high logic level and termination. The Pentium II Xeon processor AGTL+ output buffers differ from GTL+ buffers with the addition of an active pMOS pull-up transistor to "assist" the pull-up resistors during the first clock of a low-to-high voltage transition. Additionally, the Pentium II Xeon processor Single Edge Connector (S.E.C.) cartridge contains internal 150  $\Omega$  pull-up resistors to provide termination at each bus load.

**Bus Agent** - a component or group of components that, when combined, represent a single load on the AGTL+ bus.

Corner - describes how a component performs when all parameters that could impact performance are adjusted to have the same impact on performance. Examples of these parameters include variations in manufacturing process, operating temperature, and operating voltage. The results in performance of an electronic component that may change as a result of this include (but are not limited to): clock to output time, output driver edge rate, output drive current, and input drive current. Discussion of the "slow" corner would mean having a component operating at its slowest, weakest drive strength performance. Similar discussion of the "fast" corner would mean having a component operating at its fastest, strongest drive strength performance. Operation or simulation of a component at its slow corner and fast corner is expected to bound the extremes between slowest, weakest performance and fastest, strongest performance.

**Crosstalk** - the reception on a victim network of a signal imposed by aggressor network(s) through inductive and capacitive coupling between the networks.

- **Backward Crosstalk** coupling which creates a signal in a victim network that travels in the opposite direction as the aggressor's signal.

- Forward Crosstalk coupling which creates a signal in a victim network that travels in the same direction as the aggressor's signal.

- Even Mode Crosstalk coupling from multiple aggressors when all the aggressors switch in the same direction that the victim is switching.

- Odd Mode Crosstalk coupling from multiple aggressors when all the aggressors switch in the opposite direction that the victim is switching.

**Edge Finger** - The cartridge electrical contact which interfaces to the Slot 2 connector.

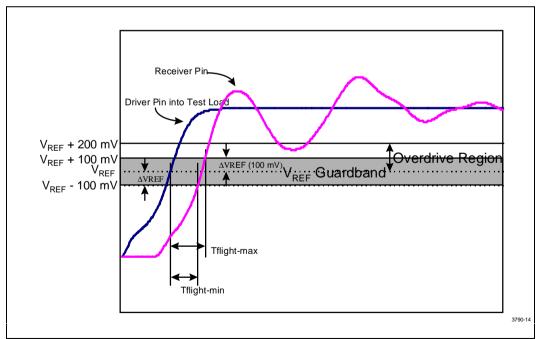

**Flight Time** - is a term in the timing equation that includes the signal propagation delay, any effects the system has on the  $T_{CO}$  of the driver, plus any adjustments to the signal at the receiver needed to guarantee the setup time of the receiver.

More precisely, *flight time* is defined to be:

• The time difference between a signal at the **input** pin of a receiving agent crossing V<sub>REF</sub> (adjusted to meet the receiver manufacturer's conditions required for AC timing specifications; i.e., ringback, etc..), and the output pin of the driving agent crossing V<sub>REF</sub> if **the driver was driving the** *Test Load* used to specify the driver's AC timings.

See Section 3.7.2. for details regarding flight time simulation and validation.

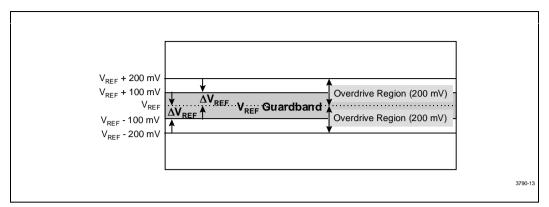

Figure 13 in Appendix A shows the  $V_{REF}$  Guardband boundaries where maximum and minimum flight time measurements are taken. The  $V_{REF}$  Guardband takes into account sources of noise that may affect the way an AGTL+ signal becomes valid at the receiver. See the definition of the  $V_{REF}$  Guardband.

Maximum and Minimum Flight Time - Flight time variations can be caused by many different parameters. The more obvious causes include variation of the board dielectric constant, changes in load condition, crosstalk, V<sub>TT</sub> noise, V<sub>REF</sub> noise, variation in termination resistance and differences in I/O buffer performance as a function of temperature, voltage and manufacturing process. Some less obvious causes include effects of *Simultaneous Switching Output (SSO)* and packaging affects.

- The **Maximum Flight Time** is the largest flight time a network will experience under all variations of conditions. Maximum flight time is measured at the appropriate V<sub>REF</sub> Guardband boundary.

- The Minimum Flight Time is the smallest flight time a network will experience under all variations of conditions. Minimum flight time is measured at the appropriate V<sub>REF</sub> Guardband boundary.

For more information on flight time and the  $V_{REF}$  Guardband, see Appendix A of this guideline and the *Pentium® II Processor Developer's Manual.*

**GTL**+ is the bus technology used by the Pentium Pro processor. This is an incident wave switching, open drain bus with pull-up resistors which provide both the high logic level and termination. It is an enhancement to the GTL (Gunning Transceiver Logic) technology. See the *Pentium® II Processor Developer's Manual* for more details of GTL+.

**Network** - the trace of a Printed Circuit Board (PCB) that completes an electrical connection between two or more components.

**Network Length** - the distance between extreme bus agents on the network and does not include the distance connecting the end bus agents to the termination resistors.

**Overdrive Region** - is the voltage range, at a receiver, located above and below V<sub>REF</sub> for signal integrity analysis. See the *Pentium® II Processor Developer's Manual* for more details.

**Overshoot** - Maximum voltage allowed for a signal at the processor core pad. See the *Pentium*® *II* Xeon<sup>TM</sup> *Processor at 400 MHz* and *Intel*® 450NX PCIset for overshoot specifications.

**Pad** - a feature of a semiconductor die contained within an internal logic package on the cartridge substrate used to connect the die to the package bond wires. A pad is only observable in simulation.

**Pin** - a feature of a logic package contained within the S.E.C. cartridge used to connect the package to an internal substrate trace.

**Ringback** - is the voltage that a signal rings back to after achieving its maximum absolute value. Ringback may be due to reflections, driver oscillations, etc. See the *Pentium® II Xeon<sup>TM</sup> Processor at 400 MHz* and *Intel® 450NX PCIset Electrical Mechanical and Thermal Specification* for ringback specifications.

Settling Limit - defines the maximum amount of ringing at the receiving pin that a signal must reach before its next transition. See the *Pentium*<sup>®</sup> *II Xeon*<sup>TM</sup> *Processor at 400 MHz* and *Intel*<sup>®</sup> *450NX PCIset* for settling limit specifications.

**Setup Window** - is the time between the beginning of Setup to Clock  $(T_{SU_{-MIN}})$  and the arrival of a valid clock edge. This window may be different for each type of bus agent in the system.

Simultaneous Switching Output (SSO) Effects - refers to the difference in electrical timing parameters and degradation in signal quality caused by multiple signal outputs simultaneously switching voltage levels (e.g., high-to-low) in the opposite direction from a single signal (e.g., low-to-high) or in the same direction (e.g., high-to-low). These are respectively called odd-mode switching and even-mode switching. This simultaneous switching of multiple outputs creates higher current swings that may cause additional propagation delay (or "pushout"), or a decrease in propagation delay (or "pull-in"). These SSO effects may impact the setup and/or hold times and are not always taken into account by simulations. System timing budgets should include margin for SSO effects.

**Stub** - the branch from the trunk terminating at the pad of an agent.

Test Load - Intel uses a 25  $\boldsymbol{\Omega}$  test load for specifying its components.

**Trunk** - the main connection, excluding interconnect branches, terminating at agent pads.

**Undershoot** - Maximum voltage allowed for a signal to extend below  $V_{SS}$  at the processor core pad. See the *Pentium® II Xeon<sup>TM</sup> Processor at 400 MHz* and *Intel® 450NX PCIset* for undershoot specifications.

**Victim** - a network that receives a coupled crosstalk signal from another network is called the victim network.

# 3.0. AGTL+ DESIGN GUIDELINE

The following step-by-step guideline was developed for systems based on four Pentium II Xeon processor loads, one MIOC load, and one optional cluster controller.

The guideline recommended in this section is based on experience developed at Intel while developing many different Pentium Pro processor family and Pentium II Xeon processor based systems. Begin with component selection, an initial timing analysis, and topology definition. Perform pre-layout analog simulations for a detailed picture of a working "solution space" for the design. These pre-layout simulations help define routing rules prior to placement and routing. After routing, extract the interconnect database and perform post-layout simulations to refine the timing and signal integrity analysis. Validate the analog simulations when actual systems become available. The validation section describes a method for determining the flight time in the actual system.

Guideline Methodology:

- Determine Components

- Initial Timing Analysis

- · Determine General Topology, Layout, and Routing

- Pre-Layout Simulation (Sensitivity sweep)

- Place and Route Board

- Estimate Component to Component Spacing for AGTL+ Signals

- Layout and Route Board

- Post-Layout Simulation

- Interconnect Extraction

- Intersymbol Interference (ISI), Crosstalk, and Monte Carlo Analysis

- Validation

- Measurements

- Determining Flight Time

### 3.1. Determine Components

Determine whether a cluster controller will be used and whether it will reside directly on the PCB or occupy a fifth Single Edge Contact (SEC) connector slot.

# 3.2. Initial Timing Analysis

Perform an initial timing analysis of the system using Equation 1 and Equation 2 shown below. These equations are the basis for the timing analysis. To complete the initial timing analysis, values for clock skew and clock jitter are needed, along with the component specifications. These equations contain a multi-bit adjustment factor,  $M_{ADJ}$ , to account for multi-bit switching effects such as SSO pushout or pull-in that are often hard to simulate. These equations **do not** take into consideration all signal integrity factors that affect timing. Additional timing margin should be budgeted to allow for these sources of noise.

#### **Equation 1. Setup Time**

$T_{CO\_MAX} + T_{SU\_MIN} + CLK_{SKEW} + CLK_{JITTER} + \\ T_{FLT\_MAX} + M_{ADJ} \le Clock \ Period$

#### **Equation 2. Hold Time**

$T_{CO\_MIN} + T_{FLT\_MIN} - M_{ADJ} \ge T_{HOLD} + CLK_{SKEW}$

Symbols used in Equation 1 and Equation 2:

- T<sub>CO\_MAX</sub> is the maximum clock to output specification<sup>1</sup>.

- T<sub>SU-MIN</sub> is the minimum required time specified to setup before the clock<sup>1</sup>.

- CLK<sub>JITTER</sub> is the maximum clock edge-to-edge variation.

- CLK<sub>SKEW</sub> is the maximum variation between components receiving the same clock edge.

- T<sub>FLT\_MAX</sub> is the maximum flight time as defined in Section 2.3.

- T<sub>FLT\_MIN</sub> is the minimum flight time as defined in Section 2.3.

- M<sub>ADJ</sub> is the multi-bit adjustment factor to account for SSO pushout or pull-in.

- T<sub>CO\_MIN</sub> is the minimum clock to output specification<sup>1</sup>.

- T<sub>HOLD</sub> is the minimum specified input hold time.

#### NOTE

The Clock to Output (T<sub>CO</sub>) and Setup to Clock (T<sub>SU</sub>) timings are both measured from the signals last crossing of V<sub>REF</sub>, with the requirement that the signal does not violate the ringback or edge rate limits. See the *Pentium<sup>®</sup> II Xeon™ Processor at 400 MHz* and the *Pentium<sup>®</sup> II Processor Developer's Manual* for more details.

Solving these equation for  $T_{FLT}$  results in the following equations:

#### **Equation 3. Maximum Flight Time**

$\begin{array}{l} T_{FLT\_MAX} \leq Clock \mbox{ Period - } T_{CO\_MAX} \mbox{ - } T_{SU\_MIN} \mbox{ - } \\ CLK_{SKEW} \mbox{ - } CLK_{JITTER} \mbox{ - } M_{ADJ} \end{array}$

#### Equation 4. Minimum Flight Time

$T_{FLT\_MIN} \ge T_{HOLD} + CLK_{SKEW} - T_{CO\_MIN} + M_{ADJ}$

There are multiple cases to consider. Note that while the same trace connects two components, component A and component B, the minimum and maximum flight time requirements for component A driving component B as well as component B driving component A must be met. The cases to be considered are:

- Pentium<sup>®</sup> II Xeon<sup>TM</sup> processor driving Pentium II Xeon processor

- Pentium II Xeon processor driving MIOC

- MIOC driving a Pentium II Xeon processor

- Pentium II Xeon processor driving cluster controller

- Cluster controller driving Pentium II Xeon processor

- MIOC driving cluster controller

- Cluster controller driving MIOC

A designer using components other than those listed above must evaluate any additional combinations of driver and receiver.

Table 1 lists the AGTL+ component timings of the Pentium II Xeon processor and MIOC defined at the pins. These timings are for reference only; obtain component specifications from the *Pentium*<sup>®</sup> II Xeon<sup>TM</sup> Processor at 400 MHz and Intel<sup>®</sup> 450NX PCIset.

| IC Parameters                                  | Pentium <sup>®</sup> II Xeon™ Processor<br>at 90 MHz or 100 MHz Bus | MIOC  |

|------------------------------------------------|---------------------------------------------------------------------|-------|

| Clock to Output maximum (T <sub>CO_MAX</sub> ) | 2.70                                                                | 2.65  |

| Clock to Output minimum (T <sub>CO_MIN</sub> ) | 0.20                                                                | -0.15 |

| Setup time (T <sub>SU_MIN</sub> )              | 1.75                                                                | 1.58  |

| Hold time (T <sub>HOLD</sub> )                 | 0.62                                                                | 0.63  |

#### Table 1. Pentium<sup>®</sup> II Xeon<sup>™</sup> Processor and MIOC AGTL+ Parameters<sup>1,2</sup>

#### NOTES

1. All times in nanoseconds.

2. Numbers in table are for reference only. These timing parameters are subject to change. Please check the appropriate component datasheets for valid timing parameter values.

Table 2 gives an example AGTL+ initial maximum flight time calculation for a 100 MHz, 4-way Pentium II Xeon processor / Intel 450NX PCIset design that does not include a cluster controller. Note that assumed values for clock skew and clock jitter were used. Clock skew and clock jitter values are dependent on the clock components and distribution method chosen for a particular design and must be budgeted into the initial timing equations as appropriate for each design.

Intel highly recommends adding margin as shown in the " $M_{ADJ}$ " column to offset the degradation caused by SSO pushout and other multi-bit switching effects. The "Recommended  $T_{FLT\_MAX}$ " column contains the recommended maximum flight time after incorporating the  $M_{ADJ}$  value. If edge rate, ringback, and monotonicity requirements are not met, flight time correction must be performed as documented in the *Pentium®* II Processor

*Developer's Manual* with the additional requirements noted in Appendix A. The commonly used "textbook" equations used to calculate the expected signal propagation rate of a board are included in Section 5.1.

Simulation and control of baseboard design parameters can ensure that signal quality and maximum and minimum flight times are met. Baseboard propagation speed is highly dependent on transmission line geometry configuration (stripline vs. microstrip), dielectric constant, and loading. This layout guideline includes high-speed baseboard design practices that may improve the amount of timing and signal quality margin. The magnitude of M<sub>ADJ</sub> is highly dependent on baseboard design implementation (stackup, decoupling, layout, routing, reference planes, etc.) and needs to be characterized and budgeted appropriately for each design.

| Table 2. Example T <sub>FLT_MAX</sub> Calculations for Too MHZ Bus |                                 |                       |                             |                             |                             |                               |                          |                                           |

|--------------------------------------------------------------------|---------------------------------|-----------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|--------------------------|-------------------------------------------|

| Driver                                                             | Receiver                        | Clk<br>Period<br>(ns) | T <sub>CO_MAX</sub><br>(ns) | T <sub>SU_MIN</sub><br>(ns) | Clk <sub>SKEW</sub><br>(ns) | Clk <sub>JITTER</sub><br>(ns) | M <sub>ADJ</sub><br>(ns) | Recommended<br>TFLT_MAX <sup>2</sup> (ns) |

| Pentium <sup>®</sup><br>II Xeon™<br>processor                      | Pentium II<br>Xeon<br>processor | 10.00                 | 2.70                        | 1.75                        | 0.15                        | 0.15                          | 0.80                     | 4.45                                      |

| Pentium II<br>Xeon<br>processor                                    | MIOC                            | 10.00                 | 2.70                        | 1.58                        | 0.15                        | 0.15                          | 0.80                     | 4.63                                      |

| MIOC                                                               | Pentium II<br>Xeon<br>processor | 10.00                 | 2.65                        | 1.75                        | 0.15                        | 0.15                          | 0.50                     | 4.80                                      |

Table 2. Example  $T_{FLT\_MAX}$  Calculations for 100 MHz Bus<sup>1,2</sup>

#### NOTES:

1. All times in nanoseconds.

The flight times in this column include margin to account for the following phenomena which Intel has observed when multiple bits are switching simultaneously. These multi-bit effects can adversely affect flight time and signal quality and are sometimes not accounted for in simulation. Accordingly, maximum flight times depend on the baseboard design and additional adjustment factors or margins are recommended.

- SSO pushout or pull-in

- Rising or falling edge rate degradation at the receiver caused by inductance in the current return path, requiring extrapolation that causes additional delay.

- Crosstalk on the PCB and internal to the package can cause variation in the signals.

There are additional effects that **may not** necessarily be covered by the multi-bit adjustment factor and should be budgeted as appropriate to the baseboard design. Examples include:

- The effective board propagation constant (S<sub>EFF</sub>), which is a function of:

- Dielectric constant (εr) of the PCB material

- The type of trace connecting the components (stripline or microstrip)

- The length of the trace and the load of the components on the trace. (Note that the board propagation constant multiplied by the trace length is a component of the flight time but not necessarily equal to the flight time.)

| Iculations for 90 MHz Bus (Cluster Controller Design) <sup>1,2</sup> |   |  |   |  |             |  |  |  |

|----------------------------------------------------------------------|---|--|---|--|-------------|--|--|--|

|                                                                      | _ |  | • |  | Recommended |  |  |  |

| Driver                            | Receiver                        | Clk<br>Period | T <sub>CO-MAX</sub> | T <sub>SU_MIN</sub> | CIk <sub>SKEW</sub> | Clk <sub>JITTER</sub> | M <sub>ADJ</sub> | Recommended<br>T <sub>FLT_MAX</sub> <sup>2</sup> |

|-----------------------------------|---------------------------------|---------------|---------------------|---------------------|---------------------|-----------------------|------------------|--------------------------------------------------|

| Pentium®<br>II Xeon™<br>processor | Pentium II<br>Xeon<br>processor | 11.11         | 2.70                | 1.75                | 0.15                | 0.15                  | 0.80             | 5.56                                             |

| Pentium II<br>Xeon<br>processor   | MIOC                            | 11.11         | 2.70                | 1.58                | 0.15                | 0.15                  | 0.80             | 5.73                                             |

| MIOC                              | Pentium II<br>Xeon<br>processor | 11.11         | 2.65                | 1.75                | 0.15                | 0.15                  | 0.50             | 5.91                                             |

Table 4. Example T<sub>FLT\_MIN</sub> Calculations (Frequency Independent)<sup>1,2</sup>

| Driver                            | Receiver                        | T <sub>HOLD</sub> | Clk <sub>SKEW</sub> | T <sub>CO-MIN</sub> | M <sub>ADJ</sub> | Recommended |

|-----------------------------------|---------------------------------|-------------------|---------------------|---------------------|------------------|-------------|

| Pentium® II<br>Xeon™<br>processor | Pentium II<br>Xeon<br>processor | 0.62              | 0.15                | 0.20                | 0.63             | 1.20        |

| Pentium II<br>Xeon<br>processor   | MIOC                            | 0.63              | 0.15                | 0.20                | 0.62             | 1.20        |

| MIOC                              | Pentium II<br>Xeon<br>processor | 0.62              | 0.15                | -0.15               | 0.28             | 1.20        |

#### NOTE:

1. All times in nanoseconds.

Table 3 gives a similar example maximum flight time calculation for a 90 MHz AGTL+ 4-way Pentium II Xeon processor / Intel 450NX PCIset design that includes a cluster controller.

Table 3. Example T<sub>FLT\_MAX</sub> Cal

Table 4 is an example calculation for minimum flight time that is frequency independent. Intel highly recommends adding margin as shown in the " $M_{AD}$ " column to offset the degradation caused by SSO pull-in and other multi-bit switching effects. The "Recommended  $T_{FLT\_MIN}$ " column contains the recommended minimum flight time after incorporating the  $M_{ADJ}$  value.

Table 2, Table 3, and Table 4 are derived assuming:

- CLK<sub>SKEW</sub> = 0.15 ns (PCB skew only assumes zero driver skew by tying clock driver outputs)

- CLK<sub>JITTER</sub> = 0.15 ns

### 3.3. Determine General Topology, Layout, and Routing Desired

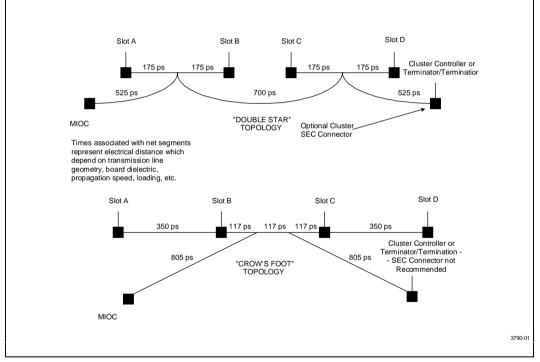

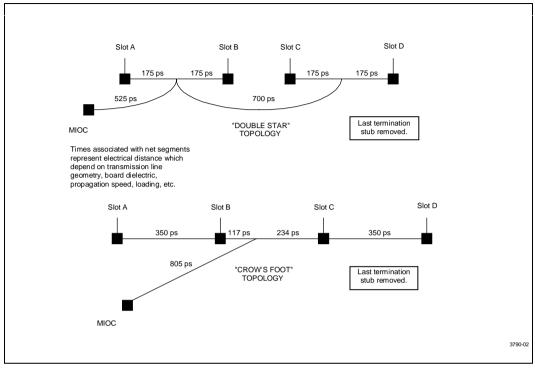

After the selecting the processor bus components and calculating the timing budget, determine the approximate location of the devices on the baseboard. Estimate the printed circuit board parameters from the placement and other information. Locate the processors, Intel 450NX PCIset, and cluster controller as required to meet timing. The "Double Star" and "Crow's Foot" Topologies illustrated in Figure 1 have been shown in simulation to be successful for 6-load, 90 MHz bus operation. 100 MHz bus operation requires that the cluster controller be removed and replaced with AGTL+ termination or a terminator card.

Figure 2 shows a "Double Star" and "Crow's Foot" topology modified to provide more noise and timing margin for 5-load, 100 MHz operation. The modification involves complete removal of the 6<sup>th</sup> stub and AGTL+

termination that should improve worst case flight time margin on falling edge transition. Doing so will reduce the bus load, and should provide more noise and timing margin. Perform simulations on the entire system bus to ensure that ideal termination resistance at the MIOC is chosen for any given design. The termination at the MIOC may be decreased to 75  $\Omega$  to maintain an effective AGTL+ termination of 25  $\Omega$ .

Six-load, cluster-capable systems may gain timing and signal quality margin by using faster dielectric material (e.g., Getek) and better ground plane referencing for AGTL+ signals.

- Place termination resistors at the MIOC and cluster controller, which should be located at opposite ends of the AGTL+ network. Minimize the inductance between the V<sub>TT</sub> distribution and the termination resistors.

- The placement of the Pentium<sup>®</sup> II Xeon<sup>™</sup> processor, MIOC and/or custom ASIC(s) on the Pentium II Xeon processor system bus must be carefully chosen. Using a custom ASIC (with different timings than Pentium II Xeon processor or MIOC) on the system bus will require additional analog simulations to determine the optimum location of each agent along the bus.

Figure 1. Example 6-load and 5-load Plus 6th Stub Termination Network Topology

Figure 2. Example 5-load Network Topology Optimized for 100 MHz Bus

### 3.4. Pre-Layout Simulation

#### 3.4.1. METHODOLOGY

Pentium II Xeon processor designs require analog simulations. Start simulations prior to layout. Pre-layout simulations provide a detailed picture of the working "solution space" that meets flight time and signal quality requirements. The layout recommendations in the previous sections are based on pre-layout simulations conducted at Intel. By basing board layout guidelines on the solution space, the iterations between layout and post-layout simulation can be reduced.

Intel specifies signal quality **at the device pads** and therefore recommends running simulations at the device pads for signal quality. However, the core timings are specified at the **device pins**, so simulation results at the device pins may be used to correlate simulation performance against actual system measurements Pre-layout analysis includes a sensitivity analysis using parametric sweeps. Parametric sweep analysis involves varying one or two system parameters while all others such as driver strength, package, Z0, and S0 are constant. This way, the sensitivity of the proposed bus topology to varying parameters can be analyzed systematically. Sensitivity of the bus to minimum flight time, maximum flight time, and signal quality should be covered. Suggested sweep parameters include trace lengths, termination resistor values, and any other factors that may affect flight time, signal quality, and feasibility of layout. Minimum flight time and worst signal quality are typically analyzed using fast I/O buffers and interconnect. Maximum flight time is typically analyzed using slow I/O buffers and slow interconnect.

Outputs from each sweep should be analyzed to determine which regions meet timing and signal quality specifications. To establish the working solution space, find the common space across all the sweeps that result in passing timing and signal quality. The solution space should allow enough design flexibility for a feasible, cost-effective layout.

#### 3.4.2. SIMULATION CRITERIA

Accurate simulations require that the actual range of parameters be used in the simulations. Intel has consistently measured the cross-sectional resistivity of PCB copper to be in the order of 1 ohm\*mil<sup>2</sup>/inch, not the 0.662 ohm\*mil<sup>2</sup>/inch value for annealed copper that is published in reference material. Using the 1 ohm\*mil<sup>2</sup>/inch value may increase the accuracy of lossy simulations.

Positioning drivers with faster edges closer to the middle of the network typically results in more noise than positioning them towards the ends. We have also shown that the worst-case noise margin can be generated by drivers located in all positions (given appropriate variations in the other network parameters). Therefore, we recommend simulating the networks from all driver locations, and analyzing each receiver for each possible driver.

Analysis has shown that **both fast and slow corner models** must be run for both rising and falling edge transitions. The fast corner is needed because the fast edge rate creates the most noise. The slow corner is needed because the buffer's drive capability will be a minimum, causing the  $V_{OL}$  to shift up, which may cause the noise from the slower edge to exceed the available budget. Slow corner models may produce minimum flight time violations on rising edges if the transition starts from a higher  $V_{OL}$ . So, Intel **highly recommends** checking for minimum and maximum flight time violations with both the fast and slow corner models.

The transmission line package models must be inserted between the output of the buffer and the net it is driving. Likewise, the package model must also be placed between a net and the input of a receiver model. This is generally done by editing your simulator's net description or topology file.

Intel has found wide variation in noise margins when varying the stub impedance and the PCB's  $Z_0$  and  $S_0$ . Intel therefore recommends that PCB parameters be controlled as tightly as possible, with a sampling of the allowable  $Z_0$  and  $S_0$  simulated. The recommended effective line impedance (Z<sub>EFF</sub>) is  $65 \Omega$  +/-10%. Intel recommends running uncoupled simulations using the  $Z_0$  of the package stubs; and performing fully coupled simulations if increased accuracy is needed or desired. Accounting for crosstalk within the device package by varying the stub impedance was investigated and was not found to be sufficiently accurate. This lead to the development of full package models for the component packages.

# 3.5. Place and Route Board

#### 3.5.1. ESTIMATE COMPONENT TO COMPONENT SPACING FOR AGTL+ SIGNALS

Estimate the number of layers that will be required. Then determine the expected interconnect distances between each of the components on the AGTL+ bus. Be sure to consider the guidelines in Section 3.3. Using the estimated interconnect distances, verify that the placement can support the system timing requirements.

The maximum network length between the bus agents is determined by the required bus frequency and the maximum flight time propagation delay on the PCB. The minimum network length is independent of the required bus frequency. Table 2, Table 3, and Table 4 assume values for CLK<sub>SKEW</sub> and CLK<sub>JITTER</sub> parameters that are controlled by the system designer. In order to reduce system clock skew to a minimum, clock buffers which allow their outputs to be tied together are recommended. Intel suggests running analog simulations to ensure that each design has adequate noise and timing margin.

#### 3.5.2. LAYOUT AND ROUTE BOARD

Route the board satisfying the estimated space and timing requirements. Stay within the solution space set from the pre-layout sweeps. Estimate the printed circuit board parameters from the placement and other information including the following general guidelines:

- Distribute V<sub>TT</sub> with a power plane or a partial power plane. If this cannot be accomplished, use as wide a trace as possible and route the V<sub>TT</sub> trace with the same design rules as the AGTL+ traces.

- Keep the overall length of the bus as short as possible (but don't forget minimum component to component distances to meet hold times).

- Plan to minimize crosstalk by:

- Routing the same type of AGTL+ I/O signals in isolated signal groups. I.e., route the data signals in one group, the arbitration signals in another group. Keep at least a 5:1 spacing to trace width ratio between each group

- Keeping at least a 25 mil space between AGTL+ signals and non-AGTL+ signals (and at least a 5:1 spacing to line width ratio).

- Keeping at least a 4:1 spacing to trace width ratio between AGTL+ signals in the same group.

- Using a trace pitch to trace height ratio of 3:1 between AGTL+ signals in the same group.

- Using a trace pitch to trace height ratio of 4:1 between AGTL+ signals in different groups.

- Using a trace pitch to trace height ratio of 5:1 between AGTL+ signals and non-AGTL+ signals

- Minimizing the dielectric process variation used in the PCB fab.

- Eliminating parallel traces between layers not separated by a power or ground plane.

The spacing between the various bus agents causes variations in trunk impedance and stub locations. These variations cause reflections which can cause constructive or destructive interference at the receivers. A reduction of noise may be obtained by a minimum spacing between the agents. Unfortunately, a tighter spacing results in reduced component placement options and lower hold margins. Therefore adjusting the inter-agent spacing may be one way to change the network's noise margin, but mechanical constraints often limit the usefulness of this technique. Always be sure to validate signal quality after making any changes in agent locations or changes to inter-agent spacing.

There are six AGTL+ signals that can be driven by more than one agent simultaneously. These signals may require more attention during the layout and validation portions of the design. When a signal is asserted (driven low) by two or more agents on the same clock edge, the two falling edge wave fronts will meet at some point on the bus and can sum to form a negative voltage. The ringback from this negative voltage can easily cross into the overdrive region. The signals are AERR#, BERR#, BINIT#, BNR#, HIT#, and HITM#.

This document addresses AGTL+ layout. Chassis requirements for cooling, connector location, memory location, etc., may constrain the system topology and component placement location, therefore constraining the board routing. These issues are not directly addressed in this document.

### 3.6. Post-Layout Simulation

Following layout, extract the interconnect information for the board from the CAD layout tools. Run post-layout simulations to verify that the layout meets timing and noise requirements. A small amount of "tuning" may be required; experience at Intel has shown that sensitivity analysis dramatically reduces the amount of tuning required. The post layout simulations should take into account the expected variation for all interconnect parameters.

Intel specifies signal quality **at the device pads** and therefore recommends running simulations at the device pads for signal quality. However, Intel specifies core timings **at the device pins**, so simulation results at the device pins should be used later to correlate simulation performance against actual system measurements.

#### 3.6.1. INTERSYMBOL INTERFERENCE

Intersymbol Interference (ISI) refers to the distortion or change in the waveform shape caused by the voltage and transient energy on the network when the driver begins its next transition.

For example, ISI may occur when the line is driven high, low, and then high in consecutive cycles (the opposite case is also valid). When the driver drives high on the first cycle and low on the second cycle, the signal may not settle to the minimum  $V_{OL}$  before the next rising edge is driven. This results in improved flight times in the third cycle. ISI simulations for the topology given in this section were performed by comparing flight times for the first and third cycle. ISI effects do not necessarily span only 3 cycles so it may be necessary to simulate beyond 3 cycles for certain designs. After simulating and quantifying ISI effects, adjust the timing budget accordingly to take these conditions into consideration.

#### 3.6.2. CROSSTALK ANALYSIS

AGTL+ crosstalk simulations can consider the Pentium II Xeon processor core package, MIOC package, and Slot 2 connectors as non-coupled. Treat the traces on the Pentium II Xeon processor cartridge and baseboard as fully coupled for maximum crosstalk conditions. Simulate the traces as lossless for worst case crosstalk, and lossy where more accuracy is needed. Evaluate both odd and even mode crosstalk conditions.

AGTL+ crosstalk simulation involves the following cases:

- Intra-group AGTL+ crosstalk

- Inter-group AGTL+ crosstalk

- CMOS to AGTL+ crosstalk

#### 3.6.3. MONTE CARLO ANALYSIS

Perform a Monte Carlo analysis to refine the passing solution space region. A Monte Carlo analysis involves

randomly varying parameters (independent of one another) over their tolerance range. This analysis is intended to ensure that no regions of failing flight time and signal quality exist between the extreme corner cases run in pre-layout simulations. For the example topology, vary the following parameters during Monte Carlo simulations:

- Trace lengths on baseboard

- AGTL+ termination resistance R<sub>TT</sub> on Pentium<sup>®</sup> II Xeon<sup>™</sup> processor cartridges

- AGTL+ termination resistance R<sub>TT</sub> at the MIOC

- AGTL+ termination resistance R<sub>TT</sub> at the Cluster Controller (if present)

- AGTL+ termination resistance  $R_{TT}$  on termination cards or 6<sup>th</sup> stub (if present).

- Z<sub>0</sub> of traces on Pentium II Xeon processor cartridges

- S<sub>0</sub> of traces on Pentium II Xeon processor cartridges

- Z<sub>0</sub> of traces on baseboard

- S<sub>0</sub> of traces on baseboard

- Fast and slow corner Pentium II Xeon processor I/O buffer models

- Fast and slow Pentium II Xeon processor package models

- Fast and slow corner Intel® 450NX PCIset I/O buffer models

- Fast and slow Intel 450NX PCIset package models

Refer to the *Pentium*<sup>®</sup> II Xeon<sup>TM</sup> Processor at 400 MHz and electronic I/O buffer models for the parameter ranges of the Pentium II Xeon processor and Intel 450NX PCIset.

# 3.7. Validation

Build systems and validate the design and simulation assumptions.

#### 3.7.1. MEASUREMENTS

Note that the AGTL+ specification for signal quality is at the **pad** of the component. The expected method of determining the signal quality is to run analog simulations for the pin and the pad. Then correlate the simulations at the pin against actual system measurements at the pin. Good correlation at the pin leads to confidence that the simulation at the pad is accurate. Controlling the temperature and voltage to correspond to the I/O buffer model extremes should enhance the correlation between simulations and the actual system.

#### 3.7.2. FLIGHT TIME SIMULATION

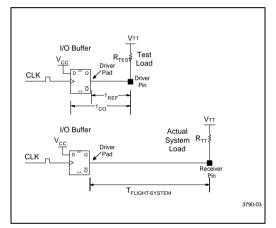

As defined earlier in Section 2.3., flight time is the time difference between a signal crossing  $V_{REF}$  at the input pin of the receiver, and the output pin of the driver crossing  $V_{REF}$  were it driving a *test load*. The timings in the tables and topologies discussed in this guideline assume the actual system load is 25  $\Omega$  and is **equal to the** *test load*. This may not be the case in a particular design and this section describes how to correlate the design load to the test load in simulation and in validation.

Figure 3. Test Load vs. Actual System Load

Figure 3 above shows the different configurations for T<sub>CO</sub> testing and flight time simulation. The flip-flop represents the logic input and driver stage of a typical AGTL+ I/O buffer. T<sub>CO</sub> timings are specified at the driver pin output. TFLIGHT-SYSTEM is usually reported by a simulation tool as the time from the driver pad starting its transition to the time when the receiver's input pin sees a valid data input. Since both timing numbers (T<sub>CO</sub> and TFLIGHT-SYSTEM) will include propagation time from the pad to the pin, it is necessary to subtract this time (TREF) from the reported flight time to avoid double counting. TREF is defined as the time that it takes for the driver output pin to reach the measurement voltage, V<sub>REF</sub>, starting from the beginning of the driver transition at the pad. TREF must be generated using the same test load for T<sub>CO</sub>. Intel provides this timing value in the AGTL+ I/O buffer models.

In this manner, the following *valid delay* equation is satisfied:

#### Valid Delay Equation

Valid Delay =  $T_{CO}$  + TFLIGHT-SYS -  $T_{REF}$  =  $T_{CO}$ -

MEASURED + TFLIGHT-MEASURED

This valid delay equation is the total time from when the driver sees a valid clock pulse to the time when the receiver sees a valid data input.

# 3.7.3. FLIGHT TIME HARDWARE VALIDATION

When a measurement is made on the actual system,  $T_{CO}$  and flight time do not need correction since these are the actual numbers. These measurements include all of the effects pertaining to the driver-system interface and the same is true for the  $T_{CO}$ . Therefore the addition of the measured  $T_{CO}$  and the flight time must be equal to the valid delay calculated above.

## 4.0. THEORY

### 4.1. AGTL+

AGTL+ is the electrical bus technology used for the Pentium II Xeon processor bus. This is an incident wave switching, open-drain bus with external pull-up resistors that provide both the high logic level and termination at each load. The Pentium II Xeon processor AGTL+ drivers contain a full cycle active pull-up device to improve system timings. The AGTL+ specification defines:

- Termination voltage (V<sub>TT</sub>).

- Receiver reference voltage (V<sub>REF</sub>) as a function of termination voltage (V<sub>TT</sub>).

- Pentium<sup>®</sup> II Xeon<sup>™</sup> processor Termination resistance (R<sub>TT</sub>).

- Input low voltage (V<sub>IL</sub>).

- Input high voltage (V<sub>IH</sub>).

- NMOS on resistance (R<sub>ONN</sub>).

- Edge rate specifications.

- Ringback specifications.

- Overshoot/Undershoot specifications.

- Settling Limit.

The complete AGTL+ specification can be found in the *Pentium*<sup>®</sup> *II Xeon*<sup>TM</sup> *Processor at 400 MHz.* Layout recommendations for the AGTL+ bus can be found in Section 3.0. of this document.

## 4.2. Timing Requirements

The system timing for AGTL+ is dependent on many things. Each of the following elements combine to determine the maximum and minimum frequency the AGTL+ bus can support:

- The range of timings for each of the agents in the system.

- Clock to output [ $T_{CO}$ ]. (Note that the system load is likely to be different from the "specification" load therefore the  $T_{CO}$  observed in the system may not be the same as the  $T_{CO}$  from the specification.)

- The minimum required setup time to clock  $[T_{SU-MIN}]$  for each receiving agent.

- The range of flight time between each component. This includes:

- The velocity of propagation for the loaded printed circuit board [S<sub>EFF</sub>].

- The board loading impact on the effective  $T_{CO}$  in the system.

- The amount of skew and jitter in the system clock generation and distribution.

- Changes in flight time due to crosstalk, noise, and other effects.

### 4.3. Noise Margin

The goal of this section is to describe the total amount of noise that can be tolerated in a system (the noise budget), identify the sources of noise in the system, and recommend methods to analyze and control the noise so that the allowed noise budget is not exceeded.

There are several sources of noise which must be accounted for in the system noise budget, including:

- V<sub>REF</sub> variation

- V<sub>CCCORE</sub> variation

- Variation in V<sub>TT</sub>

- Crosstalk

- Ringback due to impedance variation along the network, termination mismatch, and/or stubs on the network

- Simultaneous Switching Output Effects

The total noise budget is calculated by taking the difference in the worst case specified input level and the worst case driven output level.

Sections 4.3.1. and 4.3.2. discuss calculating noise margin. These sections do not discuss ringback tolerant receivers which can increase the effective noise margin. See the appropriate component datasheets for information about ringback tolerance.

# 4.3.1. FALLING EDGE OR LOW LEVEL NOISE MARGIN

Equation 5 below shows a method for calculating falling edge noise margin when the Pentium II Xeon processor is driving. An example calculation follows.

#### **Equation 5. Low Level Noise Margin**

Noise  $Margin_{LOW LEVEL} = V_{ILMAX} - V_{OLMAX}$

$\Rightarrow$  V<sub>REF\_MIN</sub> - 100 mV - V<sub>OLMAX</sub>

$\Rightarrow$  [ [ 2/3 ( V<sub>TT\_MIN</sub>) ] - 1% ] - 100 mV - V<sub>OLMAX</sub>

Symbols for Equation 5 are:

- V<sub>ILMAX</sub> is the maximum specified valid input low level from the component specification. For this example, 100 mV below the reference voltage is assumed.

- V<sub>OLMAX</sub> is the maximum output low level the component will drive. This V<sub>OLMAX</sub> maximum

condition corresponds to the slow corner components and models.

- V<sub>REF\_MIN</sub> is the minimum valid voltage reference used for the threshold reference.

- V<sub>TT\_MIN</sub> is the minimum termination voltage.

For the following example calculations for low level and high level noise margin, an  $R_{ON\_MAX}$  equal to 12.5  $\Omega$  is assumed, along with  $V_{REF}$  and  $V_{TT}$  tolerance assumptions. These specs should be obtained from the *Pentium*<sup>®</sup> *II Xeon*<sup>TM</sup> *Processor at 400 MHz.*

Solving for V<sub>REF\_MIN</sub> with 1% V<sub>REF</sub> uncertainty:

$$V_{\text{REF}\_\text{MIN}} = [2/3 (V_{\text{TT}\_\text{MIN}})] - 1\%$$

$$= [2/3 (1.5 V - 9\%)] - 1\%$$

$$= [2/3 (1.37 V)] - 1\%$$

$$= 901 \text{ mV}$$

The output low current in the case of  $V_{TT\_MIN}$ , can be calculated as shown below:

$I = V/R = 1.37/(25 \ \Omega + 12.5 \ \Omega) = 36.5 \ mA$

Then the V<sub>OLMAX</sub> for V<sub>REF\_MIN</sub> is (36.5 mA \* 12.5  $\Omega) = 456 \text{ mV}$

Then, Noise Margin<sub>LOW LEVEL</sub> =  $(V_{REF_MIN}$ -100 mV) -  $V_{OLMAX}$ = (901 mV - 100 mV) - 456 mV = 345 mV

These example calculations are for an effective termination resistance of 25  $\Omega$ . These calculations **do not** include any resistive drop along the trace.

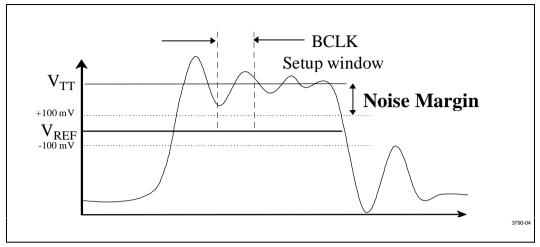

Figure 4. Rising Edge Noise Margin

#### 4.3.2. RISING EDGE OR HIGH LEVEL NOISE MARGIN

Equation 6 below shows a method for calculating rising edge noise margin when the Pentium II Xeon processor is driving. An example calculation follows.

#### Equation 6. High Level Noise Margin

Noise Margin<sub>HIGH LEVEL</sub> =  $V_{OH-MIN} - V_{IH-MIN} \Rightarrow$

$V_{TT\_MIN}$  - ( $V_{REF\_MAX}$  + 100 mV)

Symbols for Equation 6 are:

V<sub>IH\_MIN</sub> is the minimum specified valid input high level from the component specification. For this example, 100 mV above the reference voltage is assumed.

- V<sub>OH\_MIN</sub> is the minimum output high level the component will drive.

- V<sub>TT\_MIN</sub> is the minimum termination voltage. This is assumed to be 1.5 V 9%, or 1.37 V.

- $V_{REF\_MAX}$  is the maximum valid voltage reference used for the threshold reference. Since  $V_{REF}$  is defined as a function of  $V_{TT}$ , the maximum  $V_{REF}$  with  $V_{TT\_MIN}$  is 2/3 \* (1.37 V) + 1% = 922 mV.

- V<sub>OH\_MIN</sub> for AGTL+ signals is V<sub>TT\_MIN</sub>.

- Then Noise Margin<sub>HIGH LEVEL</sub>

- $= V_{TT\_MIN} (V_{REF\_MAX} + 100 \text{ mV})$

- = 1.37 V 922 mV 100 mV

- = 348 mV

Figure 5. Propagation on Aggressor Network

## 4.4. Crosstalk Theory

AGTL+ signals swing across a smaller voltage range and have a correspondingly smaller noise margins than technologies that have traditionally been used in personal computer designs. This requires that designers using AGTL+ be more aware of crosstalk than they may have been in past designs.

Crosstalk is caused through capacitive and inductive coupling between networks. Crosstalk appears as both backward crosstalk and as forward crosstalk. Backward crosstalk creates an induced signal on a victim network that travels in a direction opposite that of the aggressor's signal. Forward crosstalk creates a signal that travels in the same direction as the aggressor's signal. On the AGTL+ bus, a driver on the aggressor network is not necessarily at the end of the network, therefore it sends signals in both directions on the aggressor's network. The signal propagating in each direction causes crosstalk on the victim network. Figure 5 shows a driver on the aggressor network and a receiver on the victim network which illustrates this effect. Figure 6 shows two aggressors on each side of the victim. Additional aggressors are possible in the z-direction, if adjacent signal layers are not routed in mutually perpendicular directions. Because crosstalk coupling coefficients decrease rapidly with increasing separation, it is rarely necessary to consider aggressors which are at least five line widths separated from the victim. The maximum crosstalk occurs when all the aggressors are switching in the same direction at the same time. There is crosstalk internal to the IC packages, which can also affect the signal quality.

Figure 6. Aggressor and Victim Networks

Figure 7. Transmission Line Geometry: (A) Microstrip (B) Stripline

Backward crosstalk is present in both stripline and microstrip geometry (see Figure 7). A way to remember which geometry is stripline and which is microstrip is that a stripline geometry requires **stripping** a layer away to see the signal lines. The backward coupled amplitude is proportional to the backward crosstalk coefficient, the aggressor's signal amplitude, and the coupled length of the network up to a maximum which is dependent on the rise/fall time of the aggressor's signal. Backward crosstalk reaches a maximum (and remains constant) when the propagation time on the coupled network length exceeds one half of the rise time of the aggressor's signal. Assuming the ideal ramp on the aggressor from 0% to 100% voltage swing, and the rise time on an unloaded coupled network, then:

Length for Max Backward Crosstalk =

$$\frac{\frac{1}{2} \times \text{Rise Time}}{\text{Board Delay Per Unit Length}}$$

An example calculation if fast corner fall time is 1.5 V/ns and board delay is 175 ps/inch (2.1 ns/foot) follows:

| Space:Width:Thickness | Coupling Factor | Maximum Crosstalk |

|-----------------------|-----------------|-------------------|

| 24:4:8                | 0.65%           | 9.8 mV            |

| 20:4:8                | 1.3%            | 19. 5 mV          |

| 16:4:8                | 1.75%           | 26.2 mV           |

| 14:4:8                | 2.5%            | 37.5 mV           |

| 12:4:8                | 3.4%            | 51.0 mV           |

| 8:4:8                 | 6.55%           | 98.2 mV           |

| 4:4:8                 | 13.5%           | 202.5 mV          |

Table 5. Example Backward Crosstalk Coupling Factors with  $\epsilon_{r}$  = 4.5, V<sub>OH MAX</sub> = 1.5 V, and Z<sub>0</sub> = 65  $\Omega$

Fall time = 1.5 V/1.5 V/ns = 1 ns

Length of maximum backward crosstalk =

<sup>1</sup>/<sub>2</sub> \* 1 ns \* 1000 ps/ns /175 ps/in = 2.86 inches

Agents on the AGTL+ bus drive signals in each direction on the network. This will cause backward crosstalk from segments on two sides of a driver. The pulses from the backward crosstalk travel toward each other and will meet and **add** at certain moments and positions on the bus. This can cause the voltage (noise) from crosstalk to double.

Table 5 provides example coupling factors for various stripline space to width to dielectric thickness ratios (see Figure 6) with dielectric constant  $\mathcal{E}_{T} = 4.5$ ,  $V_{OH\_MAX} = 1.5$  V, and  $Z_0 = 65 \Omega$ . Note that the fast edge rates of falling edges place limits on the maximum coupled length allowable, and Table 5 illustrates the potential consequences of maximum coupled lengths. Also, it should be noted that multiple parallel coupled lines will increase the impact on the noise budget.

Forward crosstalk is absent in stripline topologies, but present in microstrip. (This is for the ideal case with a uniform dielectric constant. In actual boards, forward crosstalk is nearly absent in stripline topologies, but abundant in microstrip.) The forward coupled amplitude is proportional to the forward crosstalk coefficient, the aggressor's signal edge rate (dv/dt), and the coupled network's electrical length. The forward crosstalk coefficient is also a function of the geometry. Unlike backward crosstalk, forward crosstalk can grow with coupled section length, and may transition in a direction similar to or opposite to that of the aggressor's edge. Unlike backward crosstalk, forward crosstalk on the victim signal will continue to grow as it passes through more coupled length before the aggressor's wave front is absorbed by the termination.

#### 4.4.1. CROSSTALK MANAGEMENT

To minimize crosstalk (and the "cost" of crosstalk) in terms of noise margin budget:

- Route adjacent trace layers in different directions (orthogonal preferred) to minimize the forward and backward crosstalk that can occur from parallel traces on adjacent layers. This reduces the source of crosstalk.

- Maximize the spacing between traces. Where traces have to be close and parallel to each other, minimize the distance that they are close together, and maximize the distance between sections that have close spacing. Routing close together could occur where multiple signals have to route between a pair of pins. When this happens the signals should be spread apart where possible. Also note that routing multiple layers in the same direction between reference planes can result in parallel traces that are close enough to each other to have significant crosstalk.

- Minimize the variation in board impedance (Z<sub>0</sub>). For the example topologies covered in this guideline, 65 Ω +/- 10% was assumed.

- Minimize the nominal board impedance within the AGTL+ specification while maintaining the same trace width/spacing ratio. For a given dielectric constant, this reduces the trace width/trace height ratio, which reduces the backward and forward crosstalk coefficients. Having reduced crosstalk coefficients reduces the magnitude of the crosstalk.

- Minimize the dielectric constant used in the PCB fabrication. As above, all else being equal, this puts the traces closer to their reference planes and reduces the magnitude of the crosstalk.

- Watch out for voltage doubling at a receiving agent, caused by the adding of the backward crosstalk on either side of a driver. Minimize the total network length of signals that have coupled sections. If there has to be closely spaced/coupled lines, place them near the center of the net. This will cause the point in time that voltage doubling occurs to be before the setup window.

- Route synchronous signals that could be driven by different components in separate groups to minimize crosstalk between these groups. The Pentium<sup>®</sup> II Xeon<sup>™</sup> processor uses a split transaction bus with six independent sub buses (arbitration, request, error, snoop, response, and data). This implies that in a given clock cycle, each sub bus could be driven by a different agent. If these two agents are at the opposite process corner (one fast and one slow), then separating the bus types will reduce the impact of crosstalk.

Simulation shows that space to line to dielectric ratios of less than 3:1:2 can produce excessive crosstalk between networks on the Pentium II Xeon processor bus. This is due to the lower voltage swing of AGTL+, high frequencies (even with the controlled edge rate buffers) and likely long parallel traces. Also, while rising edge rates are controlled, falling edge rates are not as well controlled.

#### 4.4.2. POTENTIAL TERMINATION CROSSTALK PROBLEMS

The use of conventional "pull-up" resistor networks for Intel 450NX PCIset and cluster controller termination may not be suitable. These networks have a common power or ground pin at the extreme end of the package, shared by 13 to 19 resistors (for 14- and 20-pin components). These packages generally have too much inductance to maintain the voltage/current needed at each resistive load. Intel recommends using discrete resistors, resistor networks that have separate power/ground pins for each resistor, or working with a resistor network vendor to obtain resistor networks that have acceptable characteristics.

### 5.0. MORE DETAILS AND INSIGHTS

### 5.1. Textbook Timing Equations

The textbook equations used to calculate the propagation rate of a PCB are the basis for spreadsheet calculations for timing margin based on the component parameters. These equations are:

#### **Equation 7. Intrinsic Impedance**

$$Z_0 = \sqrt{\frac{L_0}{C_0}} \quad (\Omega)$$

**Equation 8. Stripline Intrinsic Propagation Speed**

$$S_{0\_STRIPLINE} = 1.017 * \sqrt{\varepsilon_r} \text{ (ns/ft)}$$

Equation 9. Microstrip Intrinsic Propagation Speed

$$S_{0\_MICROSTRIP} = 1.017 * \sqrt{0.475 * \varepsilon_r + 0.67}$$

(ns/ft)

#### Equation 10. Effective Propagation Speed

$$S_{EFF} = S_0 * \sqrt{1 + \frac{C_D}{C_0}}$$

(ns/ft)

#### Equation 11. Effective Impedance

$$Z_{EFF} = \frac{Z_0}{\sqrt{1 + \frac{C_D}{C_0}}} (\Omega)$$

**Equation 12. Distributed Trace Capacitance**

$$C_0 = \frac{S_0}{Z_0} \text{ (pF/ft)}$$

#### Equation 13. Distributed Trace Inductance

$$L_0 = 12 * Z_0 * S_0 \text{ (nH/ft)}$$

Symbols for Equation 7 through Equation 13 are:

- $S_0$  is the speed of the signal on an unloaded PCB in ns/ft. This is referred to as the board propagation constant.

- S0\_MICROSTRIP and S0\_STRIPLINE refer to the speed of the signal on an unloaded microstrip or stripline trace on the PCB in ns/ft.

- Z<sub>0</sub> is the intrinsic impedance of the line in Ω and is a function of the dielectric constant (ε<sub>r</sub>), the line width, line height and line space from the plane(s). The equations for Z<sub>0</sub> are not included in this document. See the *MECL System Design Handbook* by William R. Blood, Jr. for these equations.

- C<sub>0</sub> is the distributed trace capacitance per unit length of the network in pF/ft.

- L<sub>0</sub> is the distributed trace inductance per unit length of the network in nH/ft.

- C<sub>D</sub> is the sum of the capacitance of all devices and stubs divided by the length of the network's trunk, not including the portion connecting the end agents to the termination resistors in pF/ft.

- S<sub>EFF</sub> and Z<sub>EFF</sub> are the effective propagation constant and impedance of the PCB when the board is "loaded" with the components.

### 5.2. Effective Impedance and Tolerance/Variation

The impedance of the PCB needs to be controlled when the PCB is fabricated. The method of specifying control of the impedance needs to be determined to best suit each situation. Using stripline transmission lines (where the trace is between two reference planes) is likely to give better results than microstrip (where the trace is on an external layer using an adjacent plane for reference with solder mask and air on the other side of the trace). This is in part due to the difficulty of precise control of the dielectric constant of the solder mask, and the difficulty in limiting the plated thickness of microstrip conductors, which can substantially increase crosstalk.

• The effective line impedance (Z<sub>EFF</sub>) is recommended to be 65  $\Omega$  +/-10%, where Z<sub>EFF</sub> is defined by Equation 11.

### 5.3. Power/Reference Planes, PCB Stackup, and High Frequency Decoupling

#### 5.3.1. POWER DISTRIBUTION

Designs using the Pentium II Xeon processor require several different voltages. The following paragraphs describe some of the impact of three common methods used to distribute the required voltages. Refer to the *Pentium*<sup>®</sup> II Xeon<sup>TM</sup> Processor Power Distribution Guidelines for more information on power distribution.

The most conservative method of distributing these voltages is for each of them to have a dedicated plane. If any of these planes are used as an "AC ground" reference, then the plane needs to be AC coupled to the system ground plane. This method may require more total layers in the PCB than other methods. 1 ounce/ft<sup>2</sup> thick copper is recommended for all power and reference planes.

A second method of power distribution is to use partial planes in the immediate area needing the power, and to place these planes on a routing layer on an as-needed basis. These planes still need to be decoupled to ground to ensure stable voltages for the components being supplied. This method has the disadvantage of reducing area that can be used to route traces. These partial planes may also change the impedance of adjacent trace layers. (For instance, the impedance calculations may have been done for a microstrip geometry, and adding a partial plane on the other side of the trace layer may turn the microstrip into a stripline.)

#### 5.3.2. REFERENCE PLANES AND PCB STACKUP

The type and number of layers for the PCB need to be chosen to balance many requirements. Many of these requirements include:

The maximum trace resistance for AGTL+ signal paths should not exceed 2 ohms. Depending on the trace width chosen and PCB vendor's process tolerance, this may require 1 ounce/ft<sup>2</sup> thick copper instead of 1/2 ounce/ft<sup>2</sup> thickness. A higher trace resistance increases the voltage drop along the trace, which reduces the falling edge noise margin.

Providing enough routing channels to support the minimum and maximum timing requirements of the components.

- Providing stable voltage distribution for each of the components.

- Providing uniform impedance for the Pentium<sup>®</sup> II Xeon<sup>™</sup> processor bus and other signals as needed.

- Provide a ground plane under the principal component side of the baseboard. Preferably under both sides if active components are mounted on both sides.

- Minimizing coupling/crosstalk between the networks.

- Minimizing RF emissions.

- Maximizing PCB yield.

- Minimizing PCB cost.

- Minimizing cost to assemble PCB.

The following baseboard stackup recommendations should help reduce the amount of Simultaneous Switching Output (SSO) effects experienced.

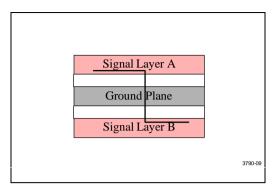

It is recommended that baseboard stackup be arranged such that AGTL+ signal routes do not traverse multiple signal layers, as this can create discontinuities in the signal's return path. It is also recommended that each AGTL+ signal have a single reference plane for the entire route. Figure 8 shows the ideal case where a particular signal is routed entirely within the same signal layer, with a ground layer as the single reference plane.

Figure 8. One Signal Layer and One Reference Plane

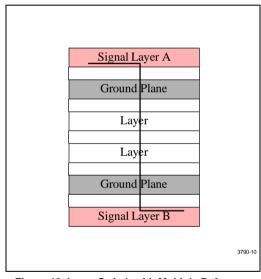

When it is not possible to route the entire AGTL+ signal on a single layer, there are methods to reduce the effects of layer switches whereby the signal still references the same plane (see Figure 9). Figure 10 shows another method of minimizing layer switch discontinuities, but may be less effective than Figure 9. In this case, the signal still references the same type of reference plane (ground). In such a case, it is good practice to stitch (i.e., connect) the two ground planes together with vias in the vicinity of the signal transition via.

Figure 9. Layer Switch with One Reference Plane

Figure 10. Layer Switch with Multiple Reference Planes (same type)

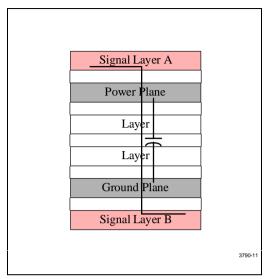

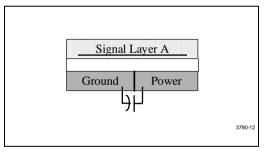

When routing and stackup constraints require that an AGTL+ signal reference multiple planes, one method of minimizing adverse effects is to add high-frequency decoupling wherever the transitions occur, as shown in Figure 11 and Figure 12. Such decoupling should, again, be in the vicinity of the signal transition via and use capacitors with minimal effective series resistance (ESR) and effective series inductance (ESL). Dual vias for these caps are recommended since via inductance may sometimes be higher than the actual capacitor inductance.

Figure 11. Layer Switch with Multiple Reference Planes

Figure 12. One Layer with Multiple Reference Planes

#### 5.3.3. HIGH FREQUENCY DECOUPLING

This section contains several high frequency decoupling recommendations that will improve the return path for an AGTL+ signal. These design recommendations will very likely reduce the amount of SSO effects.

Just as layer switching and multiple reference planes can create discontinuities in an AGTL+ signal return path, discontinuities may also occur when a signal transitions between the baseboard and cartridge. Therefore, providing adequate high-frequency decoupling across VCC<sub>CORE</sub> and ground at the Slot 2 connector interface on the baseboard will minimize the discontinuity in the signal's reference plane at this junction. Please note that these additional high-frequency decoupling capacitors are in addition to the high-frequency decoupling already on the processor.

Transmission line geometry also influences the return path of the reference plane. The following are decoupling recommendations that take this into consideration:

- A signal that transitions from a stripline to another stripline should have close proximity decoupling between all four reference planes.

- A signal that transitions from a stripline to a microstrip (or vice versa) should have close proximity decoupling between the three reference planes.

- A signal that transitions from a stripline or microstrip through vias or pins to a component (chipset, etc.) should have close proximity decoupling across all involved reference planes to ground for the device.

#### 5.3.4. SLOT 2 CONNECTOR

Internal studies indicate that the use of thermal reliefs on the connector pin layout pattern (especially ground pins) should be minimized. Such reliefs (cartwheels or wagonwheels) increase the net ground inductance and reduce the integrity of the ground plane to which many signals are referenced. Increased ground inductance has been shown to aggravate SSO effects. Also, the anti-pad diameter (clearance holes in the planes) for the signal pins should be minimized since large anti-pads also reduce the integrity of the ground plane and increase inductance.

Some additional layout and EMI-reduction guidelines regarding the Slot 2 connector follow:

- Extend power/ground planes up to the Slot 2 connector pins.