# TVP3010C, TVP3010M Data Manual

Video Interface Palette

SLAS082A October 1997

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

# Contents

| Sec | ction                                    |                                              | Title                                                                                                                                                                                  | Page                                                 |

|-----|------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1   | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Features<br>Function<br>Terminal<br>Ordering | (TVP3010C and TVP3010M)<br>al Block Diagram<br>Assignments<br>Information<br>Functions (TVP3010C and TVP3010M)                                                                         | 1–3<br>1–4<br>1–5<br>1–7                             |

| 2   | <b>Deta</b><br>2.1<br>2.2                | MPU Inte                                     | cription<br>erface                                                                                                                                                                     | 2–1<br>2–4<br>2–4<br>2–4<br>2–4                      |

|     | 2.3                                      |                                              | election and Output-Clock (SCLK, RCLK, and VCLK) Generation<br>RCLK, SCLK, VCLK<br>Frame-Buffer Clocking: Self-Clocked or Externally Clocked                                           | 2–5<br>2–5                                           |

|     | 2.4                                      | -                                            | Little-Endian and Big-Endian Data Format         VGA Pass-Through Mode         Pseudo-Color Mode         Direct-Color Mode         True-Color Mode         Multiplex Control Registers | 2–12<br>2–12<br>2–13<br>2–13<br>2–13<br>2–13         |

|     | 2.5                                      | 2.5.1<br>2.5.2<br>2.5.3<br>2.5.4<br>2.5.5    | Cursor AAM<br>Cursor RAM<br>Two-Color 64 × 64 Cursor<br>64 × 64 Cursor Positioning<br>Crosshair Cursor<br>Dual-Cursor Positioning                                                      | 2–23<br>2–23<br>2–24<br>2–24<br>2–24<br>2–25<br>2–26 |

|     | 2.6                                      | Auxiliary<br>2.6.1<br>2.6.2                  | Window, Port Select, and Color-Key Switching         Windowing Control         Color-Key-Switching Control                                                                             | . 2–28                                               |

|     | 2.7                                      |                                              | n                                                                                                                                                                                      |                                                      |

|     | 2.8                                      |                                              | al Zooming                                                                                                                                                                             |                                                      |

|     | 2.9                                      |                                              | ctions                                                                                                                                                                                 |                                                      |

|     |                                          | 2.9.1                                        | 16-Bit CRC                                                                                                                                                                             |                                                      |

|     |                                          | 2.9.2                                        | Sense-Comparator Output and Test Register                                                                                                                                              |                                                      |

|     |                                          | 2.9.3                                        | Identification Code (ID) Register                                                                                                                                                      |                                                      |

|     | 2.10                                     | MUXOU                                        | T [SENSE]Output                                                                                                                                                                        | . 2–34                                               |

|   | 2.11 | Reset .    |                                                              | 2–34  |

|---|------|------------|--------------------------------------------------------------|-------|

|   |      | 2.11.1     | Power-On Reset                                               | 2–34  |

|   |      | 2.11.2     | Software Reset                                               | 2–34  |

|   | 2.12 | Frame-B    | Suffer Interface                                             | 2–35  |

|   | 2.13 | Analog-C   | Dutput Specifications                                        | 2–35  |

|   | 2.14 | Video Co   | ontrol: Horizontal Sync, Vertical Sync, and Blank            | 2–37  |

|   | 2.15 | Split Shif | ft Register Transfer VRAMs                                   | 2–37  |

|   | 2.16 | Control F  | Register Definitions                                         | 2–38  |

|   |      | 2.16.1     | Configuration Register                                       | 2–38  |

|   |      | 2.16.2     | General Control Register                                     | 2–39  |

|   |      | 2.16.3     | Cursor Control Register                                      | 2–40  |

|   |      | 2.16.4     | Cursor Position X and Y Registers                            | 2–41  |

|   |      | 2.16.5     | Sprite Origin X and Y Registers                              | 2–42  |

|   |      | 2.16.6     | Window Start X and Y Registers                               |       |

|   |      | 2.16.7     | Window Stop X and Y Registers                                | 2–44  |

|   |      | 2.16.8     | Cursor Color 0, 1 RGB Registers                              | 2–45  |

|   |      | 2.16.9     | Cursor-RAM Address Register                                  | 2–46  |

|   |      | 2.16.10    | Cursor RAM Data Register                                     | 2–46  |

|   |      | 2.16.11    | AuxiliaryControl Register                                    | 2–47  |

|   |      | 2.16.12    | Color-Key-Control Register                                   | 2–48  |

|   |      |            | Color-Key (Red, Green, Blue, Overlay) Low and High Registers |       |

|   |      |            | Overscan Color RGB Registers                                 |       |

|   |      |            | CRC LSB and MSB Registers                                    |       |

|   |      | 2.16.16    | CRC Control Register                                         | 2–51  |

| 3 | Elec | trical Cha | aracteristics                                                | . 3–1 |

|   | 3.1  | Absolute   | Maximum Ratings Over Operating Free-Air Temperature Range    | . 3–1 |

|   | 3.2  |            | nended Operating Conditions                                  |       |

|   | 3.3  | Electrica  | I Characteristics for TVP3010C Over Recommended Ranges of    |       |

|   |      | Supply V   | /oltage and Operating Free-Air Temperature                   | . 3–2 |

|   | 3.4  | Electrica  | I Characteristics for TVP3010M Over Recommended Ranges of    |       |

|   |      |            | /oltage and Operating Free-Air Temperature                   | . 3–3 |

|   | 3.5  |            | g Characteristics (TVP3010C)                                 |       |

|   | 3.6  |            | g Characteristics (TVP3010M)                                 |       |

|   | 3.7  | Timing R   | Requirements (TVP3010C)                                      | . 3–6 |

|   | 3.8  | Timing R   | Requirements (TVP3010M)                                      | . 3–7 |

|   | 3.9  | Switching  | g Characteristics for TVP3010C Over Recommended Ranges of    |       |

|   |      | Supply V   | Oltage and Operating Free-Air Temperature                    | . 3–8 |

|   | 3.10 |            | g Characteristics for TVP3010M Over Recommended Ranges of    |       |

|   |      | Supply V   | Oltage and Operating Free-Air Temperature                    | 3–10  |

|   | 3.11 | Timing D   | Diagrams                                                     | 3–11  |

| Section    | Title                                       | Page        |

|------------|---------------------------------------------|-------------|

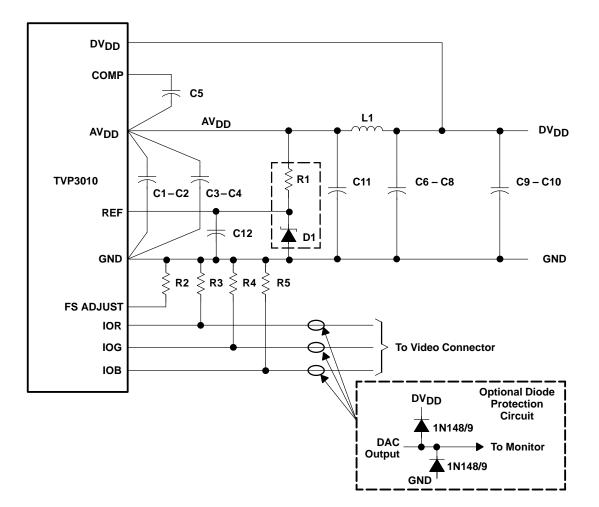

| Appendix A | Printed Circuit Board Layout Considerations | <b>A</b> –1 |

| Appendix B | RCLK Frequency < VCLK Frequency             | B–1         |

| Appendix C | Little-Endian and Big-Endian Data Formats   | C–1         |

| Appendix D | Examples: Register Settings                 | D–1         |

| Appendix E | Mechanical Data                             | E–1         |

# List of Illustrations

| Figure | Title                                                                                | Page  |

|--------|--------------------------------------------------------------------------------------|-------|

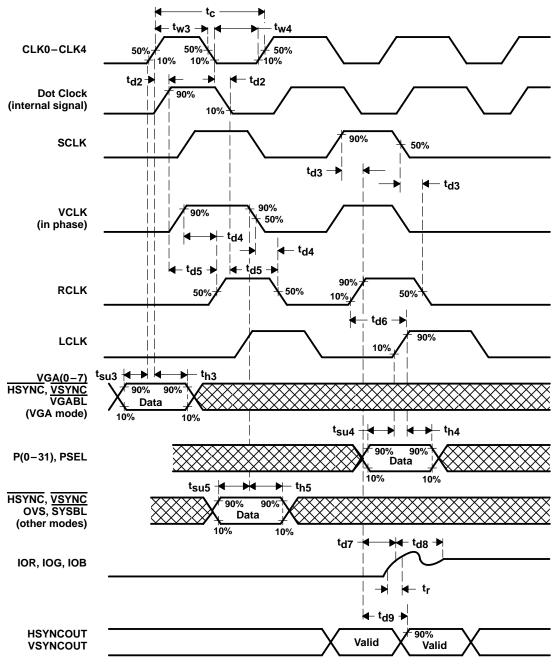

| 2–1    | Dot Clock/VCLK/RCLK/SCLK Relationship                                                | 2–7   |

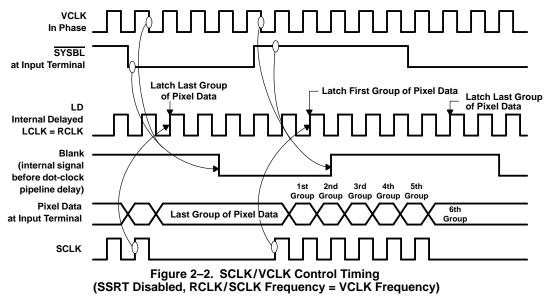

| 2–2    | SCLK/VCLK Control Timing<br>(SSRT Disabled, RCLK/SCLK Frequency = VCLK Frequency)    | 2–8   |

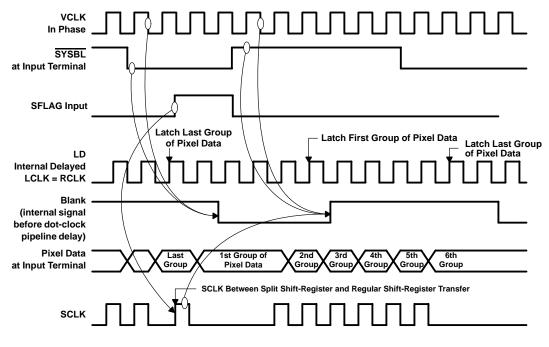

| 2–3    | SCLK/VCLK Control Timing<br>(SSRT Enabled, RCLK/SCLK Frequency = VCLK Frequency)     | 2.0   |

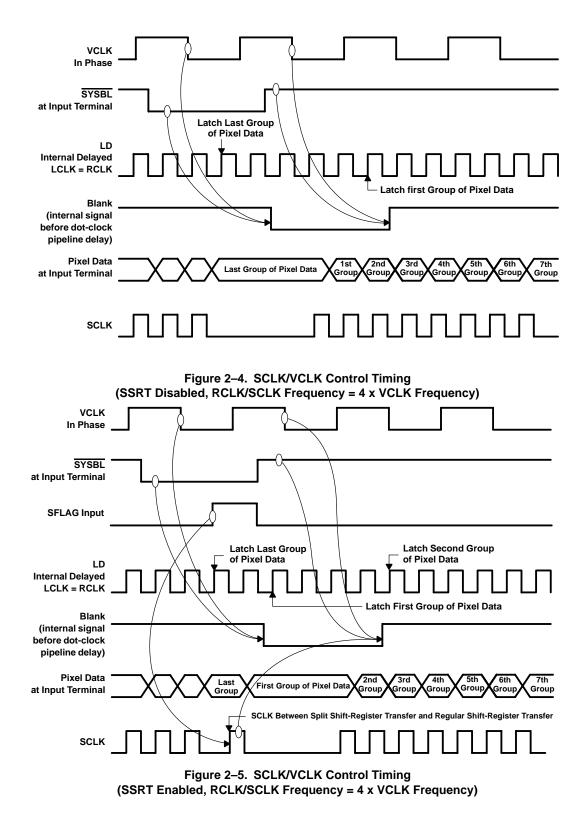

| 2–4    | SCLK/VCLK Control Timing                                                             | . 2—9 |

| o -    | (SSRT Disabled, RCLK/SCLK Frequency = 4 x VCLK Frequency)                            | 2–10  |

| 2–5    | SCLK/VCLK Control Timing<br>(SSRT Enabled, RCLK/SCLK Frequency = 4 x VCLK Frequency) | 2–10  |

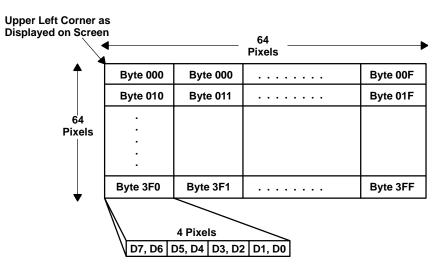

| 2–6    | CursorRAM Organization                                                               |       |

| 2–7    | Common Sprite-Origin Settings                                                        |       |

| 2–8    | Dual-Cursor Positioning                                                              | 2–26  |

| 2–9    | One Possible Custom-Cursor Creation                                                  | 2–26  |

| 2–10   | VGA in the Auxiliary Window                                                          | 2–29  |

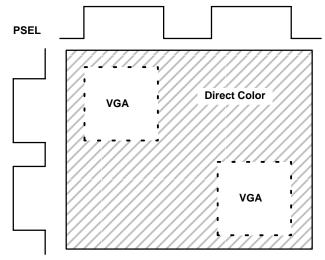

| 2–11   | Multiple VGA Windows Using Port Select (PSEL)                                        | 2–30  |

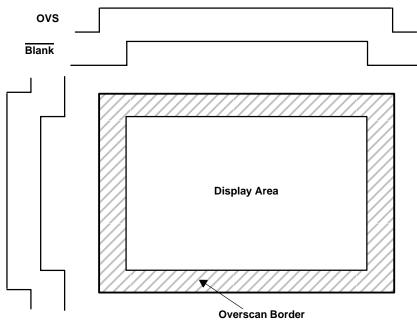

| 2–12   | Overscan                                                                             |       |

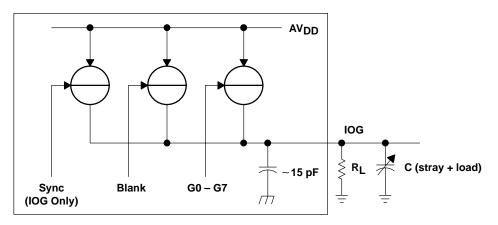

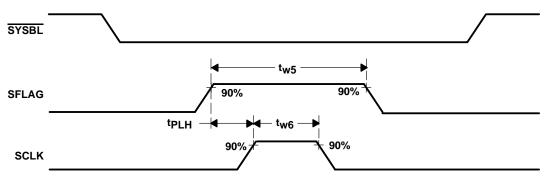

| 2–13   | Equivalent Circuit of the Current Output (IOG)                                       |       |

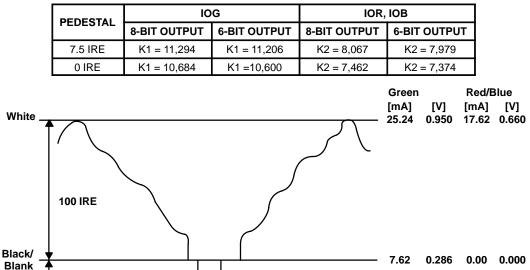

| 2–14   | Composite Video Output (With 0 IRE, 8-Bit Output)                                    |       |

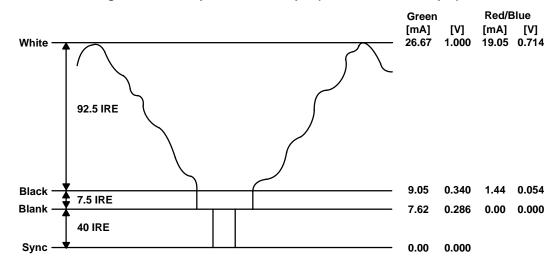

| 2–15   | Composite Video Output (With 7.5 IRE, 8-Bit Output)                                  |       |

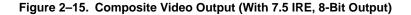

| 2–16   | Split Shift Register Transfer Timing                                                 | 2–37  |

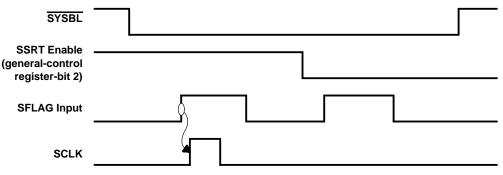

| 3–1    | MPU Interface Timing                                                                 | 3–11  |

| 3–2    | Video Input/Output Timing                                                            |       |

| 3–3    | SFLAG Timing (When SSRT Function is Enabled)                                         | 3–13  |

# **List of Tables**

| Table | Title                                                     | Page  |

|-------|-----------------------------------------------------------|-------|

| 2–1   | Direct Register Map                                       | . 2–1 |

| 2–2   | Indirect Register Map (Extended Registers)                | . 2–2 |

| 2–3   | Allocation of Palette-Page Register Bits                  | . 2–5 |

| 2–4   | Input-Clock-Selection Register                            | . 2–7 |

| 2–5   | Output-Clock-Selection Register Format                    | . 2–6 |

| 2–6   | Multiplex Mode and Bus-Width Selection                    | 2–15  |

| 2–7   | Pseudo-Color Mode Pixel-Latching Sequence                 | 2–18  |

| 2–8   | Direct-Color Mode Pixel-Latching Sequence (Little Endian) |       |

| 2–9   | Direct-Color Mode Pixel-Latching Sequence (Big Endian)    | 2–20  |

| 2–10  | True-Color Mode Pixel-Latching Sequence (Little Endian)   | 2–21  |

| 2–11  | True-Color Mode Pixel-Latching Sequence (Big Endian)      | 2–22  |

| 2–12  | Two-Color 64 × 64 Cursor-RAM Selection                    | 2–24  |

| 2–13  | Crosshair-Cursor Color Selection                          | 2–25  |

| 2–14  | Cursor-Intersection Truth Table                           | 2–27  |

| 2–15  | Windowing Control                                         | 2–28  |

| 2–16  | Zoom Control                                              | 2–32  |

| 2–17  | Sense-Test Register                                       | 2–34  |

| 2–18  | K1 and K2 Values Defined                                  | 2–36  |

| 2–19  | Configuration Register                                    | 2–38  |

| 2–20  | General Control Register                                  | 2–39  |

| 2–21  | Cursor Control Register                                   |       |

| 2–22  | Cursor Position X (LSB) and X (MSB)                       | 2–41  |

| 2–23  | Sprite Origin X and Y Registers                           | 2–42  |

| 2–24  | Window Start X and Y Registers                            | 2–43  |

| 2–25  | Window Stop X and Y Registers                             | 2–44  |

| 2–26  | Cursor-Color RGB Registers                                | 2–45  |

| 2–27  | Cursor RAM Address Register                               | 2–46  |

| 2–28  | Cursor RAM Data Register                                  | 2–46  |

| 2–29  | Auxiliary-Control Register                                | 2–47  |

| 2–30  | Color-Key Control Register                                | 2–48  |

| 2–31  | Color-Key Low and High Registers                          | 2–49  |

| 2–32  | Overscan-Color RGB Register                               | 2–50  |

| 2–33  | CRC MSB and LSB Registers                                 | 2–51  |

| 2–34  | CRC Control Register Format                               | 2–51  |

# 1 Introduction

The TVP3010C and the TVP3010M palettes are commercial and military versions, respectively, of an advanced Video Interface Palette (VIP) from Texas Instruments implemented in the EPIC<sup>™</sup> 0.8-micron CMOS process. Differences between the two versions are outlined in separate tables. In both versions, maximum flexibility is provided by the pixel multiplexing scheme. The scheme accommodates 64-, 32-, 16-, 8-, and 4-bit pixel buses without any circuit modification. This enables the system to be easily reconfigured for varying amounts of available video RAM. The device supports selection of little- or big-endian data format for the pixel-bus/frame-buffer interface. Data can be split into 1, 2, 4, or 8 bit-planes for pseudo-color mode or split into 12-, 16- or 24-bit true-color and direct-color modes. For the 24-bit direct-color modes, an 8-bit overlay plane is available. The 16-bit direct-color and true-color modes can be configured to IBM XGA<sup>®</sup> (5, 6, 5), TARGA<sup>®</sup> (5, 5, 5, 1), or (6, 6, 4) as another existing format. An additional 12-bit mode (4, 4, 4, 4) is supported with 4 bits for each color and overlay. An on-chip, IBM XGA-compatible hardware cursor is incorporated so that further increases in graphics-system performance are possible. Both devices are software compatible with the INMOS<sup>™</sup> IMSG176/8 and Brooktree<sup>™</sup> Bt476/8 color palettes.

An internal-frequency doubler is incorporated, allowing convenient and cost-effective clock-source alternatives to be utilized. An auxiliary windowing function and a pixel-port select function are provided so that overlay or VGA graphics can be displayed on top of direct color inside or outside a specified auxiliary window. Color-keyed switching of direct color and overlay is also supported.

Clocking is provided through one of five TTL inputs, CLK0–CLK4, and is software selectable. Additionally, CLK1/CLK2 and CLK3/CLK4 can be selected as differential ECL clock sources. The video, shift-clock, and reference-clock outputs provide a software-selected divide ratio of the chosen clock input. The reference clock can optionally be provided as an output on CLK3, and a data-latch clock can optionally be input on CLK4.

The TVP3010C and the TVP3010M have three 256  $\times$  8 color look-up tables with triple 8-bit video digital-to-analog converters (DACs) capable of directly driving a doubly-terminated 75- $\Omega$  line. The lookup tables are designed with a dual-ported RAM architecture that enables ultra-high speed operation. Sync generation is incorporated on the green output channel. Horizontal sync and vertical sync are fed through the device and optionally inverted to indicate screen resolution to the monitor. A palette-page register provides the additional bits of palette address when 1, 2, or 4 bit-planes are used. This allows the screen colors to be changed with only one microprocessor-interface unit (MPU) write cycle.

Each device features a separate VGA bus that allows data from the feature connector of most VGA-supported personal computers to be fed directly into the palette without the need for external data multiplexing. This allows a replacement graphics board to remain downwards compatible by utilizing the existing graphics circuitry often located on the motherboard.

Both the TVP3010 VIP and the TVP3010M VIP are highly system integrated. Either device can be connected to the serial port of a VRAM device without external buffer logic and each device can be connected to many graphics engines directly. The split shift register transfer function, which is supported by VRAM, is also supported by the TVP3010C and TVP3010M.

The system-integration concept is carried to manufacturing testing and field diagnosis levels. To support these testing and diagnostic levels, several highly-integrated test functions have been designed to enable simplified testing of the palette, the graphics board, and the graphics system.

EPIC is a trademark of Texas Instruments Incorporated. XGA is a registered trademark of International Business Machines Corporation. TARGA is a registered trademark of Truevision Incorporated. INMOS is a trademark of INMOS International Limited. Brooktree is a trademark of Brooktree Corporation. The TVP3010C and TVP3010M are 32-bit devices and both are pin compatible with the TLC3407X VIP, allowing convenient performance upgrades when using devices in the TI Video Interface Palette family.

#### NOTE:

The TVP3010C and TVP3010M include circuits that are patented as well as circuit designs that have patents pending.

# 1.1 Features (TVP3010C and TVP 3010M)

- Second-Generation Video Interface Palette

- Supports System Resolutions of:

- 1600 × 1280 × 1, 2, 4, 8, 16 Bits/Pixel @ 60-Hz Refresh Rate

- $1280 \times 1024 \times 1$ , 2, 4, 8, 16 Bits/Pixel @ 60-Hz and 72-Hz Refresh Rate

- $1024 \times 768 \times 1$ , 2, 4, 8, 16, 24 Bits/Pixel @ 60-Hz and 72-Hz Refresh Rate

- And Lower Resolutions

- Direct-Color Modes:

- 24-Bit/Pixel With 8-Bit Overlay

- 16-Bit/Pixel (5, 6, 5) XGA Configuration

- 16-Bit/Pixel (6, 6, 4) Configuration

- 15-Bit/Pixel With 1-Bit Overlay (5, 5, 5, 1) TARGA Configuration

- 12-Bit/Pixel With 4-Bit Overlay (4, 4, 4, 4)

- True-Color Modes:

- 24-Bit/Pixel With Gamma Correction

- 16-Bit/Pixel (5, 6, 5) XGA Configuration With Gamma Correction

- 16-Bit/Pixel (6, 6, 4) Configuration With Gamma Correction

- 15-Bit/Pixel (5, 5, 5) TARGA Configuration With Gamma Correction

- 12-Bit/Pixel (4, 4, 4) With Gamma Correction

- RCLK/SCLK/LCLK Data Latching Mechanism to Allow Flexible Control of VRAM Timing

- Direct Interfacing to Video RAM

- Support for Split Shift Register Transfers

- Supports 64-Bit-Wide Pixel Bus

- On-Chip Hardware Cursor:

- 64 × 64 × 2 Cursor (XGA Functionally Compatible)

- Full-Window Crosshair

- Dual-Cursor Mode

- 85-,110-,135-, and 170-MHz Versions

- Supports Overscan for Creation of Custom Screen Borders

- Versatile Pixel Bus Interface to Support Little- and Big-Endian Data Formats

- Windowed-Overlay and VGA Capability

- Color-Keyed Switching of Direct Color and Overlay

- On-Chip Clock Selection

- Internal Frequency Doubler

- Triple 8-Bit D/A Converters

- Analog Output Comparators

- Triple 256 × 8 Color-Palette RAMs

- RS-343A Compatible Outputs

- Direct VGA Pass-Through Capability

- Palette-Page Register

- Horizontal Zooming Capability

- Software Downward Compatible With IMSG176/8 and Bt476/8

- Directly to Graphics Processors

- EPIC 0.8-µm CMOS Process

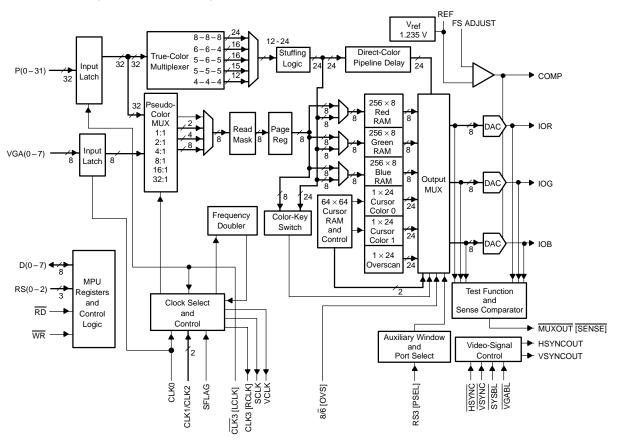

# 1.2 Functional Block Diagram

The following functional block diagram applies to both the TVP3010C and TVP3010M.

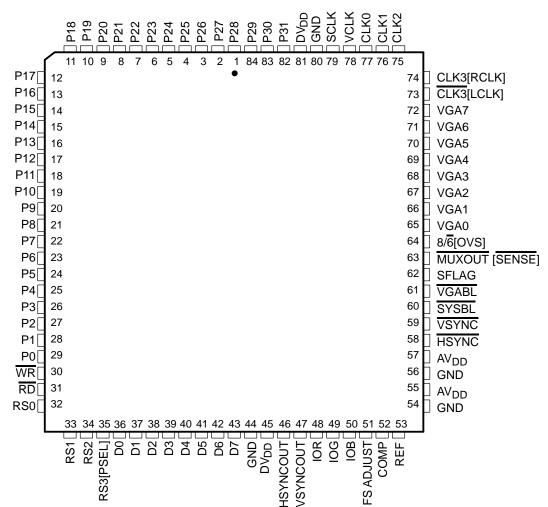

#### **1.3 Terminal Assignments**

84-PIN PLCC PACKAGE

# **1.3 Terminal Assignments (continued)**

| 12 | RS0 | D0  | D1            | D3   | D5              | D7                     | AVDD | HSYNC-<br>OUT | IOR              | IOB  | FS<br>ADJUST   | REF                        |

|----|-----|-----|---------------|------|-----------------|------------------------|------|---------------|------------------|------|----------------|----------------------------|

| 11 | WR  | RS2 | RS3<br>[PSEL] | D2   | D4              | D6                     | GND  | VSYNC-<br>OUT | IOG              | COMP | AVDD           | DVDD                       |

| 10 | P0  | RD  | RS1           |      |                 |                        |      | •             |                  | GND  | GND            | HSYNC                      |

| 9  | P2  | P1  |               |      |                 |                        |      |               |                  |      | VSYNC          | SYSBL                      |

| 8  | P4  | P3  |               |      |                 |                        |      |               |                  |      | VGABL          | SFLAG                      |

| 7  | P6  | P5  |               |      |                 |                        |      |               |                  |      | 8/6<br>[OVS]   | M <u>UXOU</u> T<br>[SENSE] |

| 6  | P8  | P7  |               |      |                 |                        |      |               |                  |      | VGA1           | VGA0                       |

| 5  | P9  | P10 |               |      |                 |                        |      |               |                  |      | VGA3           | VGA2                       |

| 4  | P11 | P12 |               | • (E | ESD symb<br>dot | ol or align<br>on top) | ment |               |                  |      | VGA5           | VGA4                       |

| 3  | P13 | P15 | P17           |      |                 |                        |      |               |                  | CLK2 | CLK3<br>[LCLK] | VGA6                       |

| 2  | P14 | P16 | P19           | P22  | P24             | P27                    | P29  | P31           | GND              | CLK0 | CLK1           | VGA7                       |

| 1  | P18 | P20 | P21           | P23  | P25             | P26                    | P28  | P30           | AV <sub>DD</sub> | SCLK | VCLK           | CLK3<br>[RCLK]             |

|    | А   | В   | С             | D    | Е               | F                      | G    | н             | J                | К    | L              | М                          |

#### 84-PIN GA PACKAGE (TOP VIEW)

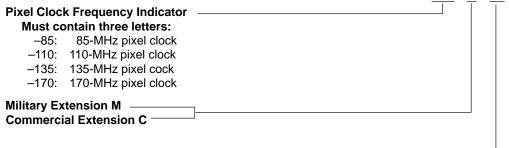

# 1.4 Ordering Information

TVP3010 XXX – X – XX

#### Package —

Must contain two Letters:

FN: square plastic J-leaded chip carrier

GA: 84-pin (12 x 12) ceramic pin-grid array

## 1.5 Terminal Functions (TVP3010C and TVP3010M)

| TERMINAL   |          | -            | 1/0                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|------------|----------|--------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME       | NO. (FN) | NO. (GA)     | 10                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| AVDD       | 55, 57   | J1, L11, G12 |                              | Analog power. All AV <sub>DD</sub> terminals must be connected.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| CLK0       | 77       | K2           | l<br>(TTL<br>compatible)     | Dot clock 0 input. CLK0 can be selected to drive the dot clock at frequencies up to 140 MHz. When VGA mode is active, the default clock source is CLK0. The maximum frequency in VGA mode is 85 MHz.                                                                                                                                                                                                                                                                      |  |  |

| CLK1, CLK2 | 75, 76   | L2, K3       | l<br>(TTL/ECL<br>compatible) | Dual-mode dot clock input. These inputs are essentially ECL-compatible inputs, but two TTL clocks may be used on the CLK1 and CLK2 if so selected in the input clock select register. These inputs may be selected as the dot clock up to the device limit while in the ECL mode or up to 140 MHz in the TTL mode.                                                                                                                                                        |  |  |

| CLK3[RCLK] | 74       | M1           | I/O                          | Dot clock 3 TTL input or reference clock output. When configured as CLK3, this terminal is similar to CLK0 and can be selected to drive the dot clock at frequencies up to 140 MHz. When configured as RCLK, this terminal outputs the reference clock signal, which is similar to the SCLK signal but not gated off during blanking. This signal can be used for pixel-port timing reference or other system synchronization. The terminal defaults to CLK3 after reset. |  |  |

| CLK3[LCLK] | 73       | L3           | I                            | Dot clock 4 TTL input or pixel-port latch clock. CLK3[LCLK] can be configured to drive dot clock frequencies up to 140 MHz, or it can be configured as a latch-clock input to latch pixel-port input data. It defaults to CLK4 after reset, and LCLK is internally connected to RCLK to latch pixel-port data.                                                                                                                                                            |  |  |

| COMP       | 52       | K11          | Ι                            | Compensation. COMP provides compensation for the internal reference amplifier. A 0.1- $\mu$ F ceramic capacitor is required between COMP and AV <sub>DD</sub> . The COMP capacitor must be as close to the device as possible to avoid noise pick up.                                                                                                                                                                                                                     |  |  |

| TERMINAL         |                   | 1/0                                                                                                                                                           | DESCRIPTION                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME             | NO. (FN)          | NO. (GA)                                                                                                                                                      | I/O                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| DV <sub>DD</sub> | 45, 81            | M11                                                                                                                                                           |                            | Digital power. All DV <sub>DD</sub> terminals must be connected together.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| D(0-7)           | 36-43             | B12, C12,<br>D11, D12,<br>E11, E12,<br>F11, F12                                                                                                               | I/O<br>(TTL<br>compatible) | MPU interface data bus. Data terminals are used to transfer data in and out of the register map and palette/overlay RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| FS ADJUST        | 51                | L12                                                                                                                                                           | I                          | Full-scale adjustment. A resistor connected between FS ADJUST and ground controls the full-scale range of the DACs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| GND              | 44, 54,<br>56, 80 | J2, L10,<br>K10, G11                                                                                                                                          |                            | Ground. All GND terminals must be connected. The GNDs are connected internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| HSYNCOUT         | 46                | H12                                                                                                                                                           | O<br>(TTL<br>compatible)   | Horizontal sync output after pipeline delay. For<br>system mode the horizontal-sync output can be<br>programmed, but for the VGA mode the output<br>carries the same polarity as the input.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| IOR, IOG, IOB    | 48, 49, 50        | J12, J11,<br>K12                                                                                                                                              | 0                          | Analog current outputs. These outputs can drive a $37.5 \cdot \Omega$ load directly (doubly terminated $75 \cdot \Omega$ line), thus eliminating the requirement for any external buffering.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| MUXOUT [SENSE]   | 63                | Μ7                                                                                                                                                            | O<br>(TTL<br>compatible)   | Multiplexer output control or DAC comparator output signal. When MUXOUT is configured as a multiplexer output control, it is software programmable through the configuration register. When the multiplexer control register is set to VGA mode, this output terminal and corresponding configuration register bit are set low to indicate to external devices that the VGA pass-through mode is being used. Alternatively, SENSE can be configured as the DAC comparator output. In this case, the SENSE is low when one or more of the DAC output analog levels is above the internal comparator reference of 350 mV $\pm$ 50 mV. |  |

| P(0-31)          | 1–29,<br>82–84    | A10, B9, A9,<br>B8, A8, B7,<br>A7, B6, A6,<br>A5, B5, A4,<br>B4, A3, A2,<br>B3, B2, C3,<br>A1, C2, B1,<br>C1, D2, D1,<br>E2, E1, F1,<br>F2, G1, G2,<br>H1, H2 | I<br>(TTL<br>compatible)   | Pixel input port. The port can be used in various<br>modes as shown in the multiplexer control register.<br>All the unused terminals need to be tied to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

# 1.5 Terminal Functions (TVP3010C and TVP3010M) Continued

NOTE 1: All unused inputs should be tied to a logic level and not be allowed to float.

# 1.5 Terminal Functions (TVP3010C and TVP3010M) Continued

| TERMINAL        |          | DECODIDION                           |                          |                                                                                                                                                                                                                                                                                                                                       |

|-----------------|----------|--------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. (FN) | NO. (GA)                             | I/O                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                           |

| REF             | 53       | M12                                  |                          | Voltage reference for DACs. An internal voltage reference of nominally 1.235 V is provided, which requires an external 0.1- $\mu$ F ceramic capacitor between REF and analog GND. However, the internal reference voltage can be overdriven by an externally supplied reference voltage. A typical connection is shown in Appendix A. |

| RD              | 31       | B10                                  | l<br>(TTL<br>compatible) | Read strobe inputs When cleared to 0, $\overline{\text{RD}}$ initiates a read from the register map. Reads are performed asynchronously and are initiated on the low-going edge of $\overline{\text{RD}}$ (see Figure 3–1).                                                                                                           |

| RS(0-2)         | 32-34    | A12, C10,<br>B11                     | l<br>(TTL<br>compatible) | Register-select inputs. The RS terminals specify the location in the register map that is to be accessed (see Table 2–1).                                                                                                                                                                                                             |

| RS3 [PSEL]      | 35       | C11                                  | l<br>(TTL<br>compatible) | Register-select input or port-select input. When configured<br>as the RS3 input, this terminal has no effect. When<br>configured as the port-select input, RS3 [PSEL] allows the<br>creation of VGA or overlay windows in a direct-color<br>background on a pixel-by-pixel basis.                                                     |

| SCLK            | 79       | К1                                   | O<br>(TTL<br>compatible) | Shift clock output. SCLK is selected as a division of the dot clock input. The output signals are gated off during blanking, although SCLK is still used internally to synchronize with the activation of Blank.                                                                                                                      |

| SFLAG           | 62       | M8                                   | l<br>(TTL<br>compatible) | Split shift register transfer flag. The TVP3010 detects a low-to-high transition on SFLAG during a blanking sequence and immediately generates an SCLK pulse. This early SCLK pulse replaces the first SCLK pulse in the normal sequence.                                                                                             |

| SYSBL           | 60       | M9                                   | l<br>(TTL<br>compatible) | System blank input. SYSBL is active (low).                                                                                                                                                                                                                                                                                            |

| HSYNC,<br>VSYNC | 58, 59   | M10, L9                              | l<br>(TTL<br>compatible) | Horizontal and vertical sync inputs. These signals<br>generate the sync level on the green current output. They<br>are active (low) inputs, but the HSYNCOUT and<br>VSYNCOUT outputs can be programmed through the<br>general control register.                                                                                       |

| VCLK            | 78       | L1                                   | O<br>(TTL<br>compatible) | Video clock output. VCLK is the user-programmable output for synchronization to the graphics processor.                                                                                                                                                                                                                               |

| VGABL           | 61       | L8                                   | l<br>(TTL<br>capability) | VGA blank input. VGABL is active (low).                                                                                                                                                                                                                                                                                               |

| VGA(0-7)        | 65–72    | M6, L6, M5,<br>L5, M4, L4,<br>M3, M2 | l<br>(TTL<br>capability) | VGA pass-through bus. These buses can be selected as the pixel bus for VGA mode, but it does not allow for any multiplexing.                                                                                                                                                                                                          |

NOTE 1: All unused inputs should be tied to a logic level and not be allowed to float.

|           | TERMINAL |          | 1/0                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|----------|----------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO. (FN) | NO. (GA) | 1/0                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VSYNCOUT  | 47       | H11      | O<br>(TTL<br>capability) | Vertical sync output after pipeline delay. For system<br>mode, the output can be programmed, but for the<br>VGA mode the output carries the same polarity as<br>the input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WR        | 30       | A11      | l<br>(TTL<br>capability) | Write strobe input. A low on $\overline{WR}$ initiates a write to the register map. As with $\overline{RD}$ , write transfers are asynchronous and initiated on the low-going edge of $\overline{WR}$ , (see Figure 3–1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8/6 [OVS] | 64       | L7       | l<br>(TTL<br>capability) | DAC resolution selection or overscan input. The 8/6<br>terminal selects the data-bus width (8 or 6 bits) for<br>the DAC and is essentially provided in order to<br>maintain compatibility with the IMSG176. When 8/6<br>[OVS] is high, 8-bit bus transfers are used with D7<br>the MSB and D0 the LSB. For 6-bit bus operation,<br>while the color palette still has the 8-bit information,<br>D5 shifts to the bit 7 position with D0 shifted to the bit<br>2 position and the 2 LSBs are filled with zeros at the<br>output multiplexer to DAC. The palette-holding<br>register zeroes the two MSBs when it is read in the<br>6-bit mode. The terminal can also be configured to<br>function as the overscan input facilitating the<br>creation of custom screen borders. This terminal<br>defaults to 8/6 after reset. |

# 1.5 Terminal Functions (TVP3010C and TVP3010M) Continued

NOTE 1: All unused inputs should be tied to a logic level and not be allowed to float.

# 2 Detailed Description

The TVP3010C and TVP3010M VIPs are identical in their operation. Both the TVP3010C and TVP3010M are 32-bit devices; both devices are terminal compatible with the TLC34076 and each device offers advanced features. To facilitate the enhanced functionality, some terminals have dual functions. The dual-function terminals are controlled by the configuration register discussed in subsection 2.16.1. At reset, all pins default to the TLC34076 terminal functions.

#### 2.1 **MPU Interface**

The microprocessor unit (MPU) interface is controlled using read and write strobes (RD, WR), three register-select terminals [RS(0-2)], and the 8/6-select terminal. The 8/6 pin selects between an 8- or 6-bit-wide data path to the color-palette RAM and is provided in order to maintain compatibility with the IMSG176. Since the 8/6 [OVS] pin is a dual-function pin, 2 bits are provided in the configuration register to control this function. Configuration-register bit 1 determines whether the 8/6 [OVS] pin operates as 8/6 or OVS. If configuration register bit 1 is cleared to 0 (default), then 8/6 operation is controlled by the pin. With 8/6 held low, data on the lowest 6 bits of the data bus are internally shifted up by 2 bits to occupy the upper 6 bits at the output multiplexer and the bottom 2 bits are then cleared to 0. This operation is carried out in order to utilize the maximum range of the DACs.

The direct register map is shown in Table 2–1. Extended registers can be accessed through the index register. The index register map is shown in Table 2-2. In general, the index register must first be loaded with the target address value. Successive reads or writes from and to the data register then access the target location. The MPU interface operates asynchronously, with data transfers being synchronized by internal logic.

| ······ |     |     |                                       |     |               |  |  |  |  |

|--------|-----|-----|---------------------------------------|-----|---------------|--|--|--|--|

| RS2    | RS1 | RS0 | REGISTER ADDRESSED BY MPU             | R/W | DEFAULT (HEX) |  |  |  |  |

| 0      | 0   | 0   | Palette Address Register – Write Mode | R/W | XX            |  |  |  |  |

| 0      | 0   | 1   | Color Palette Holding Register        | R/W | XX            |  |  |  |  |

| 0      | 1   | 0   | Pixel Read Mask                       | R/W | FF            |  |  |  |  |

| 0      | 1   | 1   | Palette Address Register – Read Mode  | R/W | XX            |  |  |  |  |

| 1      | 0   | 0   | Reserved                              |     | XX            |  |  |  |  |

| 1      | 0   | 1   | Reserved                              |     | XX            |  |  |  |  |

| 1      | 1   | 0   | Index Register                        | R/W | XX            |  |  |  |  |

| 1      | 1   | 1   | Data Register                         | R/W | ХХ            |  |  |  |  |

RS3 is a do not care for register addressing but is used as the PSEL input (see Section 2.6).

|  | Ν | 10 | T | E | : |

|--|---|----|---|---|---|

|  |   |    | - |   |   |

Table 2–1. Direct Register Map

| INDEX REGISTER<br>(HEX) | R/W | DEFAULT<br>(HEX) | REGISTER ADDRESSED<br>BY INDEX REGISTER |  |

|-------------------------|-----|------------------|-----------------------------------------|--|

| 00                      | R/W | 00               | Cursor Position X LSB                   |  |

| 01                      | R/W | 00               | Cursor Position X MSB                   |  |

| 02                      | R/W | 00               | Cursor Position Y LSB                   |  |

| 03                      | R/W | 00               | Cursor Position Y MSB                   |  |

| 04                      | R/W | 1F               | Sprite Origin X                         |  |

| 05                      | R/W | 1F               | Sprite Origin Y                         |  |

| 06                      | R/W | 00               | Cursor Control Register                 |  |

| 07                      |     |                  | Reserved                                |  |

| 08                      | W   | XX               | Cursor RAM Address LSB                  |  |

| 09                      | W   | XX               | Cursor RAM Address MSB                  |  |

| 0A                      | R/W | ХХ               | Cursor RAM Data                         |  |

| 0B                      |     |                  | Reserved                                |  |

| 0C-0F                   |     |                  | Reserved-Undefined                      |  |

| 10                      | R/W | XX               | Window Start X LSB                      |  |

| 11                      | R/W | XX               | Window Start X MSB                      |  |

| 12                      | R/W | XX               | Window Stop X LSB                       |  |

| 13                      | R/W | ХХ               | Window Stop X MSB                       |  |

| 14                      | R/W | ХХ               | Window Start Y LSB                      |  |

| 15                      | R/W | XX               | Window Start Y MSB                      |  |

| 16                      | R/W | XX               | Window Stop Y LSB                       |  |

| 17                      | R/W | XX               | Window Stop Y MSB                       |  |

| 18                      | R/W | 80               | Multiplexer Control Register 1          |  |

| 19                      | R/W | 98               | Multiplexer Control Register 2          |  |

| 1A                      | R/W | 00               | Input-Clock Selection Register          |  |

| 1B                      | R/W | 3E               | Output-Clock Selection Register         |  |

| 1C                      | R/W | 00               | Palette Page Register                   |  |

| 1D                      | R/W | 20               | General Control Register                |  |

| 1E                      | R/W | 00               | Configuration Register                  |  |

| 1F                      |     |                  | Reserved-Undefined                      |  |

| 20                      | R/W | ХХ               | Overscan Color Red                      |  |

| 21                      | R/W | XX               | Overscan Color Green                    |  |

Table 2–2. Indirect Register Map (Extended Registers)

NOTE 1: Reserved registers should be avoided; otherwise, circuit behavior could deviate from that specified. Reserved-undefined registers are nonexistent locations on the register map.

| INDEX REGISTER<br>(HEX) | R/W | DEFAULT<br>(HEX) | REGISTER ADDRESSED<br>BY INDEX REGISTER |

|-------------------------|-----|------------------|-----------------------------------------|

| 22                      | R/W | XX               | Overscan Color Blue                     |

| 23                      | R/W | XX               | Cursor Color 0, Red                     |

| 24                      | R/W | XX               | Cursor Color 0, Green                   |

| 25                      | R/W | XX               | Cursor Color 0, Blue                    |

| 26                      | R/W | XX               | Cursor Color 1, Red                     |

| 27                      | R/W | XX               | Cursor Color 1, Green                   |

| 28                      | R/W | XX               | Cursor Color 1, Blue                    |

| 29                      | R/W | 09               | Auxiliary-Control Register              |

| 2A                      |     |                  | Reserved                                |

| 2B                      |     |                  | Reserved                                |

| 2C                      |     |                  | Reserved                                |

| 2D                      |     |                  | Reserved                                |

| 2E                      |     |                  | Reserved                                |

| 2F                      |     |                  | Reserved                                |

| 30                      | R/W | XX               | Color-Key OL/VGA Low                    |

| 31                      | R/W | XX               | Color-Key OL/VGA High                   |

| 32                      | R/W | XX               | Color-Key Red Low                       |

| 33                      | R/W | XX               | Color-Key Red High                      |

| 34                      | R/W | XX               | Color-Key Green Low                     |

| 35                      | R/W | XX               | Color-Key Green High                    |

| 36                      | R/W | XX               | Color-Key Blue Low                      |

| 37                      | R/W | XX               | Color-Key Blue High                     |

| 38                      | R/W | 10               | Color-Key Control Register              |

| 39                      |     |                  | Reserved-Undefined                      |

| ЗA                      | R/W | 00               | Sense-Test Register                     |

| 3B                      | R   | XX               | Test-Data Register                      |

| 3C                      | R   | XX               | CRC LSB                                 |

| 3D                      | R   | XX               | CRC MSB                                 |

| 3E                      | W   | XX               | CRC Control Register                    |

| 3F                      | R   | 10               | ID Register                             |

| FF                      | W   | XX               | Reset Register                          |

Table 2–2. Indirect Register Map (Extended Registers) (Continued)

NOTE 1: Reserved registers should be avoided; otherwise, circuit behavior could deviate from that specified. Reserved-undefined registers are nonexistent locations on the register map.

# 2.2 Color Palette

The color palette is addressed by an internal 8-bit address register for reading/writing data from/to the RAM. This register is automatically incremented following a RAM transfer, allowing the entire palette to be read/written with only one access of the address register. When the address register increments beyond the last location in RAM, it is reset to the first location (address 0). All read and write accesses to the RAM are asynchronous to SCLK, VCLK, and dot clock but performed within one dot clock. Therefore, they do not cause any noticeable disturbance on the display.

The color RAM is 24 bits wide for each location and 8 bits wide for each color. Since the MPU access is 8 bits wide, the color data stored in the palette is 8 bits even when the 6-bit mode is chosen  $(8/\overline{6} = 0)$ . If the 6-bit mode is chosen, the 2 MSBs of color data in the palette have the values previously written. However, if they are read back in the 6-bit mode, the 2 MSBs are 0s to be compatible with IMSG176 and Bt176. The output multiplexer shifts the six LSB to the six MSB positions and fills the 2 LSBs with 0s after the color palette. The multiplexer then feeds the data to the DAC. The test register and the CRC calculation both take data after the output multiplexer, enabling total system verification. The color-palette access is described in the following two sections, and it is fully compatible with IMSG176/8 and Bt476/8.

#### 2.2.1 Writing to Color-Palette RAM

To load the color palette, the MPU must first write to the address register (write mode) with the address where the modification is to start. This is then followed by three successive writes to the palette-holding register with 8 bits of red, green, and blue data. After the blue write cycle, the three bytes of color data are concatenated into a 24-bit word that is then written to the RAM location specified by the address register. The address register then increments to the next location, which the MPU may modify by simply writing another sequence of red, green, and blue data. A block of color values in consecutive locations may be written to by writing the start address and performing continuous red, green, and blue write cycles until the entire block has been written.

### 2.2.2 Reading From Color-Palette RAM

Reading from the palette is performed by writing to the address register (read mode) with the location to be read. This then initiates a transfer from the palette RAM into the holding register, followed by an increment of the address register. Three successive MPU reads from the holding register produce red, green, and blue color data (6 or 8 bits depending on the 8/6 mode) for the specified location. Following the blue read-cycle, the contents of the color-palette RAM at the address specified by the address register are copied into the holding register and the address register is again incremented. As with writing to the palette, a block of color values in consecutive locations may be read by writing the start address and performing continuous red, green, and blue read-cycles until the entire block has been read. Since the color-palette RAM is dual ported, the RAM may be read during active display without disturbing the video.

### 2.2.3 Palette Page Register

The palette page register appears as an 8-bit register on the extended register map (see Section 2.1). Its purpose is to provide high-speed color changing by removing the need for palette reloading. When using 1, 2, or 4 bit-planes, the additional planes are provided from the page register. When using four bit-planes, the pixel inputs specify the lower 4 bits of the palette address with the upper 4 bits specified from the page register. This gives the user the capability of selecting from 16 palette pages with only one-chip access, thus allowing all the screen colors to be changed at the line frequency. A bit-to-bit correspondence is used; therefore, in the above configuration, page-register bits 7 through 4 map onto palette-address bits 7 through 4, respectively. This is illustrated in Table 2–3.

#### NOTE:

The additional bits from the page register are inserted after the read mask.

The palette page register specifies the additional bit-planes for the overlay field in direct-color modes with less than 8 bits per pixel overlay.

| NUMBER OF BIT PLANES | MSB |    | PALET | TE-AD | DRES | S BITS |    | LSB |

|----------------------|-----|----|-------|-------|------|--------|----|-----|

| 8                    | м†  | М  | М     | М     | М    | М      | М  | М   |

| 4                    | P7‡ | P6 | P5    | P4    | М    | М      | М  | М   |

| 2                    | P7  | P6 | P5    | P4    | P3   | P2     | М  | М   |

| 1                    | P7  | P6 | P5    | P4    | P3   | P2     | P1 | М   |

Table 2–3. Allocation of Palette Page Register Bits

$^{\dagger}$  M = bit from pixel port

‡ Pn = n bit from page register

#### 2.2.4 Read Masking

The read-mask register is an 8-bit register used to enable or disable a bit-plane from addressing the color-palette RAM in the pseudo-color modes. Each palette address bit is logically ANDed with the corresponding bit from the read mask register before going to the palette page register and addressing the palette RAM.

In order to provide maximum flexibility to control palette data, the read mask operation is performed before the addition of the page register bits. Therefore, care must be taken in those modes that have less than 8 bits per pixel of pseudo-color or overlay data. Be aware of the palette page register settings in these modes.

# 2.3 Clock Selection and Output-Clock (SCLK, RCLK, and VCLK) Generation

The TVP3010C and the TVP3010M VIP provide a maximum of five clock inputs. CLK0 is dedicated as a TTL input. The other four clock inputs can be selected as either two differential ECL input or two extra TTL inputs. The TTL inputs can be used for video rates up to 140 MHz. The dual-mode clock input (ECL/TTL) is primarily an ECL input but can be used as TTL-compatible inputs if the input-clock selection register is so programmed. The clock source used at power up is CLK0; an alternative source can be selected by software during normal operation. This chosen clock input can be used as a reference for multiplication. Each device also allows for user programming of RCLK, SCLK and VCLK outputs (reference, shift and video clocks) by using the output-clock selection register. The input-clock and output-clock selection registers are located in the indirect register map (see Table 2–2).

The ECL inputs can be used as differential or single-ended inputs. When CLK1 or CLK3 is used as a single-ended ECL input, CLK2 or CLK4 needs to be externally terminated to set the input common-mode signal level. This can be done with a simple resistor divider, as is the case with fully differential ECL. Care needs to be taken when choosing the resistor values to ensure that the dc level on CLK2 or CLK4 is in the middle of the CLK1 or CLK3 ECL-input signal range.

### 2.3.1 RCLK, SCLK, VCLK

Both VIP devices provide a user-programmable reference clock (RCLK), a shift clock (SCLK), and video (VCLK) clock outputs that can be set as divisions of the dot clock. RCLK is a continuously-running reference clock and is not disabled during the Blank signal. RCLK can be selected as divisions of 1, 2, 4, 8, 16, 32 or 64 of the

dot clock (see Table 2–4). It is provided as a clock reference and is typically connected back to the LCLK input to latch pixel-port data. Since pixel-port data is latched on the rising edge of LCLK, the RCLK frequency must be set as a function of the desired multiplexing ratio (that depends on the pixel-bus width and number of bit-planes, see Section 2.4).

| OUTPUT-CLOCK SELECTION-REGISTER BITS (see Note 2) |   |   |   |   |   |   | FUNCTION (see Notes 2, 2, 4, and 5)               |  |

|---------------------------------------------------|---|---|---|---|---|---|---------------------------------------------------|--|

| 6                                                 | 5 | 4 | 3 | 2 | 1 | 0 | FUNCTION (see Notes 2, 3, 4, and 5)               |  |

|                                                   | 0 | 0 | 0 | х | х | х | VCLK/1 output ratio                               |  |

|                                                   | 0 | 0 | 1 | х | х | х | VCLK/2 output ratio                               |  |

|                                                   | 0 | 1 | 0 | х | х | х | VCLK/4 output ration                              |  |

|                                                   | 0 | 1 | 1 | х | х | х | VCLK/8 output ratio                               |  |

|                                                   | 1 | 0 | 0 | х | х | х | VCLK/16 output ratio                              |  |

|                                                   | 1 | 0 | 1 | х | х | х | VCLK/32 output ratio                              |  |

|                                                   | 1 | 1 | 0 | х | х | х | VCLK/64 output ratio                              |  |

|                                                   | 1 | 1 | 1 | х | х | х | VCLK output held at logic 1 <sup>†</sup>          |  |

|                                                   | х | х | х | 0 | 0 | 0 | RCLK/1 output ratio (see Notes 2 and 5)           |  |

|                                                   | x | х | х | 0 | 0 | 1 | RCLK/2 output ratio (see Notes 2 and 5)           |  |

|                                                   | х | х | х | 0 | 1 | 0 | RCLK/4 output ratio (see Notes 2 and 5)           |  |

|                                                   | х | х | х | 0 | 1 | 1 | RCLK/8 output ratio (see Notes 2 and 5)           |  |

|                                                   | х | х | х | 1 | 0 | 0 | RCLK/16 output ratio (see Notes 2 and 5)          |  |

|                                                   | х | х | х | 1 | 0 | 1 | RCLK/32 output ratio (see Notes 2 and 5)          |  |

|                                                   | х | х | х | 1 | 1 | 0 | RCLK/64 output ratio (see Notes 2 and 5)          |  |

| 0                                                 | х | х | х | 1 | 1 | 0 | RCLK/64, SCLK output held at logic 0 <sup>†</sup> |  |

| 0                                                 | х | х | х | 1 | 1 | 1 | RCLK, SCLK outputs held at logic 0                |  |

| х                                                 | 1 | 1 | 1 | 1 | 1 | 1 | Clock counter reset (6)                           |  |

Table 2–4. Output-Clock Selection Register Format

<sup>†</sup> These lines indicate the reset conditions as required for VGA pass-through.

NOTES: 2. Register bit 6 enables (1) and disables (default = 0) the SCLK output buffer. Register bit 7 is a don't care bit.

- 3. When the clocks are selected from one mode to the other, a minimum of 30 ns is needed before the new clocks are stabilized and running.

- 4. When the output-clock-selection register is written with 3F (hex), the clock counter is reset, RCLK = SCLK = 0, and VCLK = 1.

- 5. SCLK is the same as RCLK except that it is disabled during blank. When the RCLK divide ratio is chosen, this sets the SCLK ratio as well.

SCLK is the same as RCLK but disabled during the Blank active period. SCLK is designed to be used as the shift clock to interface directly with the VRAM. If SCLK is not used, the output can be switched off and held low to protect against VRAM lockup due to invalid SCLK frequencies. The detailed SCLK control timing is discussed in subsection 2.3.2.

VCLK is designed to be used as the timing reference by the <u>graphics processor</u> or <u>other custom-designed</u> control logic to generate the graphics system control signals (SYSBL, HSYNC, and VSYNC). VCLK can be selected as divisions of 1, 2, 4, 8, 16, 32, or 64 of the dot clock and can also be held at high (see Table 2–4). The default setup is VCLK held at high since it is not used in VGA pass-through mode. Since these control signals are sampled by VCLK, VCLK must be enabled for these to function properly.

Even though RCLK/SCLK and VCLK can be selected independently, there is still a relationship between the two as discussed below. Many system considerations have been carefully covered in their design, leaving maximum freedom to the user.

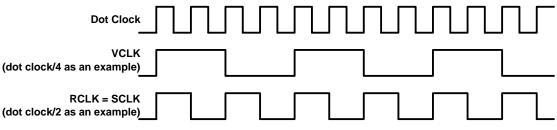

Internally, RCLK, SCLK, and VCLK are generated from a common clock counter that is counted at the rising edge of the dot clock. Therefore, when VCLK is enabled, it is naturally in phase with RCLK and SCLK as shown in Figure 2–1.

Normally, the video-control signal inputs HSYNC, VSYNC, and SYSBL are latched on the falling edge of VCLK when in a non-VGA mode. When the configuration register is programmed for opposite VCLK polarity, these video-control signals are latched on the rising edge of VCLK.

The internal clock counter is initialized any time the output-clock selection register is written with 3F (hex). This provides a simple mechanism to synchronize multiple palettes or system devices by providing a known phase relationship for the various system clocks. It is left up to the user to provide some means of disabling the dot-clock input to the part while this reset is occurring if multiple parts are to be synchronized.

The reset default divide ratio for RCLK is 64:1 with SCLK held low and VCLK held at high. When choosing certain video timing parameters, exercise caution if the selected RCLK frequency is less than the selected VCLK frequency (see Appendix B for a more detailed discussion).

Figure 2–1. Dot Clock/VCLK/RCLK/SCLK Relationship

The input-clock-selection register selects the desired input-clock source. Table 2–5 details how to program the various options.

Table 2–5. Input-Clock Selection Register

| INPUT-CLOCK-SELECT REGISTER<br>(HEX) (see Note 6) | FUNCTION (see Note 7)                                   |

|---------------------------------------------------|---------------------------------------------------------|

| 00                                                | Select CLK0 as TTL-clock source <sup>†</sup>            |

| 01                                                | Select CLK1 as TTL-clock source                         |

| 02                                                | Select CLK2 as TTL-clock source                         |

| 03                                                | Select CLK3 as TTL-clock source                         |

| 04                                                | Select CLK4 as TTL-clock source                         |

| 06                                                | Select CLK3/CLK4 as ECL-clock source up to 140 MHz      |

| 07                                                | Select CLK1/CLK2 as ECL-clock source up to device limit |

| 10                                                | Select CLK0 as doubled TTL-clock source                 |

| 11                                                | Select CLK1 as doubled TTL-clock source                 |

| 12                                                | Select CLK2 as doubled TTL-clock source                 |

| 13                                                | Select CLK3 as doubled TTL-clock source                 |

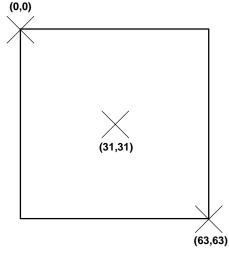

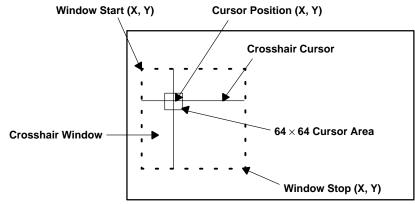

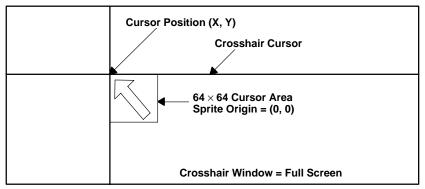

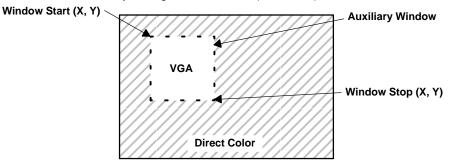

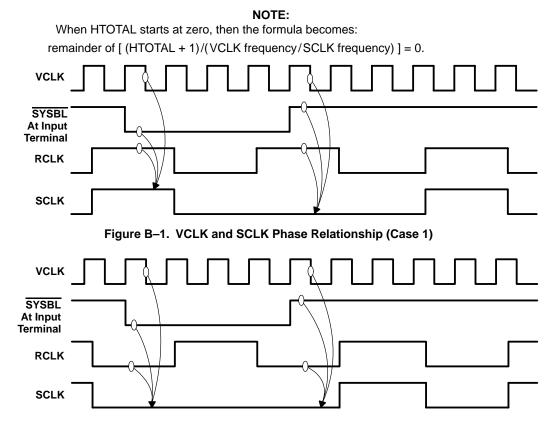

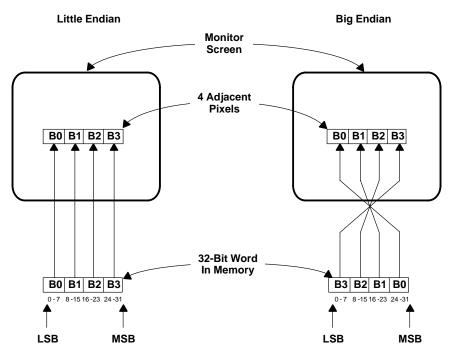

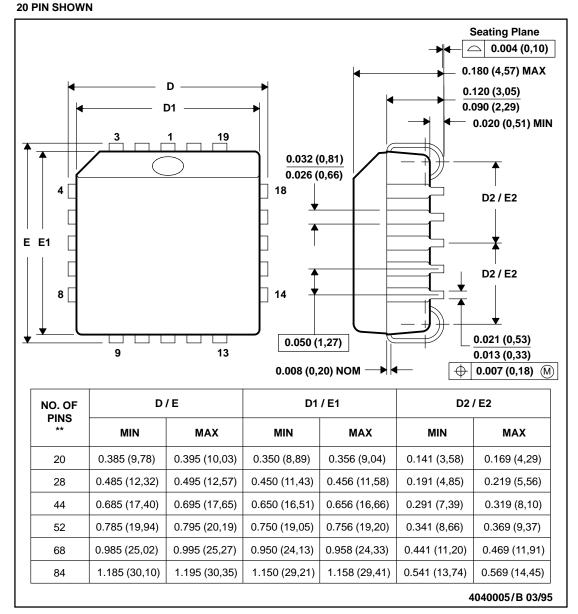

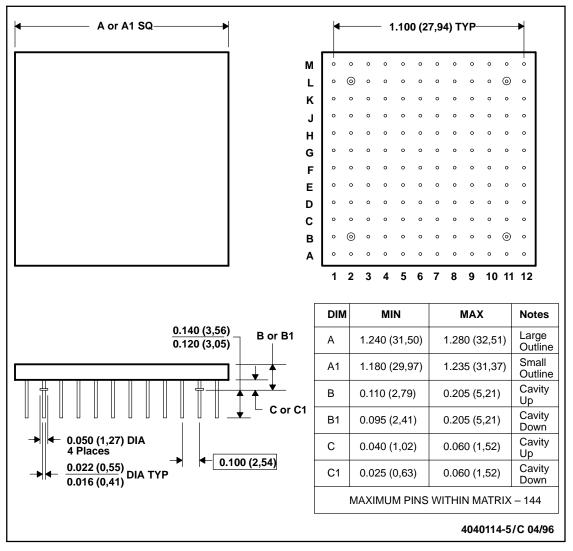

| 14                                                | Select CLK4 as doubled TTL-clock source                 |