# VECTOR 3

# HARDWARE

MANUAL

# VECTOR 3 HARDWARE MANUAL

REVISION A

AUGUST 18, 1980

Copyright 1980 Vector Graphic Inc.

# Copyright 1980 by Vector Graphic Inc. All rights reserved.

#### Disclaimer

Vector Graphic makes no representations or warranties with respect to the contents of this manual itself, whether or not the product it describes is covered by a warranty or repair agreement. Further, Vector Graphic reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of Vector Graphic to notify any person of such revision or changes, except when an agreement to the contrary exists.

#### Revisions

The date and revision of each page herein appears at the bottom of each page. The revision letter such as A or B changes if the MANUAL has been improved but the PRODUCT itself has not been significantly modified. The date and revision on the Title Page corresponds to that of the page most recently revised. When the product itself is modified significantly, the product will get a new revision number, as shown on the manual's title page, and the manual will revert to revision A, as if it were treating a brand new product. EACH MANUAL SHOULD ONLY BE USED WITH THE PRODUCT IDENTIFIED ON THE TITLE PAGE.

#### REPAIR AGREEMENT

The Vector 3 or its variations sold hereunder is sold "as is", with all faults and without any warranty, either expressed or implied, including any implied warranty of fitness for intended use or merchantability. However, the above notwithstanding, VECTOR GRAPHIC, INC., will, for a period of ninety (90) days following delivery to customer, repair or replace any Vector 3 or its variations that is found to contain defects in materials or workmanship, provided:

- 1. Such defect in material or workmanship existed at the time the Vector 3 or its variations left the VECTOR GRAPHIC, INC., factory;

- 2. VECTOR GRAPHIC, INC., is given notice of the precise defect claimed within ten (10) days after its discovery;

- 3. The Vector 3 or its variations is promptly returned to VECTOR GRAPHIC, INC., at customer's expense, for examination by VECTOR GRAPHIC, INC., to confirm the alleged defect, and for subsequent repair or replacement, if found to be in order.

Repair, replacement or correction of any defects in material or workmanship which are discovered after expiration of the period set forth above will be performed by VECTOR GRAPHIC, INC., at Buyer's expense, provided the Vector 3 or its variations is returned, also at Buyer's expense, to VECTOR GRAPHIC, INC., for such repair, replacement or correction. In performing any repair, replacement or correction after expiration of the period set forth above, Buyer will be charged in addition to the cost of parts the then-current VECTOR GRAPHIC, INC., repair rate. At the present time the applicable rate is \$35.00 for the first hour, and \$18.00 per hour for every hour of work required Prior to commencing any repair, replacement or correction of defects in material or workmanship discovered after expiration of the period for no-cost-to-Buyer repairs, VECTOR GRAPHIC, INC., will submit to Buyer a written estimate of the expected charges, and VECTOR GRAPHIC, INC., will not commence repair until such time as the written estimate of charges has been returned by Buyer to VECTOR GRAPHIC, INC., signed by duly authorized representative authorizing VECTOR GRAPHIC, INC., to commence with the repair work involved. VECTOR GRAPHIC, INC., shall have no obligation to repair, replace or correct any Vector 3 or its variations until the written estimate has been returned with approval to proceed, and VECTOR GRAPHIC, INC., may at its option also require prepayment of the estimated repair charges prior to commencing work.

Repair Agreement void if the enclosed card is not returned to VECTOR GRAPHIC, INC. within ten (10) days of end consumer purchase.

|  |   | , |  |

|--|---|---|--|

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  | , |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

#### **FOREWORD**

Audience

This manual is intended for dealers, distributors, salespersons, consultants, and service personnel. It requires a minimum of technical knowledge.

Scope

It describes what the Vector Graphic Vector 3 hardware consists of, the function of the hardware, how to adjust and test the hardware components, and some preliminary troubleshooting procedures for these components. This manual is intended for use with Vector 3 microcomputers built with the C. Itoh video subassembly.

Organization

For many dealers and users, no other hardware manuals will be necessary, though technicians will make use of the more technical publications. Users will reference specific software manuals, depending on the particular application.

# TABLE OF CONTENTS

| Sect: | ion   |          |                                        | Page              |

|-------|-------|----------|----------------------------------------|-------------------|

|       | Table | e of Co  | ntents                                 |                   |

|       | List  | of Illi  | ustrations                             |                   |

|       | Hardy | vare Spe | ecifications                           |                   |

| I.    | Pers  | ective   |                                        |                   |

|       | 1.1   | Introd   | uction                                 | 1-1               |

| II.   | Video | o Conso  | le                                     |                   |

|       | 2.1   | 2.1.1    | Adjusting Procedures for Video Monitor | 2-1<br>2-1<br>2-6 |

|       | 2.2   | 2.2.1    | Keyboard Connection                    | 2-7               |

| III.  | Main  | frame    |                                        |                   |

|       | 3.1   |          | Supply                                 | 3-1<br>3-1        |

|       | 3.2   |          | boardS-100 Bus Termination             |                   |

| IV.   | Appe  | ndix     |                                        |                   |

|       | S-10  | O Bus P  | Pin List                               | 4-1               |

#### LIST OF ILLUSTRATIONS

| Figure | Title                  | Page |

|--------|------------------------|------|

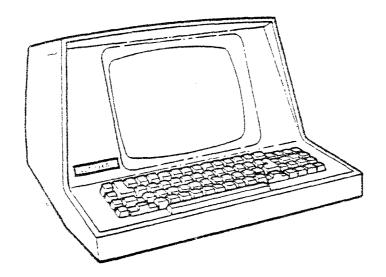

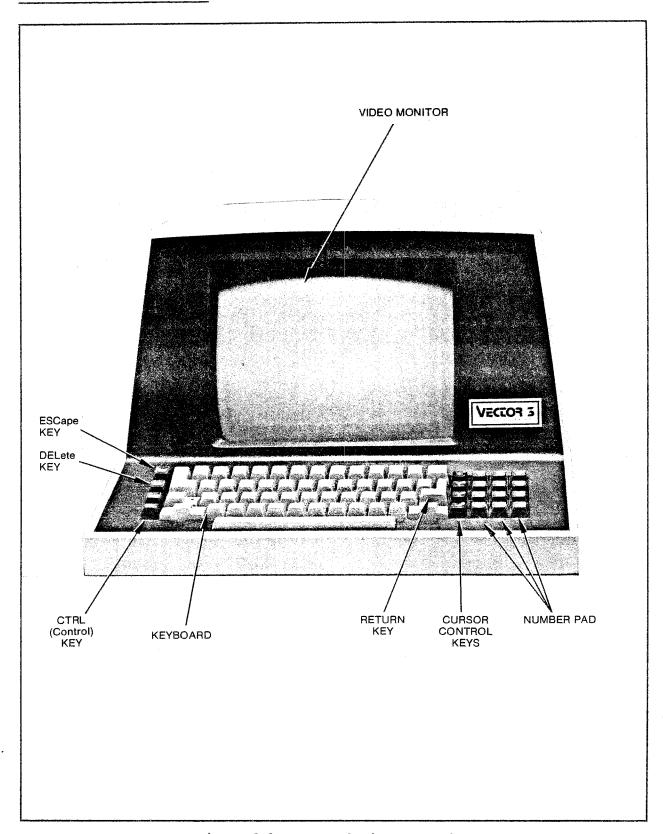

| 2-1    | Vector 3 Video Console | 1-2  |

| 3-1    | Vector 3 Mainframe     | 2-2  |

| 3-2    | Vector 3 Card Cage     | 3-2  |

# Hardware specifications

#### **POWER**

For one unit

220 VAC +/-10% Voltage option 115 VAC +/-10% Frequency 50 Hz +/-.5% 60 Hz +/-.5% Current, Operating 1.5 Amps 3 Amps Current, Surge Power Dissipation 7.5 Amps 15 Amps 350 Watts 350 Watts 1200 BTU 1200 BTU Heat Generation

#### VIDEO MONITOR

Screen Size 12-inch diagonal CRT

Resolution 850 lines at center (mean)

700 lines at borders (mean)

Bandwidth 16MHz +3dB

Video Interface Separate TTL video and sync

Compatibility of Compatible with Vector Graphic Flashwriter

Video I and II alphanumeric video display

boards and most other alphanumeric

video display boards

Not compatible with Vector Graphic High Resolution Graphics Board

External Controls Contrast

Internal Controls

Vertical hold

Vertical height

Vertical linearity

Vertical Centering

Focus Brightness

Horizontal Centering

#### KEYBOARD

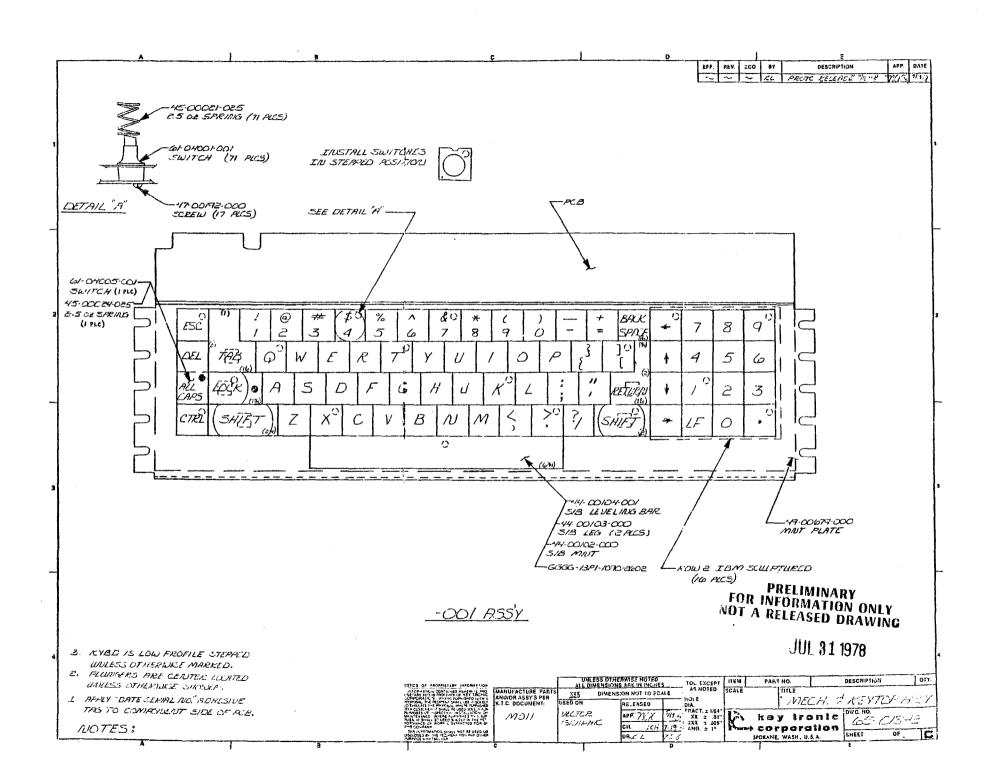

Keyboard Custom 60 keys, typwriter format, 12-key numeric pad, ESC, DEL, ALL CAPS

CTRL, LF, and cursor movement keys

Keyboard Electronics Capacitance key switches and LSI N-channel

MOS encoding electronics

# DIMENSIONS AND WEIGHT

|         | Height    | Depth*    | Width     | Weight |

|---------|-----------|-----------|-----------|--------|

|         | inches/cm | inches/cm | inches/cm | lbs/kg |

| Console | 12.8/32.4 | 18/45.7   | 21/53.3   | 22/10  |

<sup>\*</sup> Dimensions do not include requirement for cabling, typically 4 in./10.2  $\mbox{cm}$

#### I. PERSPECTIVE

#### 1.1 Introduction

The Vector 3 is a general purpose, full featured microcomputer featuring a video console with a keyboard featuring a 10-key number pad; a chassis with a heavy duty power supply and a 6-slot, fully terminated S-100 motherboard housed entirely within the console cover. For the purpose of definition, a Vector 3 is a subassembly of several systems, specifically the System VIP, the System 2800, and the System 3030. While the Vector 3 is a complete microcomputer system, many of its components are already covered in other documents; see the list below for further references.

- 1) 64K Memory Board; documented in the 64K Memory Board Dynamic RAM User's Manual.

- 2) ZCB Single Board Computer; documented in the ZCB Single Board Computer User's Manual.

- 3) Flashwriter II Video Board; documented in the Flashwriter II User's Manual.

- 4) The disk controller board appropriate for your system will be discussed in your system overview manual.

This manual will fully discuss the following subsystems:

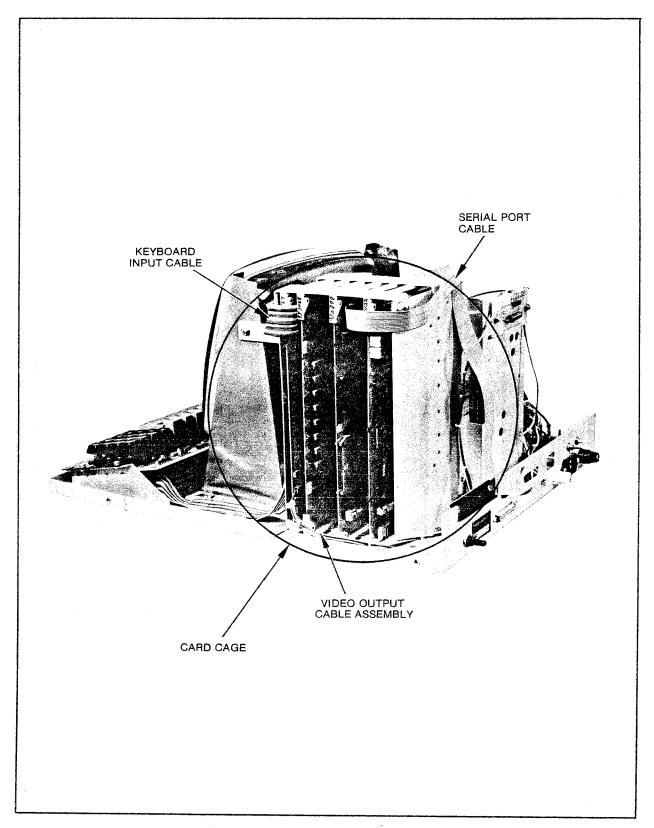

- 1) Keyboard and video monitor display (See Figure 2-1).

- 2) Power Supply (See Figure 3-1).

- 3) Shielded S-100 6-Slot Motherboard (See Figure 3-2).

Rev. A 8/18/80

#### II. VIDEO CONSOLE

#### 2.1 Video Monitor

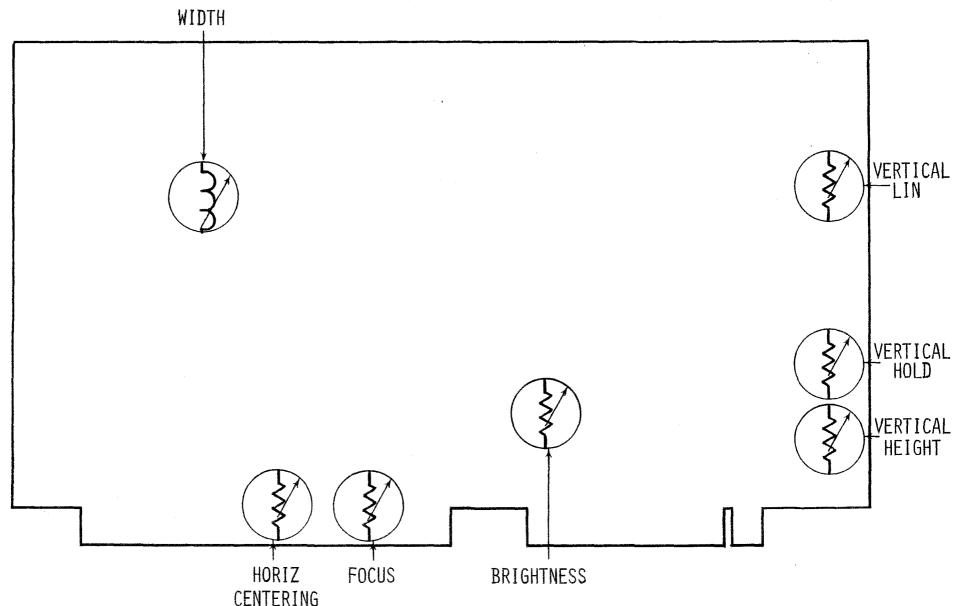

The video monitor (CRT) portion of the Vector 3 (See Figure 2-1) has up to 850 lines resolution and 16MHz bandwidth. All elements of display are adjustable. Adjustment procedures are found later in this manual.

The CRT monitor portion of the Vector 3 requires that the Video information be provided at TTL levels as separate video horizontal sync and vertical sync. This is provided by the Vector Graphic Flashwriter video boards.

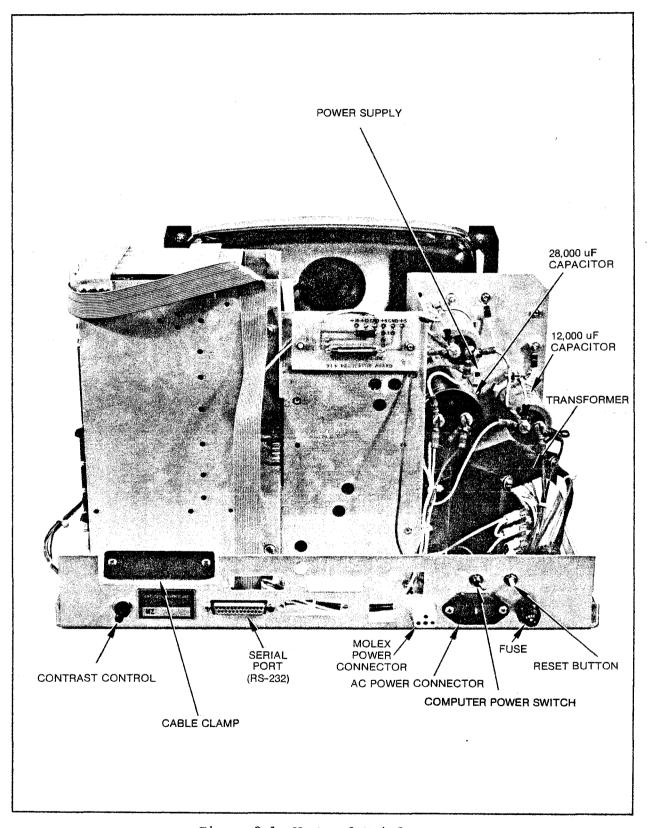

Operation of the video monitor (CRT) is very straightforward. The power to the monitor is provided by the computer power supply and is thus switched on and off by the computer power switch located on the rear panel of the console mainframe (See Figure 3-1).

Every video monitor comes supplied with a special glare reduced screen to eliminate annoying reflections and glare.

#### 2.1.1 External Controls

The only external control pertaining to the video monitor is the contrast control located on the rear panel of the console chassis (See Figure 3-1).

#### 2.1.2 Adjusting Procedures for Video Monitor.

Normally, no adjustment of the monitor screen should be required as it is adjusted at the factory. However, if adjustment is required for any reason, the following explanation of the functions of the various adjustments is provided. All the adjustments except the last two must be made inside the console, requiring you to unscrew and remove the shell.

A display which can be used to check adjustment is obtained by depressing the reset button (See Figure 3-1) on the rear of the console to call up the Monitor Executive then by typing Z F000 F7FF 38.

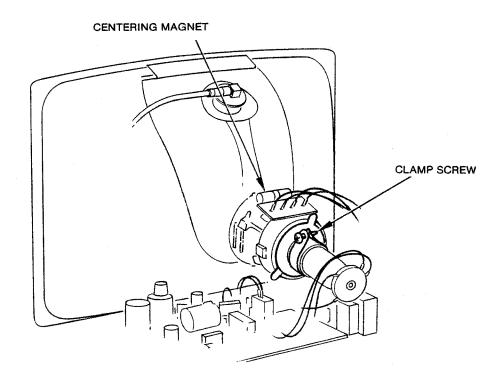

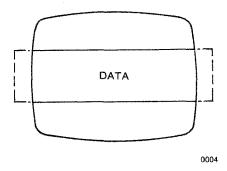

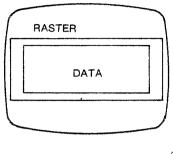

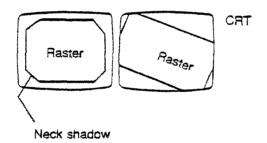

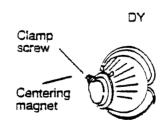

1. If the deflection yoke is not firmly against the bell of the tube, shadows will be caused at the corners of the display as shown below. If the yoke is slightly twisted, the display will also be twisted.

0001

0002

Figure 2-1 Vector 3 Video Console

Rev. A 8/18/80 2-2

Adjustment for this is made by first loosening the clamp screw holding the yoke and positioning it properly.

#### WARNING

DO NOT TOUCH ANY OF THE ELECTRICAL TERMINALS ON THE TUBE OR YOKE, AS HIGH VOLTAGES ARE PRESENT.

0011

2. If the width of the display is improper, adjust the core of the width coil (L102) on the P.C. board.

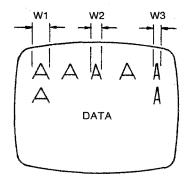

3. When data linearity in the horizontal direction is not good,

0003

turn the core of the horizontal linearity coil (L103) so that W1=W2=W3.

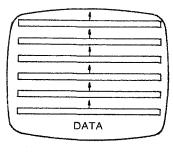

4. When the data runs in the vertical direction,

0005

turn the V. Hold pot with a screwdriver and stop data display.

Rev. A 8/18/80

5. When the vertical size (height) of data is not proper,

0006

turn the Height pot (VR102) with a screwdriver to adjust the height as required.

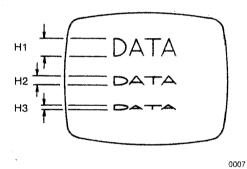

6. When vertical linearity of data is not good,

turn the V. LIN pot (VR103) with a screwdriver so that H1=H2=H3.

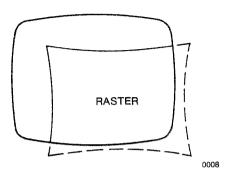

#### 7. Raster deviation:

Turn the two centering magnets so that the raster is centered in the vertical direction.

- 8. When data is not focused satisfactorily, turn the FOCUS pot (VR105) with a screwdriver so that focusing of the entire picture is optimum.

- 9. The correct adjustment of the Brightness pot (VR104) is when the background raster is just barely extinguished (black). If you can see faint lines zig-zagging across the screen in the background, turn the brightness down.

- 10. The contrast pot on the rear of the chassis should then be set to the minimum consistent with good legibility of the display. This will depend on the ambient light level and personal preference.

- 11. The horizontal position is controlled by both the video CENT (AlO3) control and also the position control on the upper left hand corner of the Flashwriter board. The latter is the preferred adjustment.

#### 2.1.3 Cables

Standard cables provided with the Vector 3 are the Flashwriter II cables, Keyboard cable, and Line cord.

#### 2.1.3.1 Cable Routing

See <u>figure 3-1</u> and <u>figure 3-2</u> for an illustration of proper cable routing. Instructions for cable routing are as follows:

- 1) Cable from keyboard (See Figure 3-2) should be attached to Jl of the Flashwriter board.

- 2) Cable from Video Monitor Interface Board (See Figure 3-2) should be attached to the 6-pin molex connector on Flashwriter II board (smooth side out).

Rev. A 8/18/80 2-6

- 3) Disk controller cable will be attached to disk controller board. See disk controller board manual for details.

- 4) A serial interface cable (See Figure 3-2) may be connected to the 16-pin output connector on the ZCB board.

- 5) If the system is equipped with a printer, a small printed circuit board may be installed on the twin parallel port connector on the ZCB board.

- 6) If the System is equipped with a Bitstreamer board, other cables may be present.

The following information is provided to inform users about the operation of the monitor. The "Interface Board" refers to the small PC board at the rear and inside the Video Monitor.

# INTERCONNECT CABLE - VIDEO MONITOR / INTERFACE BOARD

| SIGNAL    | MONITOR<br>10 PIN EDGE | WIRE COLOR | PIN<br>DESTINATION                     |

|-----------|------------------------|------------|----------------------------------------|

| HORZ GND  | 1                      | WHITE      | P2 Flash II Bd and<br>contrast control |

| H SYNC    | 6                      | PURPLE     | P3 FLASH II Bd                         |

| V SYNC    | 7                      | GREEN      | +12VDC                                 |

| VIDEO     | 8                      | BLUE       | Center tap-<br>contrast control        |

| V SYNC    | 9                      | RED        | P4 FLASH II Bd                         |

| VIDEO GND | 10                     | WHITE      | GND                                    |

# INTERCONNECT CABLE - KEYBOARD / FLASHWRITER BOARD

| Flashwriter board<br>24 PIN DIP-Jl | SIGNAL | KEYBOARD<br>DUAL TEN PIN EDGE |

|------------------------------------|--------|-------------------------------|

| 7                                  | DATA1  | 4                             |

| 8                                  | DATA3  | 2                             |

| 9                                  | -V REG | 10                            |

| 12                                 | STROBE | E                             |

| 13                                 | GND    | C,D                           |

| 14                                 | DATA4  | 1                             |

| 15                                 | DATA6  | 7                             |

| 16                                 | DATA 7 | 6                             |

| 17                                 | DATA2  | 3                             |

| 19                                 | DATA8  | 5                             |

| 20                                 | DATA5  | 8                             |

| 24                                 | Vcc    | 9                             |

Rev. A 8/18/80 2-8

# 2.2 Keyboard

The keyboard (See figure 2-1) provided with the Vector 3 is a standard typewriter keyboard with a 10 key number pad.

#### 2.2.1 Keyboard Connection

The keyboard is connected to the Flashwriter II board by a 24-pin dip plug (See Figure 3-2) to socket Jl near the lower right-hand corner of the board (side facing rear of chassis).

#### NOTE:

If the keyboard fails, check connector at both ends of the keyboard cable.

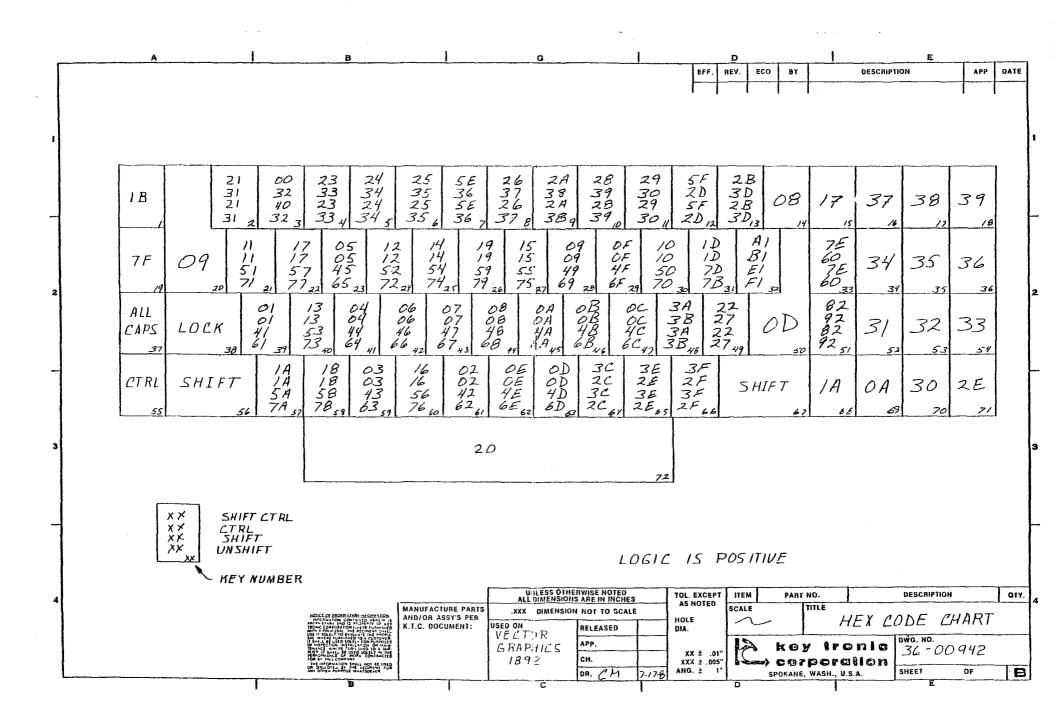

#### 2.2.2 Keyboard Code Conversion

Due to limitations in the keyboard encoder chip, it was not possible to provide several codes, in particular, those for the following characters:

[ (5B)

] (5D)

® (5C)

™ (7E)

The conversion can be done in software, as the [] key generates unique codes for the four modes: unshifted, shifted, control, control shift. This conversion is done in the Version 4.X Monitor PROM, which is the companion PROM for this keyboard. Furthermore this PROM version accepts the codes generated by the cursor control keys.

#### III. MAINFRAME

The Vector 3 Mainframe (See Figure 3-1) contains a CRT (Video) monitor, a power supply, and a 6-slot motherboard (See Figure 3-2). The on-off switch and the reset button are also located on the rear panel of the mainframe (See Figure 3-1).

#### 3.1 Power Supply

The Vector 3 power supply (See Figure 3-1) consists of two 12,000 uF Computer Grade capacitors, a 28,000 uF Computer Grade capacitor, and a 110V/220V Switchable Transformer.

#### 3.1.1 Troubleshooting

This section is provided for reference. The chassis has been completely tested at the factory.

#### WARNING

THIS POWER SUPPLY USES 110V AC, WHICH IS A POTENTIALLY LETHAL VOLTAGE LEVEL. EXTREME CAUTION MUST BE EXERCISED WHEN WORKING WITH THESE CIRCUITS WHEN POWER IS APPLIED. IT IS SUGGESTED THAT THE USER ALWAYS KEEP ONE HAND IN HIS POCKET WHILE WORKING ON THE POWER SUPPLY. NEVER MAKE OHMMETER OR CONTINUITY MEASUREMENTS WHILE POWER IS APPLIED.

#### 3.1.1.1 Preliminary Checkout (Without Power)

#### WARNING

#### DO NOT APPLY POWER DURING THESE TESTS AS HIGH VOLTAGES ARE PRESENT

Review schematic diagram and drawing (Figure 3-1) to ensure that the power supply is wired correctly. Check all connectors for mechanical integrity, such as the screw terminals on the electrolytic capacitors and the motherboard. A loose or unterminated wire can cause serious damage to the computer and present a safety hazard to the user.

Using an ohmmeter, check the continuity between the linecord receptacle ground terminal and the negative terminal of the 12,000 uF capacitor. Continuity (0 ohms) should be indicated between these points. Now measure from the capacitor to some bare metal portion of the chassis. Continuity should also be indicated here.

With the ohmmeter on the XI scale, measure across the 28,000 uF capacitor. If a short is indicated, reverse the leads of the ohmmeter and repeat the measurement. The correct indication of the ohmmeter will be a slowly increasing value of resistance (in the order of minutes) to a final value of infinity. If a short is indicated at both times, then either the capacitor is shorted or there is a wiring error.

Rev. A 8/18/80 3-1

Figure 3-1 Vector 3 Mainframe

For 110V: Jumper 1 to 3 and 2 to 4 For 220V: Jumper 2 to 3 only

Figure 3-2 Vector 3 Card Cage

Repeat the above test on each of the two  $12,000~\mathrm{uF}$  capacitors. The final value of resistance for these tests should be 820 ohms + 20%. Therefore, adjust the scale of the ohmmeter accordingly. The response time will be much shorter for these capacitors.

#### 3.1.1.2 Preliminary Checkout (With Power)

Before applying power to the computer, remove all plug-in circuit boards. Ensure that the fuse is installed and that the power switch is off. Connect the AC linecord and turn on the power switch. Listen for any crackling sounds or very loud buzzing in the transformer. Immediately disconnect power by unplugging the linecord if any unusual sounds are noted or if arcing is apparent.

Correct operation of the power supply shall be indicated by the fan running and both pilot lights on. With a voltmeter, check each of the power supply voltages. They should read as follows:

| NOMINAL VOLTAGE | ACCEPTABLE LIMITS |

|-----------------|-------------------|

| +8V             | +7.5 TO +11V      |

| +16V            | +15 TO +20V       |

| -16V            | -15 TO -20V       |

Any voltage reading out of the acceptable limits indicates a failure in that circuit. The most likely failures, after wiring errors have been eliminated, are defective diodes or transformers.

After the voltages have been tested at the power supply, carefully check for these voltages on the motherboard. They can be found on the following pins:

| BUS VOLTAGE | BUS PIN |

|-------------|---------|

| <b>V8+</b>  | 1, 51   |

| +16V        | 2       |

| -16V        | 52      |

| GROUND      | 50, 100 |

Incorrect reading here could damaage circuit boards when they are installed. If any wrong voltages are found, carefully check wiring to the motherboard.

Rev. A 8/18/80 3-5

#### 3.2 Motherboard

The Vector 3 Motherboard (See figure 3-2) has 6 slots, is based on the S-100 bus structure, and is designed to provide a number of features not previously available.

Vector Graphic motherboards are supplied with bus terminators. Not to be confused with so called "active" terminators, full-time termination is provided.

The Vector 3 motherboard has the following features.

- 1) Industry standard S-100 bus structure.

- 2) 0.75 center-to-center spacing between connectors.

- 3) Extra heavy 0.93" warp resistant G-10 epoxy board.

- 4) Full groundplane reduces noise on bus lines.

- 5) Traces on back of board only.

- 6) Less risk of shorts from conductive item being inadvertantly dropped during operation.

- 7) Reduced capacitance between traces.

- 8) Solder masked to reduce risk of solder bridges during assembly.

- 9) Bus termination.

3-6

# 3.2.1 S-100 Bus Termination

The terminators provided are 220 ohm pull-up (to +5V) and 330 ohm pull-down (to GND).

# TABLE 1 LINES TERMINATED

| 04 00      | 20 204           | CO 15 77 777    | 20               |

|------------|------------------|-----------------|------------------|

| 24 - 02    | 38 <b>-</b> DO4  | 68 - MWRITE     | 88 <b>-</b> DO2  |

| 25 - 01    | 39 <b>-</b> 1005 | 76 - PSYNC      | 89 <b>–</b> DO3  |

| 26 - PHLDA | 40 - DO6         | 77 <b>-</b> PWR | 90 <b>-</b> 1007 |

| 27 - PWAIT | 41 - D12         | 78 - PDBIN      | 91 - D14         |

| 29 - A5    | 42 - Dl3         | 79 <b>–</b> A0  | 92 - D15         |

| 30 - A4    | 43 - D17         | 80 - Al         | 93 - D16         |

| 31 - A3    | 44 - SML         | 81 - A2         | 94 - Dll         |

| 32 - A15   | 45 - SOUT        | 82 - A6         | 95 <b>-</b> D10  |

| 33 - Al2   | 46 - SINP        | 83 <b>–</b> A7  | 96 - SINTA       |

| 34 - A9    | 47 - SMEMR       | 84 - A8         | 97 <b>-</b> SWO  |

| 35 - DO1   | 48 - SHLTA       | 85 <b>-</b> Al3 |                  |

| 36 - DOO   | 49 - CLK         | 86 - Al4        |                  |

| 37 - AlO   | 58 - SXTRQ       | 87 <b>-</b> All |                  |

Rev. A 8/18/80

# IV APPENDIX

# S-100 Bus Pin List

| PIN NO.  | SIGNAL & TYPE                  | ACTIVE LE | VEL    | DESCRIPTION                                                                                                                               |

|----------|--------------------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | +8 VOLTS (B)                   |           |        | Instantaneous minimum greater than 7 volts, instantaneous maximum less than 25 volts, average maximum less than 11 volts.                 |

| 2        | +16 VOLTS (B)                  |           |        | Instantaneous minimum greater than 14.5 volts, instantaneous maximum less than 35 volts, average maximum less than 21.5 volts.            |

| 3        | XRDY (S)                       | H         | •      | One of two ready inputs to the current bus master. The bus is ready whe both these ready inputs are true. See pin 72.                     |

| 4        | V10*(S)                        | L         | G.C.   | Vectored interrupt line 0.                                                                                                                |

| 5        | V11*(S)                        | L         | 0.C.   | Vectored interrupt line 1.                                                                                                                |

| 6        | VI2*(S)                        | L         | 0.C.   | Vectored interrupt line 2.                                                                                                                |

| 7        | VI3*(S)                        | Ļ         | 0.C.   | Vectored interrupt line 3.                                                                                                                |

| 8        | VI4*(S)                        | Ļ         | 0.C.   | Vectored interrupt line 4.                                                                                                                |

| 9        | VI5*(S)                        | L         | O.C.   | Vectored interrupt line 5.                                                                                                                |

| 10       | VI6*(S)                        | L         | 0.C.   | Vectored interrupt line 6.                                                                                                                |

| 11       | VI7*(S)                        | L         | 0.C.   | Vectored interrupt line 7.                                                                                                                |

| 12<br>13 | NMI*(S)                        | L         | Q.C.   | Non-maskable interrupt.                                                                                                                   |

| 14       |                                |           |        |                                                                                                                                           |

| 15       | A18 (M)                        | H         |        | Extended address bit 18.                                                                                                                  |

| 16       | A16 (M)                        | Н         |        | Extended address bit 16.                                                                                                                  |

| 17       | A17 (M)                        | H         |        | Extended address bit 17.                                                                                                                  |

| 8        | SDSB* (M)                      | Ļ         | 0.C.   | The control signal to disable the 8 status signals.                                                                                       |

| 9        | CDSB* (M)                      | L         | O.C.   | The control signal to disable the 5 control output signals.                                                                               |

| 20       | GND (B)                        |           |        | Common with pin 100.                                                                                                                      |

| 21       | NDEF                           |           |        | Not to be defined. Manufacturer must specify any use in detail.                                                                           |

| 22       | ADSB* (M)                      | Ļ         | O.C.   | The control signal to disable the 16 address signals.                                                                                     |

| 23       | DODSB* (M)                     | L         | · 0.C. | The control signal to disable the 8 data output signals.                                                                                  |

| 24       | Ф (B)                          | H         |        | The master timing signal for the bus.                                                                                                     |

| 25       | pSTVAL*(M)                     | Ļ         |        | Status valid strobe.                                                                                                                      |

| 26       | pHLDA (M)                      | Н         |        | A control signal used in conjunction with HOLD* to coordinate bus master transfer operations.                                             |

| 27       | RFU                            |           |        | Reserved for future use.                                                                                                                  |

| 28       | RFU                            |           |        | Reserved for future use.                                                                                                                  |

| 29       | A5 (M)                         | H         |        | Address bit 5.                                                                                                                            |

| 30       | A4 (M)                         | H         |        | Address bit 4.                                                                                                                            |

| 31<br>32 | A3 (M)                         | H         |        | Address bit 3.                                                                                                                            |

| 33       | A15 (M)                        | H         |        | Address bit 15 (most significant for non-extended addressing.)                                                                            |

| 34       | A12 (M)                        | H         |        | Address bit 12.                                                                                                                           |

| 35       | A9 (M)                         | H         |        | Address bit 9.                                                                                                                            |

| 36       | DO1 (M)/DATA1 (M/S)            | H         |        | Data out bit 1. bidirectional data bit 1.                                                                                                 |

| 37       | DOO (M)/DATAO (M/S)            | п<br>Н    |        | Data out bit 0, bidirectional data bit 0.                                                                                                 |

| 38       | A10 (M)<br>D04 (M)/DATA4 (M/S) | H         |        | Address bit 10.                                                                                                                           |

| 39       | DOS (M)/DATAS (M/S)            | H         |        | Data out bit 4, bidirectional data bit 4.  Data out bit 5, bidirectional data bit 5.                                                      |

| 10       | DOG (M)/DATAG (M/S)            | H         |        | Data out bit 6, bidirectional data bit 6.                                                                                                 |

| 11       | DI2 (S)/DATA10 (M/S)           | H         |        | Data in bit 2, bidirectional data bit 10.                                                                                                 |

| 2        | DI3 (S)/DATA11 (M/S)           | H         |        | Data in bit 3, bidirectional data bit 11.                                                                                                 |

| 13       | DI7 (S)/DATA15 (M/S)           | H         |        | Data in bit 7, bidirectional data bit 15.                                                                                                 |

| 14       | sM1 (M)                        | н         |        | The status signal which indicates that the current cycle is an on-code fetch.                                                             |

| 15       | sOUT (M)                       | Н.,       |        | The status signal identifying the data transfer bus cycle to an output device.                                                            |

| 16       | SINP (M)                       | н         |        | The status signal identifying the data transfer bus cycle from an input device.                                                           |

| 17       | SMEMR (M)                      | H         |        | The status signal identifying bus cycles which transfer data from memory to a bus master, which are not interrupt acknowledge instruction |

| 8.       | sHLTA (M)                      | н         |        | fetch cycle(s).  The status signal which acknowledges that a HLT instruction has been executed.                                           |

| 19       | CLOCK(B)                       |           |        | 2 MHz (0.5%) 40-60% duty cycle. Not required to be synchronous with<br>any other bus signal.                                              |

| 0        | GND (B)                        |           |        | Common with pin 100.                                                                                                                      |

| 1        | +8 VOLTS (B)                   |           |        | Common with pin 1.                                                                                                                        |

| 2        | -16 VOLTS (B)                  |           |        | Instantaneous maximum less than -14.5 volts, instantaneous minimum greater than -35 volts, average minimum greater than -21.5 volts.      |

| 53<br>54 | GND (B)                        | •         |        | Common with pin 100.                                                                                                                      |

|          | ·_ •                           |           |        | _ • • • · · · · · · · · · · · · · · · ·                                                                                                   |

| PIN NO.    | SIGNAL & TYPE        | ACTIVE LE | VEL  | DESCRIPTION                                                                                                                     |

|------------|----------------------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------|

| 56         |                      |           |      |                                                                                                                                 |

| 57         |                      |           |      |                                                                                                                                 |

| 58         | sXTRQ* (M)           | L         |      | The status signal which requests 16-bit slaves to assert SIXTN*.                                                                |

| 59         | A19 (M)              | Ĥ         |      | Extended address bit 19.                                                                                                        |

| 60         | SIXTN* (S)           | Ë         | Q.C. | The signal generated by 16-bit slaves in response to the 16-bit request                                                         |

| 00         | CIATIN (C)           | -         | u    | signal sXTRQ*.                                                                                                                  |

| 61         | A20 (M)              | Н         |      | Extended address bit 20.                                                                                                        |

| 62         | A21 (M)              | H         |      | Extended address bit 21.                                                                                                        |

| 63         | A22 (M)              | • й       |      | Extended address bit 22.                                                                                                        |

| 64         | A23 (M)              | H         | •    | Extended address bit 23.                                                                                                        |

| 65         | NDEF                 |           |      | Not to be defined signal.                                                                                                       |

| 66         | NDEF                 |           |      | Not to be defined signal.                                                                                                       |

| 67         | PHANTOM* (M/S)       | L         | 0.C. | A bus signal which disables normal slave devices and enables phantom                                                            |

| <b>.</b> . | (Indicate (indicate) | •         |      | slaves—primarily used for bootstrapping systems without hardware front panels.                                                  |

| 68         | MWRT (B)             | н         |      | pWR - sOUT (logic equation). This signal must follow pWR by not mo                                                              |

|            | CALCALIST CONT.      | "         |      | than 30 ns. (See note, Section 2.7.5.3)                                                                                         |

| 69         | RFU                  |           |      | Reserved for future use.                                                                                                        |

| 70         | GND (B)              |           |      | Common with pin 100.                                                                                                            |

| 71         | RFU .                |           |      | Reserved for future use.                                                                                                        |

| 72         | RDY (S)              | H         | 0.C. | See comments for pin 3.                                                                                                         |

| 73         | INT* (S)             | Ë         | 0.C. | The primary interrupt request bus signal.                                                                                       |

| 74         | HOLD* (M)            | Ī         | 0.C. | The control signal used in conjunction with pHLDA to coordinate bus                                                             |

| 1 7        | (m)                  |           | U.U. | master transfer operations.                                                                                                     |

| 76         | 0000000              | / t       | 0.0  | <u> </u>                                                                                                                        |

| 75         | RESET*(B)            | ′ L       | O.C. | The reset signal to reset bus master devices. This signal must be active with POC* and may also be generated by external means. |

| 76         | ACVING (M)           | ы         |      | external means.                                                                                                                 |

| 76<br>77   | psync (M)            | H         |      | The control signal significing the processes of                                                                                 |

| "          | pWR* (M)             | L         |      | The control signal signifying the presence of                                                                                   |

| 78         | -DOIN (M) :          | . 14      |      | valid data on 00 bus or data bus.                                                                                               |

| <i>,</i> 0 | pDBIN (M)            | Н         |      | The control signal that requests data on the Di                                                                                 |

| 79         | 40 (14)              |           |      | bus or data bus from the currently addressed slave.                                                                             |

|            | A0 (M)               | H         |      | Address bit 0 (least significant).                                                                                              |

| 30<br>31   | A1 (M)               | H         |      | Address bit 1.                                                                                                                  |

| 31         | A2 (M)               | H         |      | Address bit 2.                                                                                                                  |

| 32         | A6 (M)               | H         |      | Address bit 6.                                                                                                                  |

| 83         | A7 (M)               | H         |      | Address bit 7.                                                                                                                  |

| 34         | A8 (M)               | Н         |      | Address bit 8.                                                                                                                  |

| 35         | A13 (M)              | н         |      | Address bit 13.                                                                                                                 |

| 36         | A14 (M)              | н         |      | Address bit 14.                                                                                                                 |

| 37         | A11 (M)              | н         |      | Address bit 11.                                                                                                                 |

| 38         | DO2 (M)/DATA2 (M/S)  | Н         |      | Data out bit 2, bidirectional data bit 2.                                                                                       |

| 39         | DO3 (M)/DATA3 (M/S)  | Н         |      | Data out bit 3, bidirectional data bit 3.                                                                                       |

| 90         | DO7 (M)/DATA7 (M/S)  | н         |      | Data out bit 7, bidirectional data bit 7.                                                                                       |

| 31         | DI4 (S)/DATA12 (M/S) | н         |      | Data in bit 4 and bidirectional data bit 12.                                                                                    |

| 32         | DIS (S)/DATA13 (M/S) | Н         |      | Data in bit 5 and bidirectional data bit 13.                                                                                    |

| 93         | DI6 (S)/DATA14 (M/S) | н         |      | Data in bit 6 and bidirectional data bit 14.                                                                                    |

| )4         | DI1 (S)/DATA9 (M/S)  | Н         |      | Data in bit 1 and bidirectional data bit 9.                                                                                     |

| 95         | DIO (S)/DATA8 (M/S)  | н .       |      | Data in bit 0 (least significant for 8-bit data) and bidirectional data bit 8.                                                  |

| 36         | sINTA (M)            | H         |      | The status signal identifying the bus input cycle(s) that may follow an accepted interrupt request presented on INT*.           |

|            | sWO* (M)             | L         |      | The status signal identifying a bus cycle which transfers data from a bus master to a slave.                                    |

| 8          |                      |           |      | See Interior to a staye.                                                                                                        |

| 99         | POC* (B)             | L         |      | The power-on clear signal for all bus devices; when this                                                                        |

| 100        | GND (B)              |           |      | signal goes low, it must stay low for at least 200 nanoseconds.  System ground.                                                 |

Rev. A 8/18/80 4-2

|  |  |  |  | 1 |

|--|--|--|--|---|

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  |   |

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  | l |

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  |   |

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  |   |

|  |  |  |  | ı |

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  | ı |

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  | 1 |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

|  |  |  |  |   |

| , |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

•

|  |   | ı |

|--|---|---|

|  |   | I |

|  |   | 1 |

|  |   | I |

|  |   |   |

|  |   | ı |

|  |   | 1 |

|  | , | 1 |

|  |   | 1 |

|  |   | 1 |

|  |   | 1 |

|  |   | 1 |

|  |   |   |

|  |   | l |

|  |   | l |

|  |   | 1 |

|  |   | I |

|  |   | 1 |

|  |   | 1 |

|  |   | ı |

|  |   |   |

|  |   | l |

|  |   |   |

|  |   | I |

|  |   | 1 |

|  |   |   |

|  |   | 1 |

|  |   | ı |

|  |   | l |

|  |   | 1 |

|  | · |  |  |

|--|---|--|--|

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

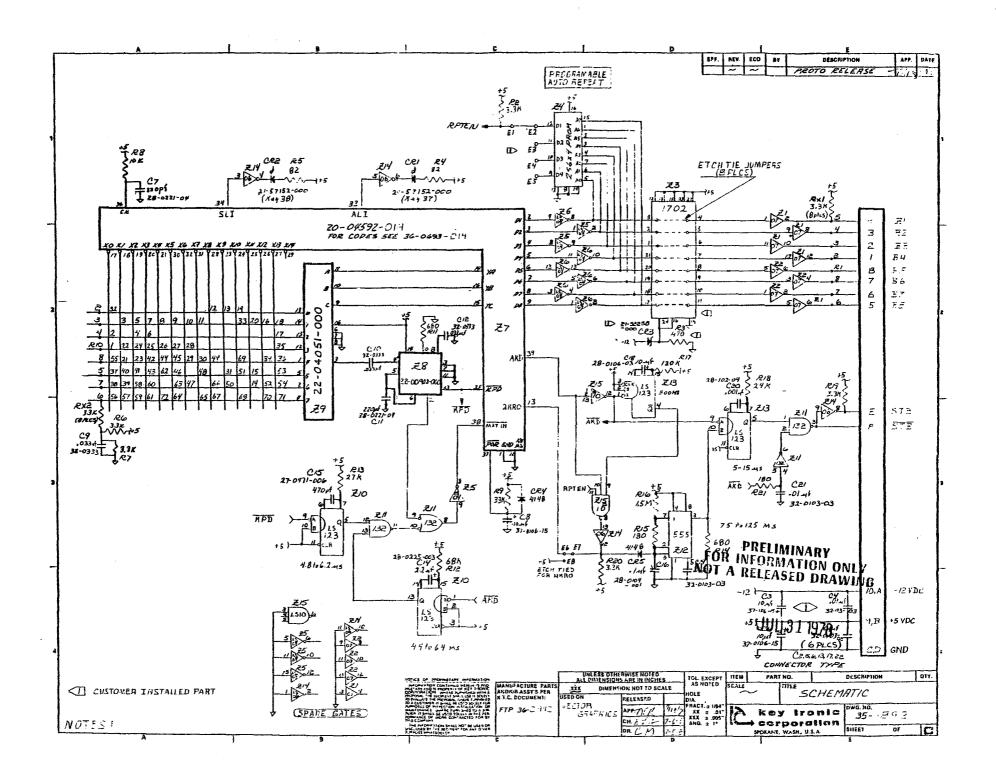

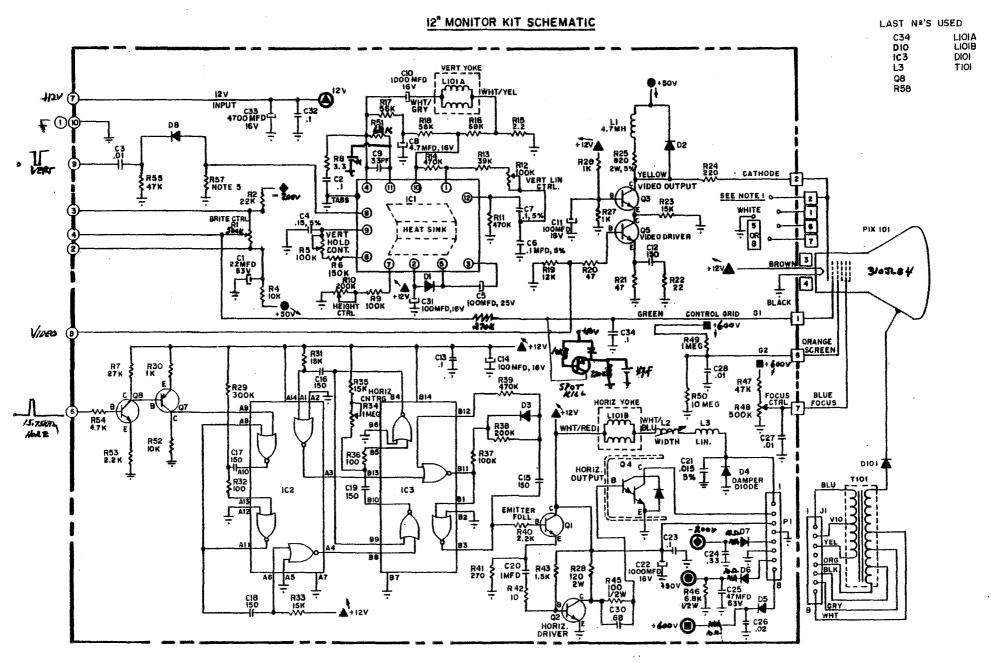

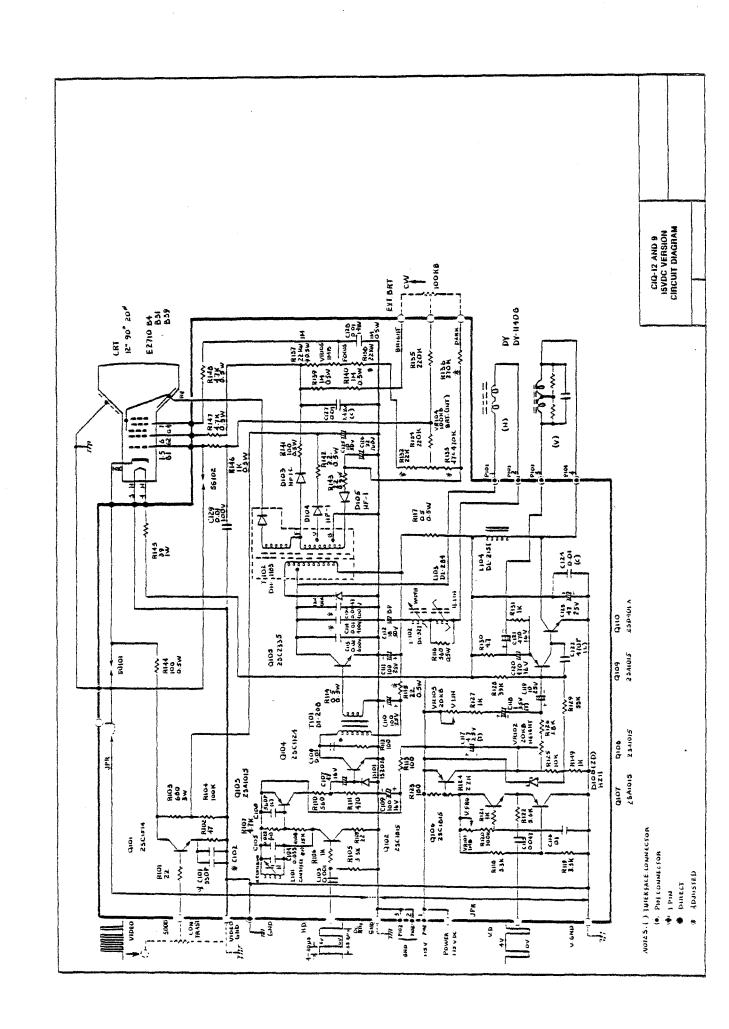

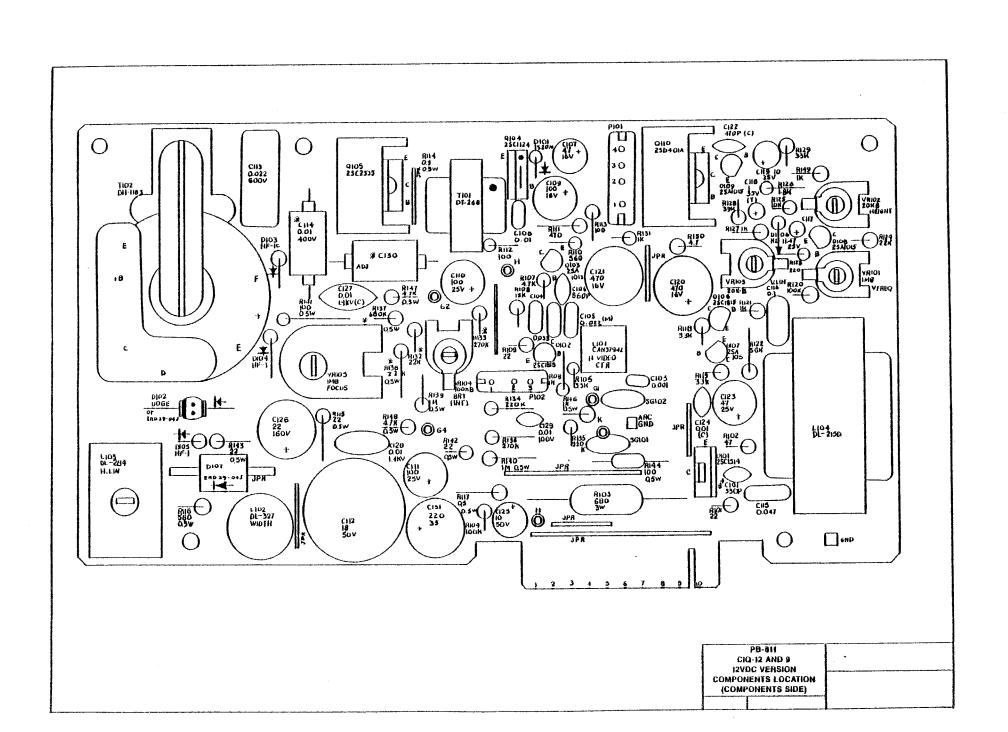

## Physical Position of Controls on P.C. Board

#### NOTES

- 1. PIN 5 OF PIX SOCKET IS GROUND, RETURN FOR SPARK GAPS TO PINS 1,2,6 AND 7.

- 2. SOURCE VOLTAGES. SYMBOL CIRCLED. ARROWS POINT TO SOURCE.

- 3. EDGE CONNECTOR NUMBERS INDICATED IN CIRCLES, PIX SOCKET PIN CONNECTIONS IM RECTANGLES,

- 5, R57 REQUIRED WITH TDAILTOS BUT NOT WITH TDAILTO.

- CAPACITANCE VALUES OF 1 OR LESS ARE IN MICROFARADS.

ABOVE 1 IN PICOFARADS, UNLESS OTHERWISE INDICATED.

Wells GARDNET SCHEMATIC FOR VECTOR SOMMES 12/3/80

# SPECIFICATIONS

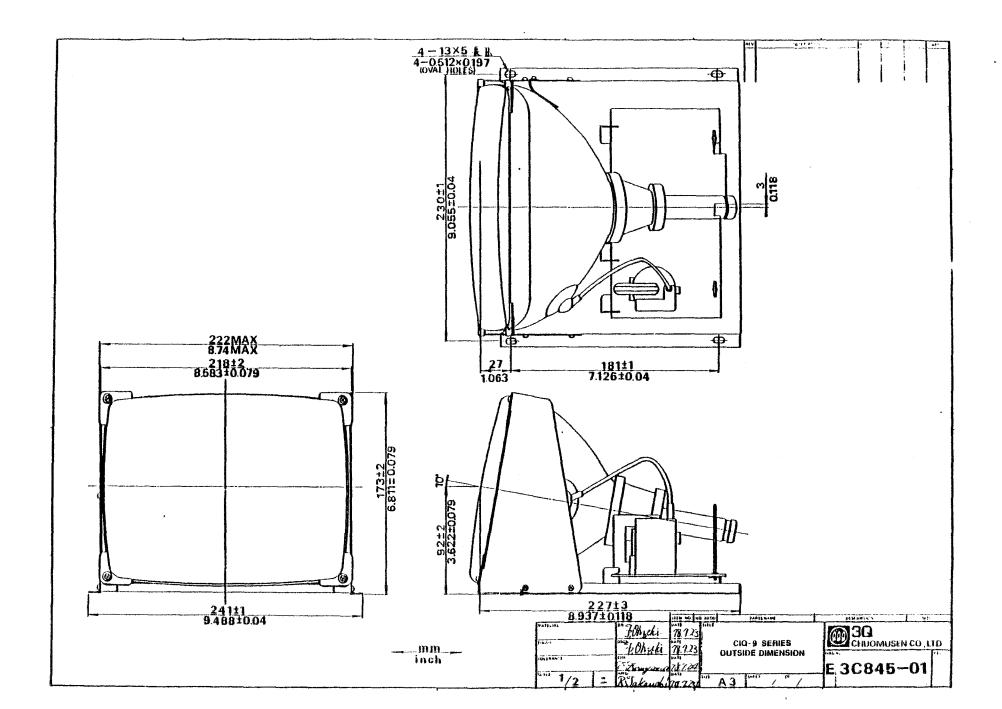

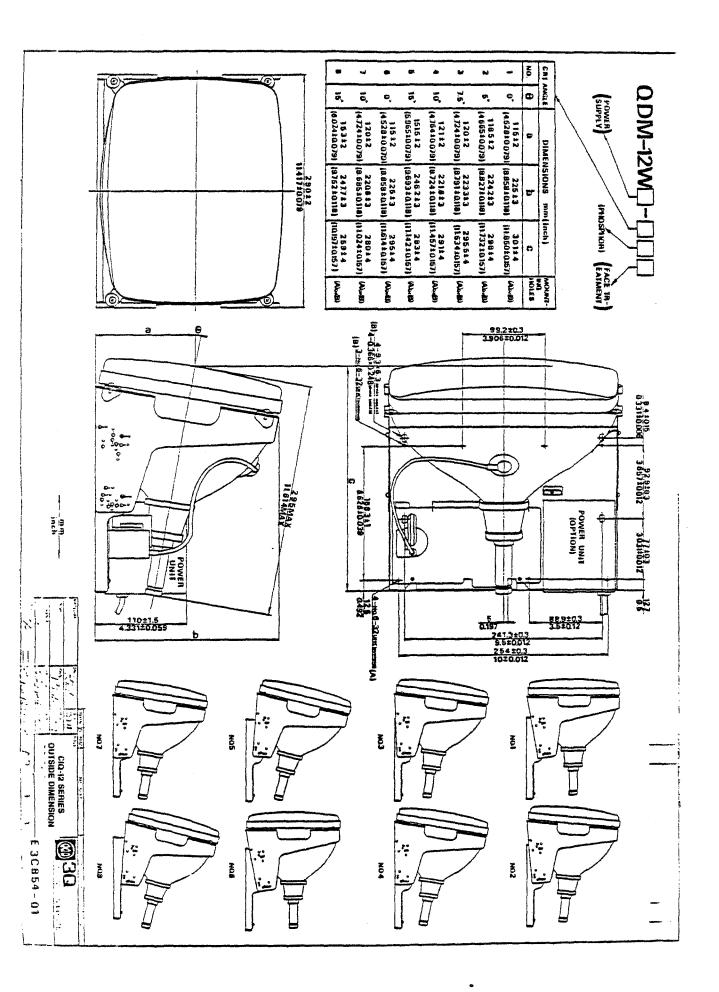

### MODEL CIQ-9 MODEL CIQ-12

# 9"and 12" CRT DISPLAY MONITOR

5301 Beethoven Street Los Angeles, Calif. 90066 Telephone: (213) 390-7778 Telex: (WU) 65-2451

280 Park Avenue, New York, NY 10017 Telephone: (212) 682-0420 Telex (WU) 12-5059

### **SPECIFICATIONS**

#### GENERAL

The Model CIQ-12 and CIQ-9 are a 12-inch and 9 inch CRT Display Unit is to be used as an alpha-numeric display device. The CRT will be scanned in conventional TV fashion.

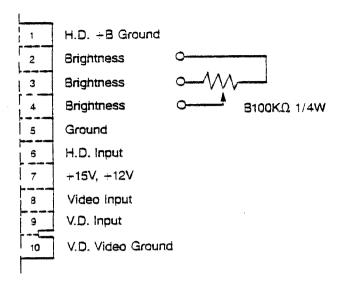

All input signal connections to the monitor will be via a single 10 pin card edge connector, and comprise:

Video

Horizontal Drive

Vertical Sync

#### RATING

|    | 110                                 | •                                                                                                                      |

|----|-------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 1. | Video Input                         | 4.0Vp-p = 1.5V positive going pulse                                                                                    |

| 2. | Video Input<br>Impedance            | More than 1 K $\Omega$                                                                                                 |

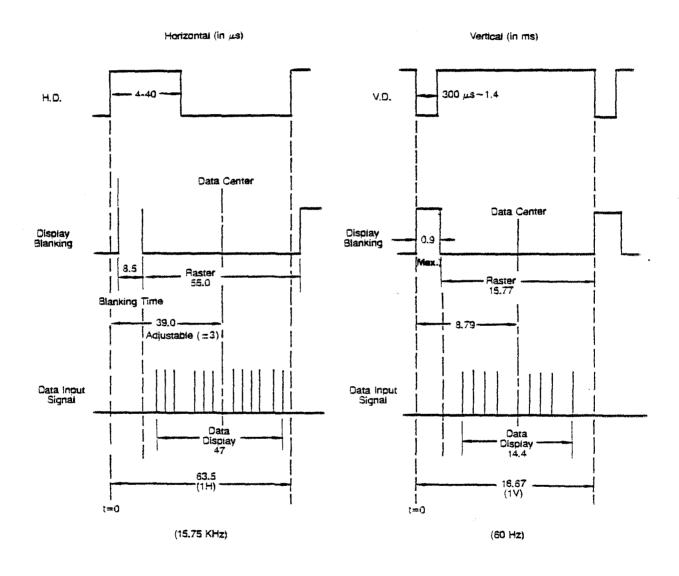

| 3. | Horizontal Drive                    | 4.0 Vp-p $\pm$ 1.5V positive going pulse Pulse width: 4 to 40 $\mu$ sec. Frequency: 15.75 KHz $\pm$ 500 Hz             |

| 4. | Horizontal Orive<br>Input Impedance | More than $470\Omega$                                                                                                  |

| 5. | Vertical Sync.                      | 4.0 Vp-p $\pm$ 1.5V negative going pulse Pulse width: 300 $\mu$ sec. to 1.4 msec. Frequency: 55 Hz $\pm$ 8 Hz          |

| 6. | Vertical Sync<br>Input Impedance    | More than $K\Omega$                                                                                                    |

| 7. | Signal Lavel                        | Low: 0 ± 0.4V<br>High: 4 ± 1.5V                                                                                        |

| 8. | Power Supply                        | DC +15V $\pm$ 0.2V (Less than 1.2A) or DC +12V $\pm$ 0.2V (Less than 1.5A) or AC 115/230V $\pm$ 10%, 50/60 Hz (Option) |

|    |                                     | Input connector for AC power supply (customer supplied).                                                               |

Housing: AMP1-480705-0 or equivalent Contact pin: AMP 350690-1 or equivalent

9. Ambient Temperature

0°C to 55°C (Operating)

-30°C to 65°C (Storage)

10. Humidity

10 to 90% (Non-condensing)

11. C.R.T.

12 and 9-inch, 90° deflection 20°

12. X-ray Radiation

Less than 0.5mR/H

13. Weight

CIQ-12.

Approx. 9.9 lbs (4.5 Kg) without AC power unit

AC power unit Approx. 3.3 lbs. (1.5 Kg)

CIQ-9

Approx. 6.2 lbs. (2.8 Kg)

14. Dimensions

Based on the drawing of External View.

15. Inside Controls

Sub-brightness

Horizontal Centering

Focusing Vertical Frequency

Horizontal Size Horizontal Linearity

Vertical Size

Vertical Linearity

16. Phosphor

P4 —Standard P31—Option P39—Option

#### CHARACTERISTICS

1. Video Band Width

16MHz = 3dB

2. Rise Time And

Fall Time

35 nsec or less (linear mode)

3. Storage Time

15 nsec or less (linear mode)

4. Horizontal Retrace

Time

Approx. 8.5 µsec.

5. Vertical Retrace

Time

0.9 msec, or less

6. Resolution

CIQ-12

Center: 850 TV lines (mean)

Corner: 700 TV lines (mean)

CIQ-9

Center: 800 TV lines (mean) Comer: 650 TV lines (mean)

7. Distortion and Linearity Offset

Within limit equivalent to 2% measured with EiA's ball chart (with PC board mounted according to manufacturer's specification)

8. SN Ratio

40dB or more (80% area of CRT screen)

9. MTBF

More than 20,000 H (without CRT)

10. Performance range

0°C to 40°C

#### 1. Connection of Connector

#### 2. Input Connector

#### Card edge connector

- Viking # 2VK10S/1-2

- Amphenol # 225-21031-101

- Cinch # 1-039-0119

- · Hirose # CR7E-20DA-3.96E

- Or Equivalent

Polarizing key shall be inserted between 9 pin and 10 pin.

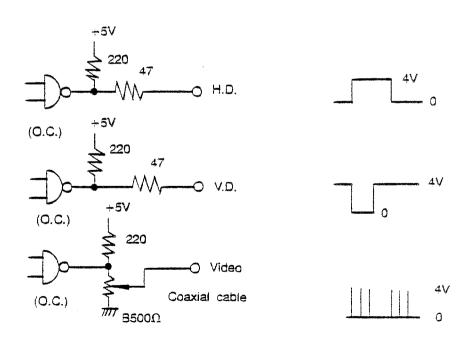

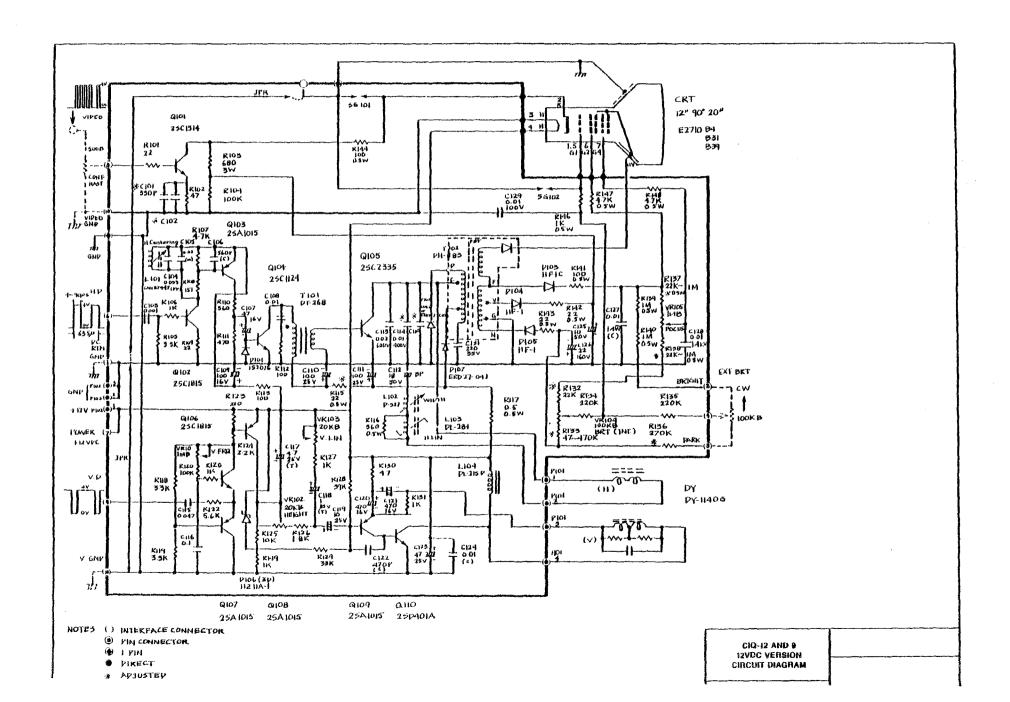

#### 3. C.P.U. Output Circuit

### TIMING CHART (Standard Type)

| ~ |  | ı      |

|---|--|--------|

|   |  | i<br>I |

|   |  | 1      |

|   |  | 1      |

|   |  | 1      |

|   |  | 1      |

|   |  | 1      |

|   |  | 1      |

|   |  | l<br>I |

|   |  | 1      |

|   |  | 1      |

|   |  | 1      |

|   |  | 1      |

|   |  | l<br>I |

|   |  | 1      |

|   |  | 1      |

|   |  | 1      |

|   |  | i.     |

|   |  | 1      |

|                                       | - |  |  |  |

|---------------------------------------|---|--|--|--|

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

| e e                                   |   |  |  |  |

| e e e e e e e e e e e e e e e e e e e |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|                                       |   |  |  |  |

|  | r |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

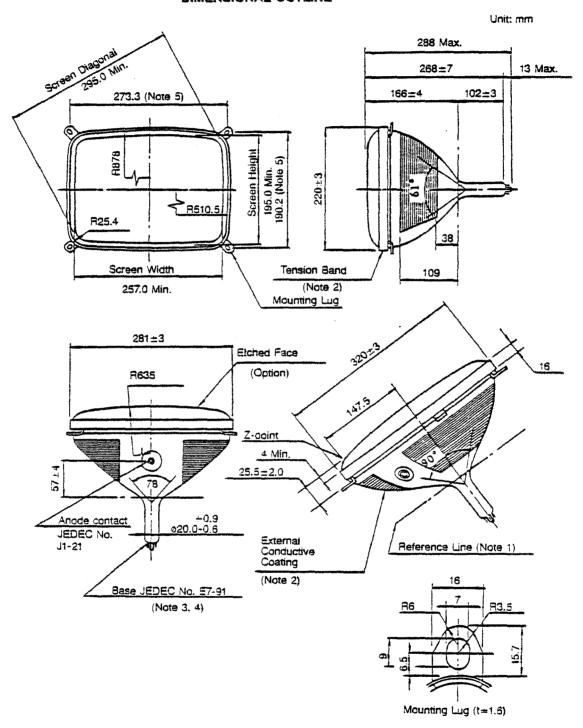

#### CIQ-12 CATHODE RAY TUBE DIMENSIONAL OUTLINE

#### NOTE FOR DIMENSIONAL OUTLINE

- 1. Reference line is determined by EIAJ G-R90J5 reference line gauge, when the reference line gauge is seated against the bulb.

- 2. External conductive coating and implosion protection hardware must be grounded.

- 3. The plane through the tube axis pin No. 5 may vary from the plane through the tube axis and anode contact by angular tolerance of ±30 degrees. Anode contact is on same side as pin No. 5.

- 4. Socket for this base should not be rigidly mounted. It should have flexible leads and be allowed to move freely.

- 5. The mounting bolts in the cabinet must be situated inside a circle of 4.5 mm (0.177 inch) diameter on the true geometrical positions.

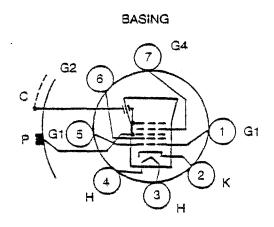

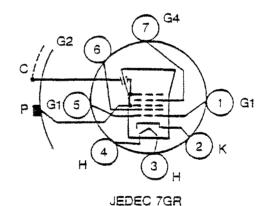

JEDEC No. 7GR

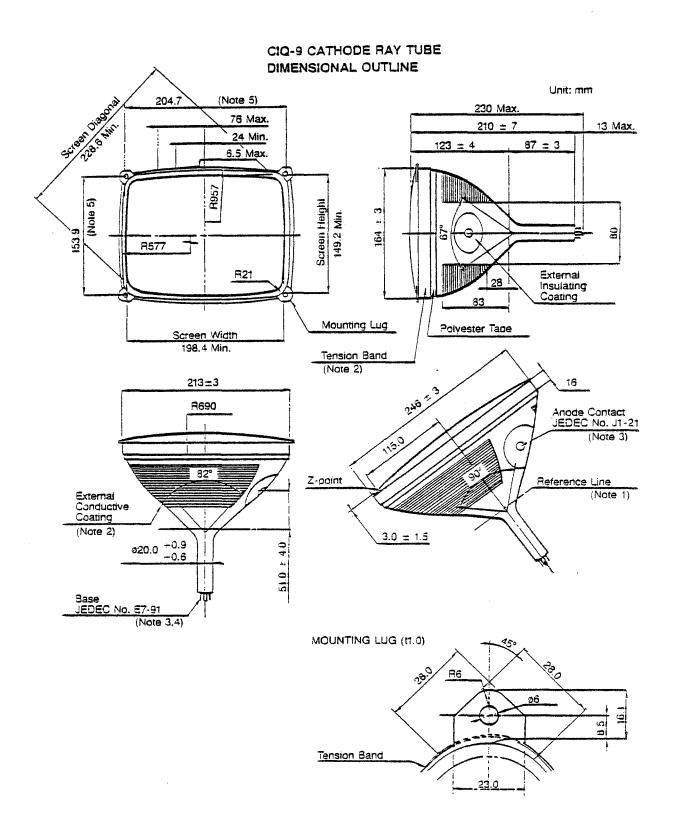

#### NOTE FOR DIMENSIONAL OUTLINE

- 1. Reference line is determined by EIAJ G-R90J3 reference line gauge, when the reference line gauge is seated against the bulb.

- 2. External conductive coating and implosion protection hardware must be grounded.

- 3. The plane through the tube axis pin No. 5 may vary from the plane through the tube axis and anode contact by angular to tolerance of  $\pm$  30 degrees. Anode contact is on same side as pin No. 5.

- 4. Socket for this base should not be rigidly mounted. It should have flexible leads and be allowed to move freely.

- 5. For the mounting bolt holes, a free space of 4.0 mm (0.157 inch) diameter is ensured around this nominal position.

#### SOCKET CONNECTION (BOTTOM VIEW)

#### INSPECTION/ADJUSTMENT PROCEDURE

- 1. Inspect the following items thoroughly upon arrival for any physical damage:

- 1) Metal works (bent, loose, and/or missing screws, etc.)

- 2) Printed circuit board (crack, fracture, etc.)

- 3) Discrete components (crack, poor soldering, etc.)

- 4) Wiring (broken lead, poor soldering, damaged insulation, etc.)

- 5) illegible label

#### 2. Raster Check and Adjustment Procedure

- 1) Apply HD and VD signal to the input terminal (No. 6 and 9 respectively) of the circuit board. Ref. P3-1

- 2) Apply 15VDC or 12VDC to the input terminal No. 7 of the circuit board. Raster will appear in 15 seconds or so

- 3) Check tilting of the raster.

Loosen DY clamp screw, and correct tilted raster or neck shadow. Tighten clamp screw, and fix it with paint lock.

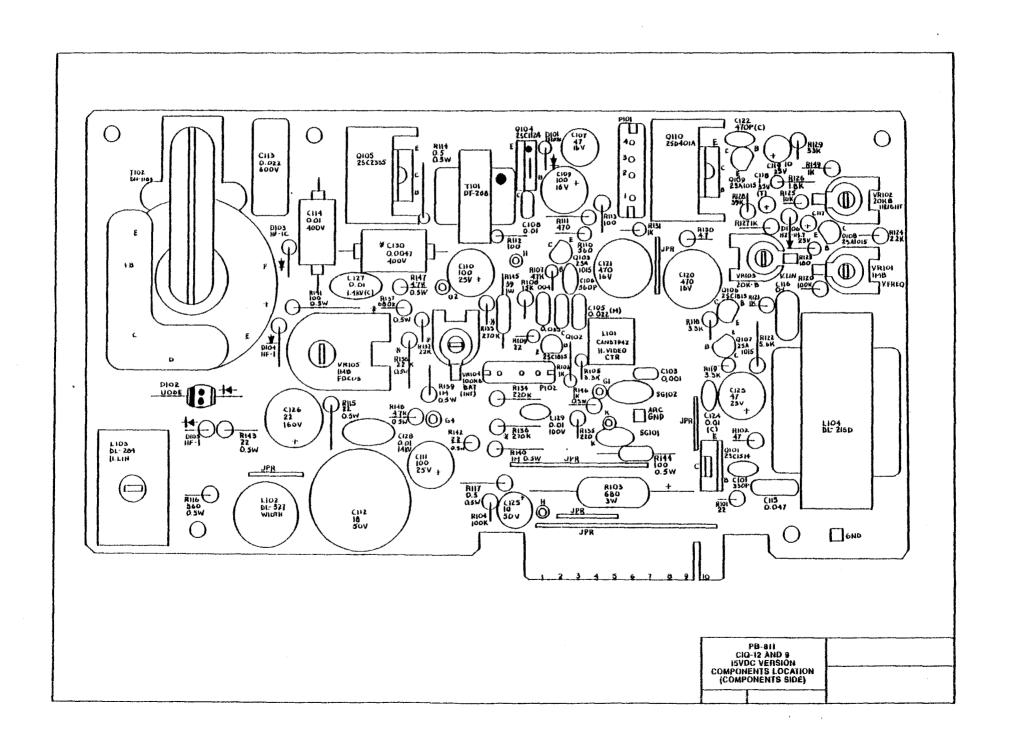

Internal Controls and Adjustments

Display Width-L102

Display Horizontal Centering-L101

Horizontal Linearity-L103

Vertical Hold-VR101

Vertical Height-VR102

Vertical Linearity-VR103

Focus-VR105

Sub-brightness-VR104

#### (SEE PC BOARD PARTS LAYOUT FOR LOCATION)

- 1) The brightness can be controlled by adjusting VR104. If EXT-BRT is utilized, set it to the center before Internal Brightness Control is adjusted.

- 2) Blurred display may not be caused by improper focus adjustment. High video signal will also create a blurred image. In this case, reduce video signal level by EXT-CONTRAST CONTROL.

#### 4. Shock Test

Lift one side of the unit about 2 inches off the surface and release. Observe whether or not the display is affected by the shock; if the unit is affected, check for loose soldering, screws, etc.

#### 5. CRT Soot Test

One minute after the power is turned off, if the spot appears at the center of the CRT screen, it may be defective.

#### 6. Raster Deviation

Turn the two centering magnets until the raster is centered. Apply screw lock when correction is completed.

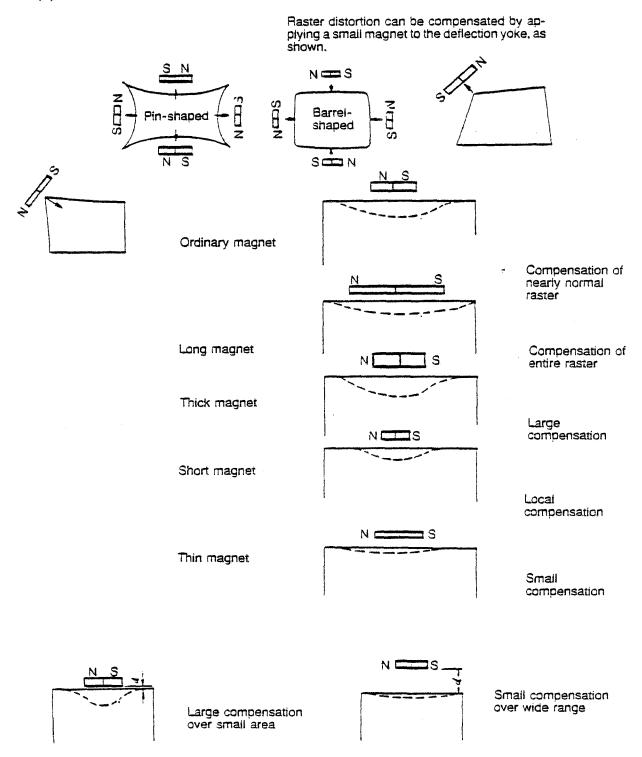

(6) Raster deviation

#### (7) Raster distortion

#### PART NUMBER CLASSIFICATION FOR CIQ SERIES CRT DISPLAY MONITOR

| cia - [                  | A B C D E F G H I J                                                                                                                                                                                 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                                                                                                                                                                                                     |

| A - 12:<br>09:<br>05:    | inches, diagonal measurement of CRT screen                                                                                                                                                          |

| B - C:<br>X:<br>U:<br>Z: | with chassis kit version universal chassis (settings for 0, 5, 7.5, 10, 15, -10, or -15 degree tilt positions) chassis per customer's requirement                                                   |

| C - Q:<br>P:<br>X:<br>Z: | chassis compatible with Ball TV-12 by physical measurement " " according to Ball drawing (Slight difference between drawing and actual measurement.) kit version chassis per customer's requirement |

| D -00, 05,<br>XX:        | 7.5, 10, 15: degree(s) tilt angle of CRT kit version                                                                                                                                                |

| E - D:<br>A:             | DC power AC power                                                                                                                                                                                   |

| F - 015:<br>012:<br>XXX: | 15 VDC<br>12 VDC<br>115/230 VAC                                                                                                                                                                     |

| G -C:<br>E:              | clear face (standard) etched face (non-glare)                                                                                                                                                       |

| H -04:<br>31:<br>39:     | P4 phosphor P31 phosphor P39 phosphor                                                                                                                                                               |

| 1 - (25-30):<br>(04-40)  | : Horizontal drive input, 25-30µs pulse width<br>: " " 4-40µs pulse width                                                                                                                           |

| J - S:<br>C:             | separate signal composite signal                                                                                                                                                                    |

#### **ASCII CODE CHART**

1968 ASCII: American Standard Code for Information Interchange, Standard No. X3.4-1968 of the American National Standards Institute.

|            | b <sub>7</sub> →                          | 0   | 0   | 0  | 0 | 1  | 1  | 1   | 1      |

|------------|-------------------------------------------|-----|-----|----|---|----|----|-----|--------|

| Bits       | $b_6 \longrightarrow b_5 \longrightarrow$ | 0   | 0   | 1  | 1 | 0  | 0  | 1 0 | 1      |

| 14 13 12 b | COLUMN ->                                 | 0   | 1   | 2  | 3 | 4  | 5  | 6   | 7      |

| 0000       | 0                                         | NUL | DLE | SP | 0 | @  | P  | 1   | P      |

| 0001       | 1                                         | SOH | DC1 | 1  | 1 | Α  | Q  | a   | 9      |

| 0010       | 2                                         | STX | DC2 | 11 | 2 | В  | R  | Ь   | r      |

| 0011       | 3                                         | ETX | DC3 | #  | 3 | C. | S  | C   | S      |

| 0100       | 4                                         | EOT | DC4 | \$ | 4 | D  | T  | d   | t      |

| 0101       | 5                                         | ENQ | NAK | %  | 5 | E  | U  | •   | u      |

| 0110       | 6                                         | ACK | SYN | &  | 6 | F  | ٧  | f   | V      |

| 0111       | 7                                         | BEL | ETB | ,  | 7 | G  | W  | g   | w      |

| 1000       | 8                                         | BS  | CAN | (  | 8 | Н  | X  | h   | X      |

| 1001       | 9                                         | HT  | EM  | )  | 9 | 1  | Y  | i   | У      |

| 1010       | Α                                         | LF  | SUB | *  |   | J  | Z  | j   | z      |

| 1011       | В                                         | VT  | ESC | +  | ; | K  | I. | k   | {      |

| 1100       | C                                         | FF  | FS  | ,  | < | L  | 1  |     | 1      |

| 1101       | D                                         | CR  | GS  | -  | = | M  | 1  | m   | }      |

| 1110       | E                                         | SO  | RS  |    | > | N  | ^  | n   | $\sim$ |

| 1111       | F                                         | SI  | US  | 1  | 3 | 0  |    | 0   | DEL    |

All characters in these two columns and SP (Space) are non-printing.

When UPPER CASE ONLY is used, shaded lower case characters (columns 6 & 7) from keyboard are converted to their upper case equivalents (columns 4 & 5) before being printed or transmitted.